Изобретение относится к автомат ке и вычислительной технике, в час ности к техническим средствам обучения и контроля знаний, и может б использовано для программированног кон1;роля знаний по различным дисци линам. Известно устройство, содержащее блок ввода ответов, элементы совпа дения, триггер состояния, регистр, ответа, блок управления прерываниям Коммутатор пультов, счетчик введен ных символов, шифратор начального раса, блок памяти, блок управления коммутатором пультов и вычислитель Недостатками такого устройства являются сложность формирования ад са, значительный объем памяти для хранения информации и низкая надеж ность передачи информации. Известно также устройство, соде жащее пульты учащихся, включающее последовательно соединенные блок в да ответов, триггер, блок совпадания и блок Пс1мяти ответов, вычисли тель, а также последовательно вклю ченные генератор, счетчик, дешифра тор и группу элементов ИЛИ С2. Это устройство позволяет сократить затраты на обрудование, однак его недостатком является значитель ное количество длинных линий связи снижающие надежность работы.устрой ства., Наиболее близким к изобретению является устройство, содержащее пул ты обучаемых, подключенные через, блок управления к электронной машин соединенной с одними входами блока памяти учебной информации, блок эле ментов ИЛИ, генератор, соединенный через последовательно включенные пульты учащихся с другими входами блока памяти и блока элементов ИЛИ СЗ . Устройство позволяет уменьшить количество линий связи между пультами и блоком.памяти, однако имеет низкую надежность передачи информации и ограниченные дидактические возможности.из-за блокировки узлов пульта обучаемого на мсмент считывания массива информации в блок- памяти. Кроме того, в устройстве слож процесс дешифрации ответа, так как за один цикл в одну ячейку памяти считываются символы ответа от всех пультов и для контроля полного ответа каждого обучаемого необходимо склеивать полный код ответа из ряда кодов символов, расположенных в разных ячейках памяти. Цель изобретения - расширение дидактических возможностей устройства с повышением надежности передачи информации и уменьшением числа линий свйзи. , . Поставленная цель достигается тем, что в устройство, содержащее последовательно включенные блок памяти, вычислитель, генератор тактовых импульсов, пульты обучаемых , коммутатор пультов и блок регистрации, введенных в первый счетчик и последовательно включенные элемент задержки, второй счетчик, первый блок элементов И и второй блок элементов И, выход которого соединен с первым входом блока памяти, второй и третий входы которого подключены соответственно к первому и второму выходам первого счетчика, вход которого соединен с выходом элемента задержки, а первый выход - с вторыми входами вычислителя и генератора тактовых импульсов, выход которого подключен ко вторым входам блока регистрации и коммутатора пультов, третий и четвертый входы блока регистрации соединены соответственно с выходом второго счетчика и вторым выходом первого блока элементов И, второй вход второго счетчика подключен ко второму выходу коммутатора пультов, пятый вход блока регистрации соединен с выходом элемента задержки, вход которого и четвертый вход блока памяти подключены к первому выходу перво го блока элементов И, второй вход второго блока элементов И соединен с выходом блока регистрации, причем коммутатор пультов содержит формирователь кодов, первый вход которого через последовательно включенные элементы ИЛИ соединен с первым входом коммутатора, второй вход - через сдвигающий регистр подключен ко второму входу коммутатора, выход формирователя кодов является первым выходом коммутатора, а второй выход сдвигающего регистра является вторым выходом коммутатора, а блок регистрации содержит последовательно включенные первый узел элементов И, третий счетчик, сумматор, узел элементов ИЛИ-НЕ, второй узел элементов И, регистр и третий узел элементов И, выход которого сЪединен со вторым входом третьего счетчика, выход которого является выходом блока, первый вход первого узла элементов И, второй вход сумматора и второй вход второго узла элементов И являются первым входом блока, третий вход второго узла элементов И и второй вход третьего узла элементов И являются вторым входом блока, четвертый вход второго узла элементов И и втррой вход первого узла элементов И являются соответственно третьим и четв.ертым входами блока, второй вход регистра и третий вход третьего счетчика являются пятым входом блока, третий вход третьего узла элементов И соединен с выходом сумматора.

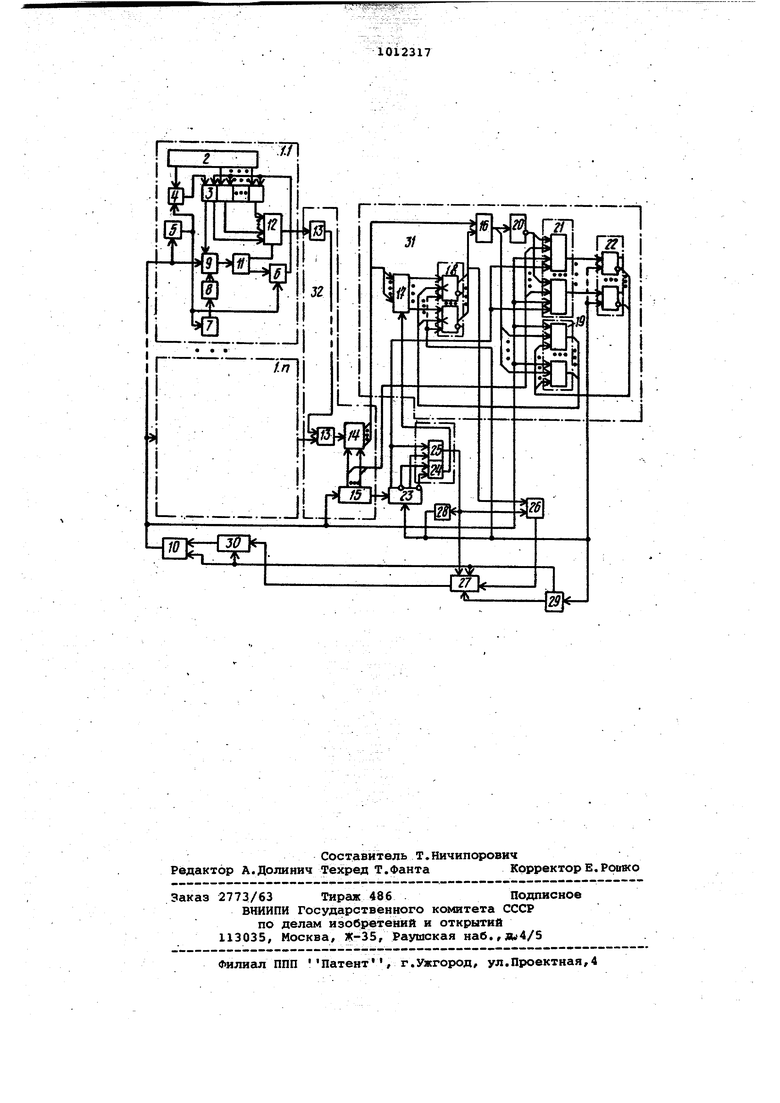

На чертеже представлена функцио;нальная схема устройства.

Устройст во для контроля знаний обучаемых содержит пульты обучаемого каждый из которых состоит из панели 2 ввода ответа, информационные выходы которой связаны с информационными входами регистра 3 ответа, а выход сигнала ТотовнЬсть соединен с первым входом элемента И 4, второй

1ВХОД которого подключен к выходу счетчика 5 серииимпульсов, подсоединенного, кроме того, этим же выходом к первому входу элемента И 6 и входу счетчика 7 тактов, выход которого связан со входом девшфра- . тора 8. Выход де1чифратора 8 подключен к первому входу элемента И 9, второй вход которого соединен с вы

Готовность

ходом разряда

регистра 3, а третий вход элемента И 9, 20 как и вход счетчика 5 связан с выходом генератора 10 тактовых им пульсов. Выход элемента И 9 соединен со входом счетчика 11, первый выход которого связан со вторым 25 входом элемента И б, выход которого соединен с управляющими входами регистра 3, а второй выход счетчика 11 связан с управляющим входом мультиплексора 12, информационные ,входы которого подключены к выходам регистра 3, а выход мультиплексора 12 является выходом пульта 1.

Выходы пультов 1 через последовательно включенные элементы ИЛИ .13 связаны с информационным входом формирователя 14 кодов, управляюие входы которого соединены с информационньЕли выходами сдвигающего регистра 15. вход которого подключен к выходу генератора 10. Выходы фор- 40 мироЁателя 14 связаны со входами сумматора 16 () и со входами узла 17 элементов И, выходы которого соединены со входами счетчика 18. Счетные входы триггеров счетчика 18 45 связаны с соответствующими выходамк блока 19 элементов И, а выходы подключены ко вторым входам сумматора 16, выходы которого соединены со входами узла 19 и со входами узла 20 Q элементов ИЛИ-НЕ, выходы которого подключены к одним входам узла 21 элементов И. Другие входы узла 21 связаны с информационными выходами регистра 15, а выходы - со входами „ регистра 22, инверсные выходы триггеров которого подключены ко входам блока 19. Входы блоков 19 и 21 Соединены со входом генератора 10. Управляйвшй выход регистра 15 подключен к счетному входу счетчика 23, ин- 60 версные выходы которого соединены со входами элемента И 24, выход которого подключен ко входу блока 17, а прямые выходы счетчика 23 соединены со заходами элемента И 25, выход 65

которого связан с;первыми входами блока 26 элементов И, вторыми входа- ми подключенного к выходам счетчика 18, с входом режима записи блока 27 памяти и со входом элемента 28 задержки. Выход элемента 28 соединен со входом счетчика 23, с входами счетчика 18, с входами регистра 22 и с входом счетчика 29 (адреса), выход которого соединен со входом генератора 10, с управляющим входом вtIчиcлитeля 30 и со входом режима считывания блока 27, выход которого связан с информс1ционным входом вычислителя 30, а другой выход счетчика 29 связан с управляющим входом блока 27, информационный вход которого подключен к выходу блока 26.

Сумматор 16, узел 17, счетчик 18, узлы 19, 20 и 21 и регистр 22 соединены в блок 31 регистрсщйи, элементы 13, формирователь 14 и регистр 15 - в коммутатор 32 пультов, а элементы 24 и 25 - в блок элементов И (позици на чертеже не указана).

Устройство работает следующим образом.

Вычислитель 30 запускает генерато 10, который формирует серии по С импульсов ( 1,к,где к - разрядность регистра ответа). Эта тактовая последовательность поступает на сдвиговый вход регистра 15, с помощью которого адресуется, соответствукнций элемент узла 21. С последовательного выхода регистра 15 импульс, после опроса всех к разрядов, .поступает навход регистра 15 (на чертеже связь не показана) и вход счетчика 23, управляющего считыванием информации с по мощью элемента 24 и занесением единицы в счетчик 29, адресующий очередную ячейку в блоке 27. Адрес ячейки равен номеру, оправшиваемого в данный момент 3-ро пульта 1, обучаемого. (Адрес изменяется после прохождения t-Зк импульсов, что обеспечивается регистром 15 и счетчиком 23). Тактовая серия генератора 10 поступает также в пульты 1, создавая условия для синхронного считывания и дешифрования элементов ответа -го обучаемого. Обучаемый вводит свой ответ с помощью панели 2 в регистр 3. Для сигнал1;зсщии об окончании работы над вопросом и считывания отззета обучаемьй формирует сигнал Готовность, поступающий в регистр 3 только в момент прохождения импульса тактовой серии с номером Зк, что обеспечивает счетчиком 5 и элементом 4. Запись сигнала готовности в регистр 3, происходит, таким образом, в строго фиксированные моменты времени, что обеспечивает считывание содержимого регистра 3 без потери информации. Каждое переполнение счетчика 5 (т.е. прохождение Зк импульсов) вызывает импульс на входе счетчика 7, где образуется номер опраииваемого в данный момент пульта 1 (равный номеру серии б). Дешифратор 8 настроен в каждом пульте на свое состоя ние, а именно, на код -номера данного пульта. При дешифрации заданного состояния (j) и наличии сигнала го товности (единичное состояние 1-го разряда регистра 3), через элемент И б разрешается опрос регистра 3. через мультиплексор 12 i-и разряд кода ответа выводится из -го пульт 1 и через ( -1) элементы ИЛИ 13 поступ.ает на информационный вход формирователя 14, в котором синхрон но коммутируется регистром 15 соот.ветствуюций i-и разряд в счетчике 18 через узел 17, так как с.четчик 2 находится в состоянии О до завершения первых к импульсов серии (.riK тактового генератора 10, и на в ходе элемента И 24 - . Таким образом, в триггеры счетчика 18 переписывается содержание ответа j-ro обучаемого. В процессе передачи информации по длинной связи, которой является информационная шина, из-за внешних причин возможен сбой. Для повьйпения надежности передачи этой информации используется 3-кратное считывание с текущим мажорированием (т.е. выделением повторяющего-: ся сигнала например 2 из 3-х). Эта -операция протекает следующим образом После прохождения первых к в серии С импульсов счетчик 11 переполняется и (к .-«-1)) импульс серии адресует в мультиплексоре 12 снова первый информации разряд регистра 13, а в первый разряд счетчика 23 в этот мо мент заносится , что запрещает запись информации в счетчик 18 (обеспечивается элементом 24) и разреша ет прохождение сигнала через узел 2 на регистр 22. Повторное считьшание ответа совмещено с операцией текущего мажоритарирования сигналов ответа в каждом разряде. Код i-го разряда ответа с формирователя 14 суммируется по той 2 на элементе сумматора 16. Если имеет место совпадение -i -го сигнала второго считывания и состояния i-ro разряда счетчика 18, то выходной сигнал с соответствующего элемента сумматора 16, инвертируемый элементом узла 20 поступает на -«-и элемент узла 21 (этот элемент выбирается также с регистра 15 и тактируатся генератором 10). В результате i-й триггер регистра 22 переходит в единичное состояние и снимаемый с его инверсного выхода сигнал запрещает прохождение импульса через элемент 19, т.е. запрещает изменение состояния 1-го разряда счетчика 18 до окончания всей операции, считывания ответа из j-го пульта 1, Таким образом, обеспечивается защита данного i-го разряда кода ответа от сбоя .при 3-м считывании. Если элемент узла 16 формирует единичный сигнал, что свидетельствует о наличии сбоя, то этот сигнал через открытый триггер регистра 22 и тактируемый генератором 10 i-й элемент узла 19 поступает на счетный вход - -триггера счетчика 18, переводя его в противоположное состояние. В последующем цикле (3-м) это состояние либо подтвердится, либо изменяется описаннкм.способом. В итоге на счетчике 18 зафиксируется код ответа с j-го пульта 1 обучаемого, критерием достоверности считывания которого является совпадение хотя бы двух из трех однотипных сигналов в каждом разряде. После прохождения серии импульсов счетчик 23 переходит в состря,ние 11. Это состояние счетчика 23 через элемент 25 обеспечивает режим записи информации в блок 27 папяти. Из счетчика 18 через блок 26 по адресу J/ находящемуся на счетчике 29, в блок 27 заносится откорректированный код ответа j-ro обучаемого. Тем же импульсом, задержаннь элементом 28 на время записи, счетчик записи, счетчик 23, счетчик 18, регистр 22 сбрасываются в О, а содержимое счетчика 29 увеличивается на единицу. Начинается опрос следующего -( j +1)-го пульта 1. После опроса всех и пультов 1 обучаемых счетчик 29 переполняется и устанавjraaaeT режим считывания информации из блока 27 в вычислитель 30 и обеспечивается останов генератора 10 После считывания и обработки учебной информации -/сравнение с эталоном, проверка правильности этапа доказательства или решения задачи и т.д.) вычислители) 30 вновь запускает генератор 10 и опрос пультов 1 продолжается до вьтолнения ими всей контролируквдей программы. Таким образом, устройство для контроля знаний Обучаемых позволяет контролировать ответ с высокой степенью надежности, обеспечивающейся защитной от слз айных сбоев в длинной линии и реализацией гарантованного считывания всего, содержимого регистра ответа. Устройство отличается от известных упрощением конструкции за счет сокращения линий связи.

JL 17{Мгй WiSlES

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированный класс для контроля знаний обучаемых | 1981 |

|

SU963065A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1483479A1 |

| Автоматизированный класс для контроля знаний обучаемых | 1984 |

|

SU1196938A1 |

| Устройство для обучения | 1983 |

|

SU1273974A1 |

| Обучающее устройство | 1980 |

|

SU875434A1 |

| Многопультовый тренажер операторов систем управления | 1981 |

|

SU953651A1 |

| Устройство для обучения и контроля знаний обучаемых | 1980 |

|

SU936009A1 |

| Устройство для обучения | 1980 |

|

SU985814A1 |

| Пульт преподавателя для обучающих устройств | 1984 |

|

SU1166163A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU985811A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗНАНИЙ, ОБУЧАЕМШ, содержащее последовательно включенные блок памяти, вычислитель, генератор тактовых импульсов, пульты обучаемых, коммутатор пультов и блок регистрации, о т л ичающееся тем, что, с целью расширения дидактических возможностей устройства, в него введены первый счетчик и последовательно включенные элемент задержки, второй счетчик, первый блок элементов И и второй блок элементов и, выход которого соединен с первым входом блока памяти, второй и третий входы которого подключены соответственно к первому и второму выходам первого счетчика, вход которого соединен с выходом элемента задержки, а первый .выход - со вторыми входами вычислителя и генератора тактовых импульсов, выход которого подключен ко вторьмвходам блока регистрации и кс 1мутатрра пультов, третий и четвертый входы блока регистрации соединены соответственно с выходся 4 второго счетчика и вторым выходом первого блока эло 1ентов И, второй вход второго счетчика подк.гаочен к второму выходу ксмлмутатора пультов, пятый вход блока регистрации соединен с выходом элемента задержки, вход которого и четвертый вход блока пшяти подключены к первому выходу первого блока элементов И, второй вход второго блока элементов И соединен с выходом блока регистрации. 2.Устройство по П.1, о т л и чающеес я тем, что в нем коммутатор пультрв содержит формирователь кодов, первый вход которого через последовательно вкяючеиные элементы ИЛИ соединен с первсш входом ксжлмутатора, второй вход через сдвигающий регистр подключен к6 второму входу коммутатора, выход Фо я 1ирователя кодов является первьм выходе коммутатора, а второй .выход сдвигаюцего регистра является вторым выходсяч коммутатода. 3.Устройство по П.1, ОТЛИЧЭ ю щ е е с я ем, что в нем блок регистрации содержит последовательно включенныег первый уз элементов И, третий счетчик, сумматор, узел элементов ИЛИ-НЕ, второй узел элементов И,регистр и третий узел элементов И, выход которого соединен со вторым входом третьего счетчика, ts9 выход которого является выходом блоОб ка , первый вход первого, узла элементов и, второй вхоц сумматора и вторрй вход второго узла элементов И являются первым аходом блока, третий вход узла элементов И и второй вход третьего узла элементов И являются вторым входом блока, четвертый вход второго узла элементов И и второй вход первого узла элементов И являются соответственно третьим и четвертым входами блока, второй вход регистра и третий вход третьего счетчика являются пятьох входом блока, третий вход третьего узла элементов И соединен с выходом сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Автоматизированный класс для контроля знаний учащихся | 1977 |

|

SU734794A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-04-15—Публикация

1981-12-08—Подача