(54) УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ Изобретение относится к автоматгмКбг и вычислительной технике, в частности к устройствам и системам для группового обучения и контроля знаний, и может быть использовано для программированного обу чения и контроля знаний в учебных заведени$1х по различным дисциплинам. Известно устройство, содержащее пуль ты учащихся, соединенные через коммутаторы пультов и блоки приоритета с СОО-Рветствующими блоками оперативной памя тя, которые через коммутатор блоков памяти, подключены к блоку буферной памяти ш.: Недостатком устройства являются боль ише затраты оборудования. Известно также устройство, содержа. шее пульты учащихся, блок приоритета, коммутатор пультов, блоки буферной пакшти, блоки совпадения, дешифратор и рас ределители С 2 . Недостатком данного устройства являются ограниченные дидактические возможности и большие аппаратурные затраты. Наиболее близким к предлагаемомуявляется устройство, содержащее пультй учащихся, соединенные с соответствук щими блоками приоритета и коммутаторами, которые подключены к соотъетствук щим блокам оперативной памяти, соединенные с коммутатором блокор памяти, который подключен непосредственно к блокам буферной памяти СЗ , Устройство позволяет получать справки по изучаемому курсу, однако имеет ограниченные дидактичес1 ие возможности из-за отсутствия режима автоматизированной консультации. Цель изобретения - расширение дидакгаческих возможностей устройства за счет автоматизированной консудьтаюш по неусвоенным участкам курса. Указанная цель достигается тем, что в известное устройство, содержащее последсшатепьно включенные коммутатор пультов, пульты обучаемых, блок приоритета.

блок анализа запросов и первый блок памяти, второй вход блока приоритета соединен с вторым выходом блока анализа запросов, а второй выход - с вторыми выходами пультов обучаемых, бведены последоватрпьно включенные первый распределитель кодов и второй блок памяти, выход которого соединен с первым входом коммутатора пультов, второй распределитель кодов, первый вход которого подключен к первому выходу первого блока памяти, а выход - к третьим входам пультов обучавмых, и последовательно включенные генератор тактовых импульсов, блок задания времени, блок управления считъшанием, третий блок памяти, первый блок элементов И и второй блок элементов И, второй вход которого соединен с вторым выходом третьего блока памяти, а выход - с вторым входом блока управления считьтанием третий вход которого подключен к выходу генератора тактовых импульсов, а второй выход - к второму входу второго распределителя кодов, вход первого распределигеля кодов соединен с вторыми выходами пультов обучаемых, а второй вьгход - с вторым входом коммутатора пультов, выход генератора тактовых импульсов соединен с третьим входомблока приоритета и с вторым входом первого блока памяти, третий и четвертый входы которого подключены к третьему и четвертому выходам блока управления считьтанием соответственно, второй вь1ход - к второму входу первого блока элементов И, а третий выход - к второму входу блока анализа запросов, второй и третий входы третьего блока памяти соединены соответственно с первым и третьим выходами блока приоритета, причем блок управления считьюанием содержит последовательно соединенные дешифратор, первый регистр, первый элемент И, первый триггер и второй элемент И, второй вход и выход которого являются соответственно третьим входом и чет вертым выходом блока, второй вход и выход триггера являются соответственно первым входом и третьим выходом блока, выход первого элемента И является первым .выходом блока и соединен с вторым входом первого регистра, выход и вход дешифратора являются соответственно вторыми выходом и входом блока, блок анализа запросов содержит первый узел элементов И, первый вход и выход которого являются соответственно первыми входом и выходом блока, и последовательно соединенные второй регистр, первый коммутатор, .второй узел элементов И и первый

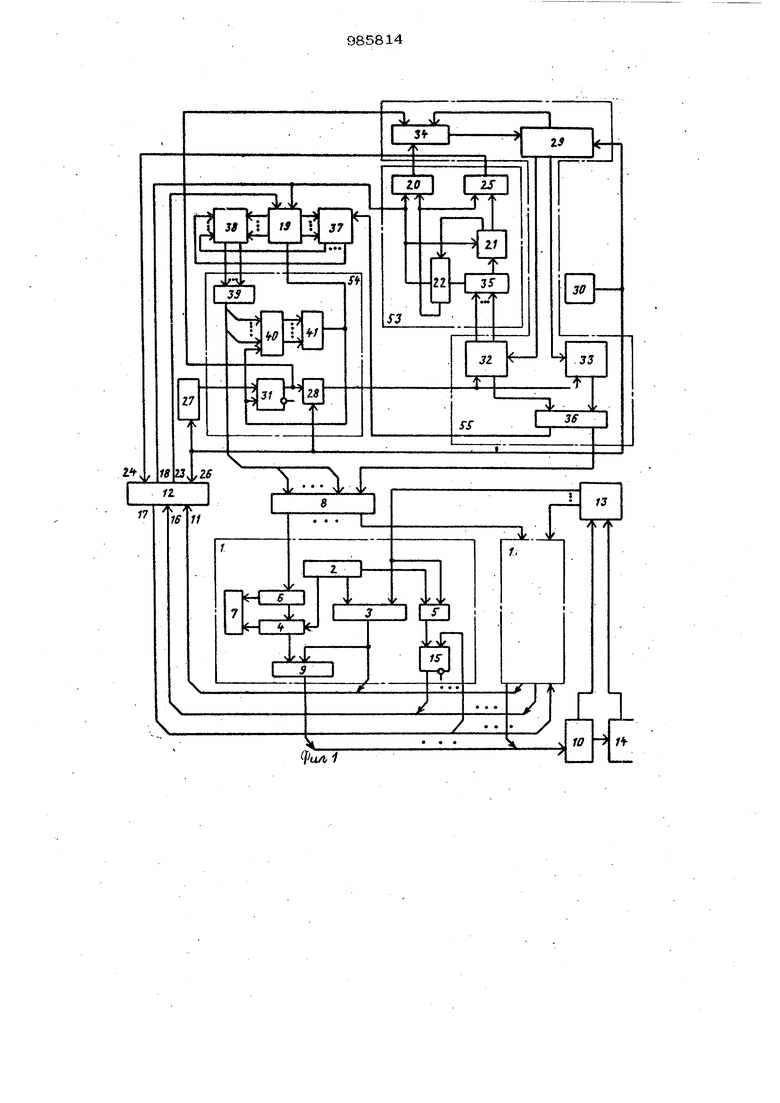

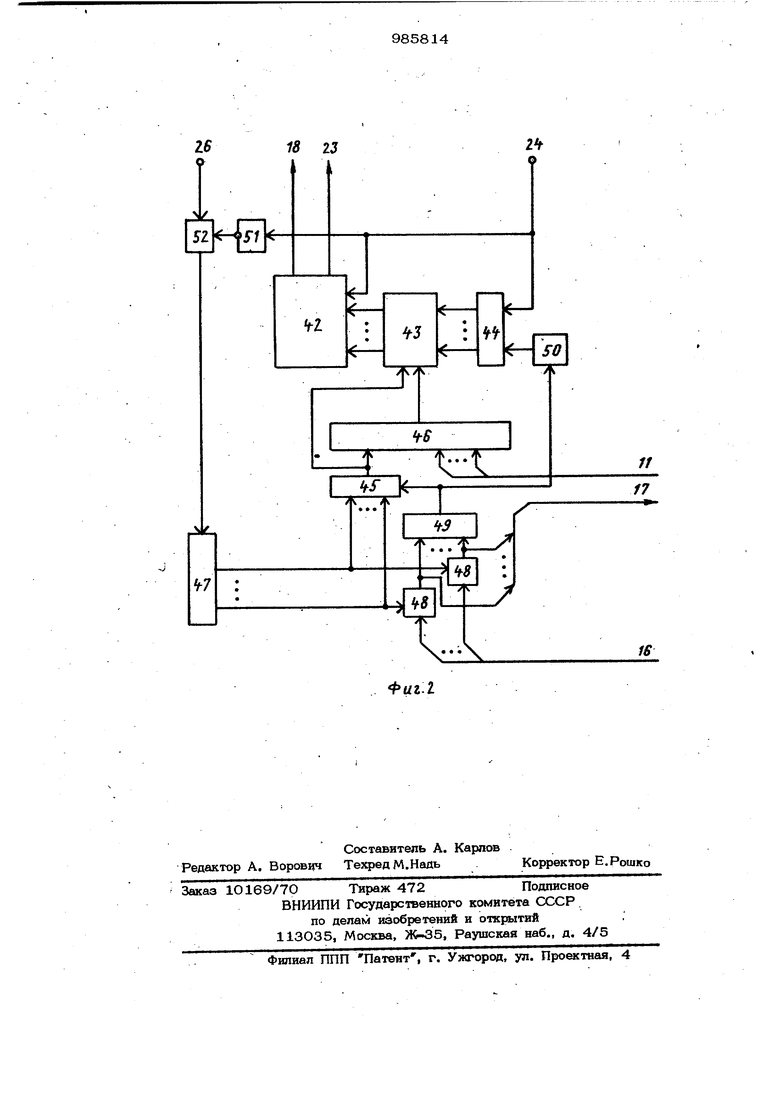

элемент ИЛИ, выход которого является вторым выходом блока, а второй вход подключен к второму выходу второго регистра, соединенному с вторым входом первого узла элементов И, пепвый вход второго регистра соединен с вторым выходом второго узла элементов И, вторые входы второго регистра и второго узла элементов И являются первым входом блока, а второй вход первого коммутатора вторым входом блока, а блок приоритета содержит последовательно соединенные инвертор, третий элемент И, счетчик, элементы И группы, второй элемент ИЛИ, третий узел элементов И, второй коммутатор, третий коммутатор и первый узел памяти, первый и второй выходы и второй вход которого являются соответственно первым и третьим выходами и вторым входом блока, и последовательно включенные элёмент задержки и третий регистр, выход которого соединен с вторым входом третьего коммутатора, а второй вход является вторым входом блока, вход элемента задержки соединен с выходом второго элемента ИЛИ, второй вход третьего узла элементов И соединен с выходом счетчика, вторые выходы и выходы элементов . И группы являются соответственно первым входом и вторым выходом блока, второй вход второго коммутатора является первым входом блока, выход третьего узла элементов И подключен к -третьему входу третьего коммутатора. Не фиг. 1 изображено устройство, общая структура; на фиг. 2 - структура блока приоритета. Устройство для обучения состоит из пультов 1 обучаемого, содержащих узел 2 ввода ответов, подключенный к регистру 3, узлу. 4 сравнения и элементу ИЛИ 5, причем узел 4 и узел 6 памяти подсоединен к узлу 7 индикации, а узел 6 другим выходом соединен с узлом 4, а входом - с распределителем 8 кодов. Выходы регистра 3 и .узла 4 через узел элементов И 9 подключены к распределителю 10 кодов, кроме того выход регистра 8 связан с входом 11 блока 12 приоритета, а входы регистра 3 и элемента ИЛИ. 5 подсоединены к соответствующему выходу коммутатора 13 пультов, подсоединенного к выходам распределителя Ю и блока 14 памяти (связей), подключенному к другому выходу распределиаеля 10. Выход элемента 5 связан с единичным входом триггера 15, выход кото59858146

рого соединен с входом 16 блока 12, аи элемент 41 - в блок 54 управления

нулевой вход - с выходом 17 блока 12.считыванием информации, а накопнтели29, .

Выход 18 блока 12 подключен к блоку 1932, 33 и 34 и регистр 36 - в блок 55

памяти (запросов), узлу 20 элементов И,памяти.

узлу 21 элементов И и входу сброса ре- $ Блок 19 хранит номер пульта и код пистра 22, а третий выход 23 блока 12-признака запроса (или номер понятия). к блоку 19. Вход 24 блока 12 подсоеди-Накопитель 34 предназначен для запоминен через элемент ИЛИ 25 к выходам ре-нания признаков информации (или номер гистра 22 и узла 21, а вход 26 блокапонятий), отсутствукицих на момент зап12, и входы блока 27 задания времени, Юроса в накопителе 33, и организован в элемента И 28 и накопителя 29 (памятивиде стека. Накопитель 29 содержит в понятий) связаны с генератором 30 так-своих ячейках учебную информацию, потовых импульсов. Выход блока 27 подклю-деленную на понятия. В накопителе 33 чен к единичному входу триггера 31, вы-хранится учебная информация, раскрываюход которого подсоединен к элементу И 15щая содержание понятий курса, номера 28, связанному с накопителями 32 ,и 33(или признаки) которых записаны в соот. буферной памяти и накопителем 34 опера-ветствуюших ячейках накопителя 32. Ретивной памяти, подключенным к узлу 2Огистр 22 состоит из признаковой и miи связанному двусторонней связью с на-формационной частей. В блоке 14 содер- копителем 29, первым выходом соединен-20жатся номера понятий, предшествующие и ным с накопителем 32i подключенным че-связанные по смыслу с понятием, номер рез коммутатор 35, связанный с регист которого соогветствуаг номеру ячейки ром 22, к узлу 21, а вторым выходом-где записана эта информация с накопителем 33, причем выходы нако-Предлагаемое устройство для обучения пителей 32 и 33 подсоединены к регкст 25работает следующим образом, ру 36, один выход которого связан с

распределителем 8, а другой - с блокомПосле включения питания генератор 30 37 элементов И, другими входами свя-формирует на своем выходе последовательзанным с блоком 19, а выходами - с бло-ность тактовых импульсов, поступающую ком 38 элементов И, также подсоединен- зо связанные с ним блоки. Обучаемые ным к блоку 19, а выходами через де-с помощью узла 2 вводят номера понятий шифратор 39 - к распределителю 8 и ре-(или признаки), которые должны ими изугистру 40, выходь которого подключенычаться. Код поступает в регистр 3, а через элемент И 41 к блоку 19, нулево-после окончания ввода обучаемый формиму входу триггера 31 и входу сброса ре-,РУет сигнал Готовность., переводящий в гистра 4б. Блок 12 приоритета содержитединичное состояние через элемент 5 тригузел 42 памяти, выходы которого являют-гер 15. Блок 12 приоритета с помощью ся выходами 18 и 23 блока 12, первыйэлемента И 52, счетчика 47 и группы вход, подсоединен через коммутатор 43,элементов И 48 опрашивает на-входе 16 подсоединенный к регистру 44 и узлу 45 шину Готовности пультов 1. Если готовэлементов И, к коммутатору 46, подсо-ность обнаружена, то через элемент ИЛИ единенному к входу 11 и узлу 45, входы49 разрешается поступление адреса пулькоторого являются выходами счетчика 47,та 1 со счетчика 47 через узел 45 на связанного этими же выходами с первымикоммутатор 46. В результате коммутатор входами группы элементов И 48, другие46 подключает на свой выход ту линию входы которых связаны с входом 16 бло-входа 1-1, по которой в данный момент ка 12, а выходы подключены к вь1ходу 17передается код запроса ,с выбранного реблока 12, через элемент ИЛИ 49 подсо-гистра 3. На коммутатор 43, таким обраединены к узлу 45 и через элемент 5Озом, поступает код запроса и номер пульзадержки - к регистру 44, другой входта (или его адрес). Эта информашш под которого, как и второй вход узла 42 иуправлением регистра 44 заносится в инвертора 51, подключены к входу 24узел 42, причем в первую свободную ячей- блока 12. Вход 26 через элемент И 52,ку (на которую указывает единица в соот подключенный к элементу 51, связан советствующем разряде регистра 44). За- счетным входом счетчика 47.держанный элементом 50 сигнал с элёмен-

Узел 20, регистр 22, узел 21, эле- ИЛИ 49 сдвигает единицу регистра

мент 25 и коммутатор 35 объединены в44 на один разряд, номер которого COOTW

блок 53 анализа запроса, триггер 31,ветствует новой свободной ячейке, узла 42.

элемент 28, деши(}ратор 39, регистр 4ОТаким образом, блок 12 фиксирует запро79858сы по мере их поступления. Через заданное блоком 27 время с него снимается сигнал, переводящий триггер 31 в блоке 54 в состояние, разрешающее считьгоание ;-информации из блока 12 и передачу ее в 5 соответствующие узлы устройства. Код первого запроса из узла 42 блока 12 поступает с выходов 18 и 23 в блок 19, а его часть, содержащая только номер понягая (с выхода 18) - в блок 53 анализа О запроса. В блоке 53 появление кода приводит к сбросу в начальное состояние регистра 22, адресующего с помощью коммутатора 35 первую ячейку накопителя 32, где записаны номера понятий, находящиеся15 в этот момент JB накопителе 33. Узел 21 производит сравнение и в случае совпадения кодов посылает сигнал через элемент 25 в блок 12 для вьщачи следующего запроса. Этот сигнал по входу 24 блокирует 20 вход 26 (С помощью элементов 51 и 52) и поступает-на входы узла 42 и регистра 44. Информация в узле 42 и единица 44 сдвигаются в противоположном, чем при .записи, направлении.25 Если же узлом 21 не обнаружено совпадение с содержимым данной ячейки накоЛителя 32, то сигнал неравенства поступает на сдвигающий вход регистра 22 н зо коммутируется. новая ячейка. Если заданное понятие содержится в накопителе 33, ТО с оследовательного выхода регистра 22 снимается сигнал, поступающий через элемент 25 в блок 12 и разрещающий запись номера понятия через узел 2О в накопитель 34. Из накопителя 34 номера понятий поступают-, одновременно с тактом от генератора 56 в накопитель 29, и на освобождающееся место в накопителях 32 (номера понятий) и 33 (содержание понятия) записьюается новая информация. Новый адрес из накопителя 34 поступает с появлением на специальном выходе накопителя 29 (маркера), что говорит о полном считъюании информахши по данному понятию. Одновременно с записью информации в накопителях 32 и 33 под действием тактовых импульсов, поступающих через элемент И 28, идет считьшание понятий в регистр 36. Адресная (или признаковая) часть информации сравнивается в блоке 37 с номерами понятий, поступивщими в качестве запросов. Совпавщие ячейки коммутируют в блоке 38 соофветствующие напряжения и адреса пультов из блока 19, заказавших данное понятие, поступают через дешифратор 39 на pacпpeдeлйteriь 8. В результате информа48ДИЯ о понятии через распределитель 8 с регистра 36 записьшается в узел 6 памяти соответствующего пульта 1 (или пультов). Одновременно сигнал с деши4 ратора 39 переводит соответствукшшй разряд регистра 40 в единичное состояние. При считьтании информации в последний пульт с элемента 41 снимается сиг нал, переводящий триггер 31, блок 19 и регистр 40 в начальное состояние, Поступающая в узел 6 информация анализируется обучаемым, который отвечает с помощью узла 2 на контрольный вопрос, проверяемый в узле 4. При правильном ответе устройство ожидает очередного запроса, а при неправильном код запроса поступает через распределитель 10 в блок 14, где новый номер понятия из цепочки связи, а именно номер консультационного понятия, принудительно записьшается че- рез коммутатор 13 в регистр 3 данного пульта 1 и восстанавливает через эле- . мент ИЛИ 5 сигнал .Готовность на триггере 15. Происходит поиск новой информации н описанные выще операции повторяются. . Предлагаемое устройство позволяет расщирить дидактические возможности благодаря введению режима автоматизированной консультации, обеспечиваклдей повторную и всестороннюю проработку неусвоенного материала, что, может совмещаться с изучением разделов курса. При этом, устройство использует в качестве основного источника информации только два буферных блока памяти, по сравнению с несколькими в известных устройствах. Формула изобретения 1. Устройство для обучения, содержащее последовательно включенные коммутатор пультов, пульты обучаемых, блок приоритета, блок анализа запросов н первый блок памяти, второй вход блока приоритета соединен с BTOfanvi выходом блока анализа запросов, а второй выход - с вто рыми выходами пультов обучаемых, отличающееся тем, что, с целью расширения дидактическ1Ьс возможностей устройства, в него введены последсжательно включенные первый распределитель Кодов и второй блок йамяти, выход которого соединен с первым входом коммутатора пультов, второй распределитель кодов, первый вход которого подключен к первому выходу первого блока памяти, а выход -к

третьим входам пупьтов обучаемых, и последовательно включенные генератор тактовых импульсов, блок задания времени, блок управления считьтанием, третий блок памяти, первый блок элементов И и второ блок элементов И, второй вход которого соединен с вторым выходом третьего блока памяти, а выход - с вторым входом блока управления считьюанием, третий . вход которого подключен к выходу генератора тактовых импульсов, а второй выход к второму входу второго распределителя кодов, вход первого распределителя кодов соединен с вторыми выходами пультов обучаемых, а второй выход - с вторым входом коммутатора пультов, выход генератора тактовых импульсов соединен с третьим входом блока приоритета и с вторым входом первого блока памяти, третий и четвертый входы которого подключены к третьему и четвертому выходам блока управления считъшанием соответственно, второй выход - к второму входу первого блсжа элементов И, а третий выход - к второму входу блока анализа запросов, второй и третий входы третг рго блока памяти соединены соответственно с першам и третьим выходами блока приоритета/

2. Устройство по п. 1, о т л и ч а io ш е е с я тем, что в нем блок управлення считьтанием содержит последовательно соединенные дешифратор, первый регистр, первый элемент И, первый триггер и второй элемент И, второй вход и выход которого являются соответственно третьим входом и четвертым выходом ; - блока, второй вход и выход триггера являются соответственно первым входом и третьим выходом блока, выход первого элемента И является первым выходом бл& ка и соединен с вторым входом первого регистра, вход и выход детнифратора являются соответственно вторыми выходом и входом блока.

3. Устройство по п. 1, о т л и ч а ,ю ш е е с я тем, что в нем блок анализа запросов содеряшт первый узел эЛe ментов И, первый вход и выход которого являются соответственно первыми вхо- .

floM и выходом блока, и последовательно .соединенные второй регистр, первый коммутатор, второй узел элементов И и первый элемент ИЛИ, выход которого является вторьЫ выходом блока, а второй вхо подключен к второму гаыходу второго ре;гистра, соединенному с вторым входом первого узла 9лемент ж И, первый вход второго регистра соединен с вторым вьн ходом BTOJmro узла эп 4ентов И, вторые входы регистра и второго узла элементов И являются первым входом блока, а второй вход первого коммутатора вторым входом блока.

4. Устройство по п. 1, о т л и ч а - ю щ е е с я тем, что в нем блок приоритета содерзмйт последовательно соеди- ненные инвертор, третий элемент И, счетчик, элемент И группы, второй элемент ИЛИ, третий узел элементов И, второй коммутатор, третий коммутатор и первый узел памяти, первиоК и второй выходы и второй вход которого являются соответс венно первым и третьим выходами вторым входом блока, и последовательно включенные элемент задержки в третий регистр, выход которого соединен с вторым входом третьего коммутатора, а второй вход является вторым входом блока, вход элемента задержки соединен с выходом второго элемента ИЛИ, второй вход третьего узйа элементов И соединен с выходом счетчика, вторые входы и выходы элементов И группы являются соответственно первым входом в вторым В1 ходом 6iioKa, второй вход второго коммутатора гжвляется первым входом блока, выход третьего узла элементов И подключен к третьему входу третьего коммутатора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР N9 656098, кл. Gi О9 В 7/07. 1977,

2.Авторское свидетельство СССР № бОИЗЭ, кл. G 09 В 7/07, 1976.

3.Авторское свидетельство СССР МЬ 731453, кл. G09 В 7/ОО, 1980 (прототип).

tГ

гУ

-

2

39

N

fZ

22

LT

fS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1976 |

|

SU601739A1 |

| Обучающее устройство | 1979 |

|

SU860113A1 |

| Обучающее устройство | 1981 |

|

SU974394A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU982063A1 |

| Обучающее устройство | 1979 |

|

SU860114A1 |

| Устройство для обучения и контроля знаний обучаемых | 1980 |

|

SU936009A1 |

| Устройство для обучения | 1981 |

|

SU985813A1 |

| Обучающее устройство | 1979 |

|

SU842924A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU976469A1 |

| ТРЕНАЖЕР КОЛЛЕКТИВА ОПЕРАТОРОВ СИСТЕМЫ УПРАВЛЕНИЯ | 1998 |

|

RU2176108C2 |

2

1823,

2

ил1

1618 2J

о

LS

17

/V Ik

I . .,

.

16

Фиг.1

Авторы

Даты

1982-12-30—Публикация

1980-12-05—Подача