(5) АВТОМАТИЗИРОВАННЫЙ КЛАСС ДЛЯ КОНТРОЛЯ ЗНАНИЙ ОБУЧАЕМЫХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированный класс для контроля знаний обучаемых | 1984 |

|

SU1196938A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU1012317A1 |

| Обучающее устройство | 1980 |

|

SU875434A1 |

| Устройство для контроля знаний обучаемых | 1979 |

|

SU851450A1 |

| Автоматизированный класс для контроля знаний учащихся | 1977 |

|

SU734794A1 |

| Устройство для контроля знаний учащихся | 1978 |

|

SU742446A1 |

| Автоматизированный класс для обученияи КОНТРОля зНАНий ОбучАЕМыХ | 1979 |

|

SU836650A1 |

| Автоматизированный класс для контроля знаний учащихся | 1978 |

|

SU771700A1 |

| Автоматизированный класс для контроля знаний | 1982 |

|

SU1035634A1 |

| Устройство для обучения | 1983 |

|

SU1273974A1 |

1

Изобретение относится к автоматике и вычислительной технике, в частности к области обучающих систем, построенных на базе вычислительных машин, и предназначено для контроля , знаний обучаемых в различных учебных заведениях.

Известен автоматизированный класс, содержащий пульты учащихся, подключенные через блок управления к элек- Q тронной вычислительной машине, блок памяти учебной информации, блок элементов ИЛИ, генератор l .

Недостатком класса является низ- i кое быстродействие и отсутствие пред- 15 варительной обработки информации, что снижает эффективность контроля знаний.

Известен также автоматизированный, класс, содержащий пульты учащих- 20 ся, соединенные через коммутатор пультов с блоком памяти и через блок управления прерываниями с электронной вычислительной машиной, блок

управления коммутатором, счетчик .введенных символов, шифратор начального адреса {,2.

Недостатком данного класса является сложность узлов управления и низкая эф1)ективность контроля знаний,

Наиболее близким к предлагаемому является автоматизированный класс, содержащий пульты учащихся, вычислитель и последова.тально включенные генератор, счетчик и дешифратор, а также блоки совпадения, элементы ИЛИ и группу элементов ИЛИ 3.

Автоматизированный класс выполняет контроль знаний и обладает простой структурой, однако отсутствие предварительной обработки информации, а именно сортировки по вариантам контрольных знаний, а также неуправляемые прерывания вычислителя, снижают эффективность npoL(ecca контроля знаний.

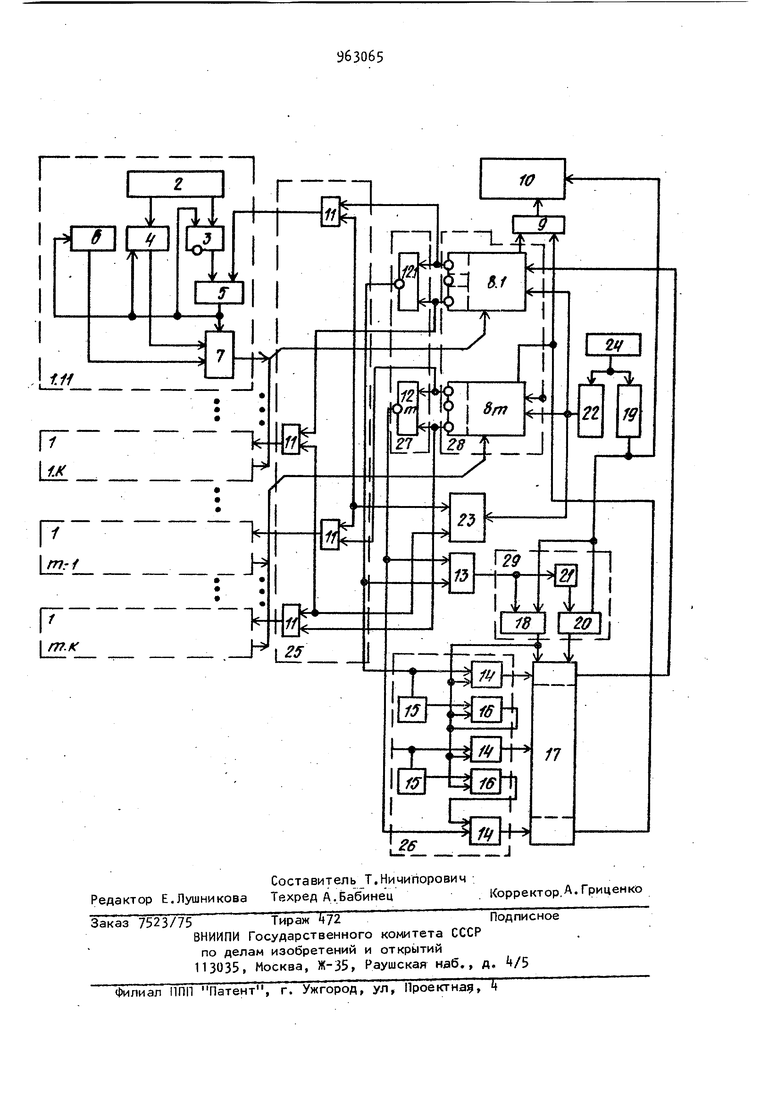

Цель йзбрётения - повышение точности контроля. Поставленная цель достигается тем, что в автоматизированный класс, содержащий последовательно включенные генератор, счетчик, дешифратор, блок элементов И и пульты обучаемых, а также вычислитель, введены последовательно соединеннее блок буферной памяти, блок элементов ИЛИ-НЕ, распределитель импульсов и регистр) опроса, два элемента ИЛИ, счетчик времени и формирователь импульсов, первый вход которого соединен через один из элементов ИЛИ с выходам блока элементов ИЛИ-НЕ, второй вход через счетчик времени - с выходом генератора, один выход непосредственно - со вторым входом распределителя импульсов и с вторым входом регистра опроса, а другой выход непосредственно с третьим входом регист- 2о ра опроса, выход которого подключен к первому входу блока буферной памяти, второй вход которого соединен с выходом счетчика, третий вход - с выходами пультов обучаемых, первый выход - с вторым входом блока элементов И, а второй выход с входом другого элемента ИЛИ, выход о которого подключен к первому входу вычислителя, второй вход которого cpa Динен с выходом счетчика времени. На чертеже представлена структурная схема предлагаемого автоматизированного класса. Автоматизированный класс для контроля знаний обучаемых содержит пульты 1 обучаемых, состоящие из блока 2 ввода ответов, подключенных к единичному входу триггера 3 и регистру ответа, причем выход триггера 3 подключен к первому входу элемента 5 И, выход которого связан с установочным входом регистра k, входом счетчика 6 вопросов и блоком 7 элементов И, к другим входам которого подсоединены выходы регистра k и счетчика 6, а выход блока 7, являющийся выход дом пульта 1, подключен через информационную шину к входу соответствующего блока 8 буферной памяти, выходы которых через элемент 9 ИЛИ связаны с информационной шиной вычислителя 10, Инверсные выходы маркерных разрядов ячеек блоков 8 .подсоединены через элементы 11 И к соответствующим входам пультов 1, являющихся вторыми входами элементов 5 И, кроме то92S 4 го, выходы каждого из блоков 8 подсоединены к соответствующему элементу 12 ИЛИ-НЕ, выходы которых подключены к входам элемента 13 ИЛИ и к соответствующему элементу I И, а через инвертор 15 к соответствующему элементу 16 И, Выход каждого из элементов И связан с установочным входом соответствующего разряда регистра 17.опроса, а выход каждого из (т-1) элементов 16 подключен к входам двух последующих элементов 1 и 1б в цепочке, причем первые в этой цепочке элементы 14 и 16, как и вход регистра 17 сброса связаны через элемент 18, И с выходами элемента 13 и счетчика 19 времени. Сдвиговый вход регистра 17 подключен через элемент 20 И к счетчику 19 и через инвертор 21 к выходу элемента 13. Выходы каждого из m разрядов регистра 17 подсоединены к управляющей шине соответст1зующего блока 8, адресные шины которых подсоединены к счетчику 22, связанному этим же выходом с дешифратором 23, каждый из k выходов которого подключен к входам m соответствующих элементов 11. Входы счетчика 22 и счетчика 19 подключены к генератору 2, а выход счетчика 19 связан с шиной прерывания вычислителя 10. Элементы И 11 объединены в блок 25 элементов И, элементы И k, инвертор 15 и элементы И 1б - в распределитель 26 импульсов, элементы ИЛИНЕ 12 - в блок 27 элементов ИЛИ-НЕ, блоки 8 - в блок 28 буферной памяти, а элементы 18-21 - в формирователь 29 импульсов. Учебные контрольные задания состоят из вопросов, предполагающих ответ, кодируемый цифрами. Информация о правильных ответах по всем m вариантам и программа проверки ответов обучаемых вводится в вычислитель 10. Автоматизированный класс для контроля знаний обучаемых работает следующим образом. По команде с вычислителя 10 запускается генератор 24, импульсы которого поступают на счетчики 19 и 22. Счетчик 19 начинает отсчитывать время, до первого прерывания вычислителя 10, для считывания информации из одного из блоков 8. Каждый i-ый блок 8 подключен к выходам пультов 1, предназначенных для выполнения 1-го варианта контрольного задания. Счетчик 22 формирует иа своем выходе адрес очередного i-ro пульта 1, который одинаково во всех m вариантах. Таким образом, в каждый такт генератора 2 опрашивается m пультов, что обеспечиваетсяедешифратором 2k, элементами 11 и 5, которые подключаются к своему блоку 8, в каждом из которых в данный момент скрммутирована ячейка, соответствующая номеру пульта 1. Обучаемый с помощью блока 22 вво дит код ответа, записывающийся в ре гистр k. После завершения этой oneрации обучаемый взводит триггер 3, разрешая тем самым опрос данного пульта 1. Сигнал опроса формируется в том случае, если на управляющей шине соответствующее го блока 8 установлен нулевой потенциал (от ре гистра 17) и ячейка, номер которой соответствует опрашиваемому пульту, свободна. Последнее означает, что с инверсного выхода маркерного разряда этой ячейки должен быть снят единичный потенциал. Если приведенные выше условия выполнены, то соответствующий элемент 11 открывается и опрашивается с помощью элемента 5 состояние триггера 3. Если три гер 3 в единичном состоянии, то открывается блок 7, через который содержимое регистра i и счетчика 6 поступает по информационной шине в заданную ячейку соответствующего блока 8. Кроме того, сигнал с выхо: да элемента 5 устанавливает триггер и регистр k в нулевое состояние, а счетчик 6 переводит в следующее сое тояние (первоначально в нем уставливается код единицы), определяющее код номера вопроса, на который будет формироваться ответ. Прерывание вычислителя 10 для считывания с одного из блоков 8, записанной, в них информации, может про изводиться как по сигналу счетчика 19, так и по полному заполнению одного из блоков В. В первом случае, сигнал с выхода счетчика 19 при отсутствии запрета, снимаемого с инвер тора 21 и означающего наличие хотя бы одного заполненного блока 8, через, элемент 20 сдвигает записанную в регистре 17 единицу на один разряд, чем обеспечивается подключение к информационной шине вычислителя 10 очередного блока 8, содержимое ко 56 торого считывается в вычислитель 10, при одновременной записи информации из пультов 1 во все остальные ,блоки 8. Если же на выходе элемента 13 единичный потенциал, что свидетельствует о наличии заполненного блока 8, то очередной импульс прерывания с счетчика 19 сбрасывает через элемент 18 регистр 17 и обеспечивает занесение с помощью цепочки элемент И 14, fiHBepTop t5 и элемент ,И 1б единицы в регистр ,17. Единица заносится в, разряд регистра 17, соответствующий номеру элемента 12 ИЛИ-НЕ, с которого снят единичный потенциал. Это означает, что в данном блоке 8 все маркерные разряды в единичном состоянии. Работа класса продолжается до момента остановки генератора24 командой с вычислителя 10, формируемой либо повыполнению всех заданий, либо по истечению времени, отведенного на занятие. Автоматизированный класс для контроля знаний обучаемых позволяет повысить эффективность контр оля знаний за счет предварительной сортиров- ки ответов по вариантам, что позволяет обрабатывать быстрее информацию вычислителем по прерыванию, согласно которого вызывается в данный момент только одна программа контроля (одного варианта). . Кроме того, управляемый режим прерываний позволяет использовать эффективнее вычислитель для обработки фоновых программ. Совмещение операций опроса пультов обучаемых с режимом считывания . информации о готовых ответах расширяет дидактические возможности уст-i ройства, снижая время обс{1уживания готовых пультов. Кроме того, предлагаемый класс беспечивает ускорение процесса облуживания пультов обучаемых в 1,6раза по сравнению с известным. Формула изобретения Автоматизированный класс для контроля знаний обучаемых, содержа1ций последовательно включенные генератор, счетчик, .дешифратор, блок элементов И и пульты обучаемых, а также вычислитель, отличающийся тем, .что, с целью повышения точности контроля, в него введены послвдовательью соединенные бло буферной памяти, блок элементов ИЛИНЕ, распределитель импульсов и регистр опроса, два элемента ИЛИ, счет чик времени и формирователь мпульсов, первый вход которого соединен через один из элементов ИЛИ с выходом блока элементов ИЛИ-НЕ, второй вход через счетчик времени - с выходом генератора, один выход непосредственно - -с вторым входом распределителя импульсов и с вторым входом регистра опроса, а другой выход непосредственно с третьим входом регистра опроса, выход которого подключен к первому входу блока буферной памяти, второй вход которого соединен с выходом счетчика, третий входс выходами пультов обучаемых, первый выход - с вторым входом блока элементов И, а второй выход - с входом другого элемента ИЛИ, выход которого подключен к первому входу вычислителя, второй вход которого соединен с выходом счетчика времени.

Источники информации, принятые во внимание при экспертизе

Г

Т

i.i1

W

.-/ F

I т.к

.

Авторы

Даты

1982-09-30—Публикация

1981-02-25—Подача