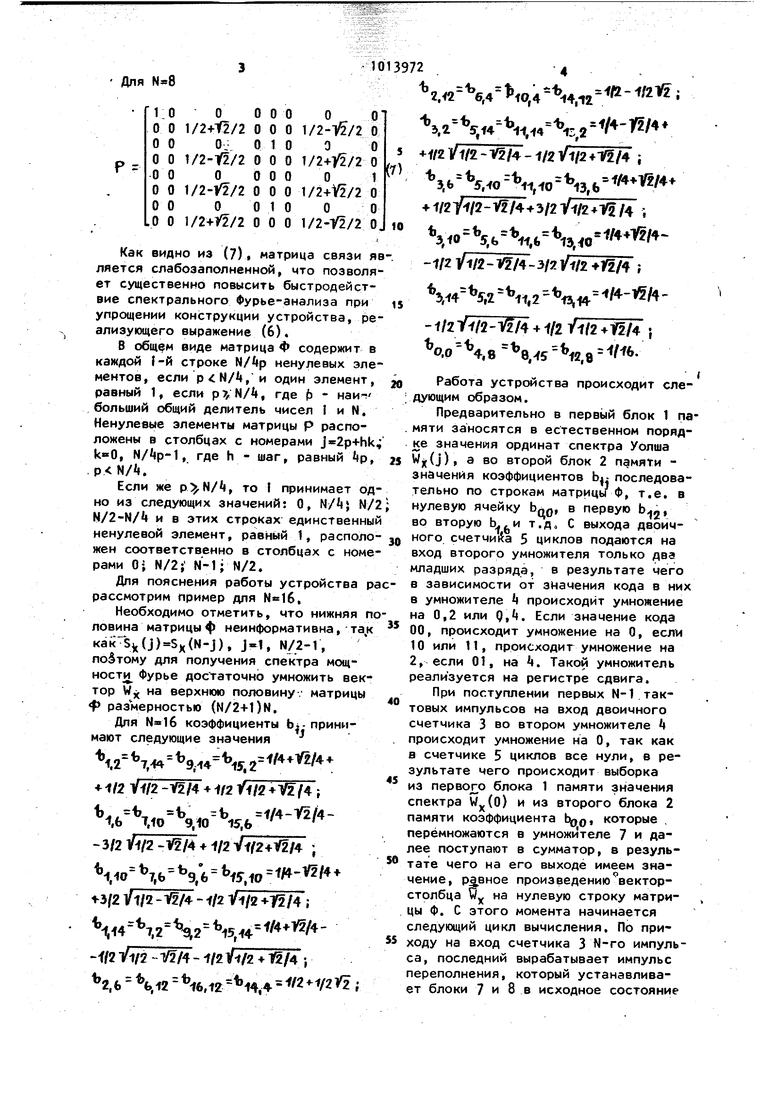

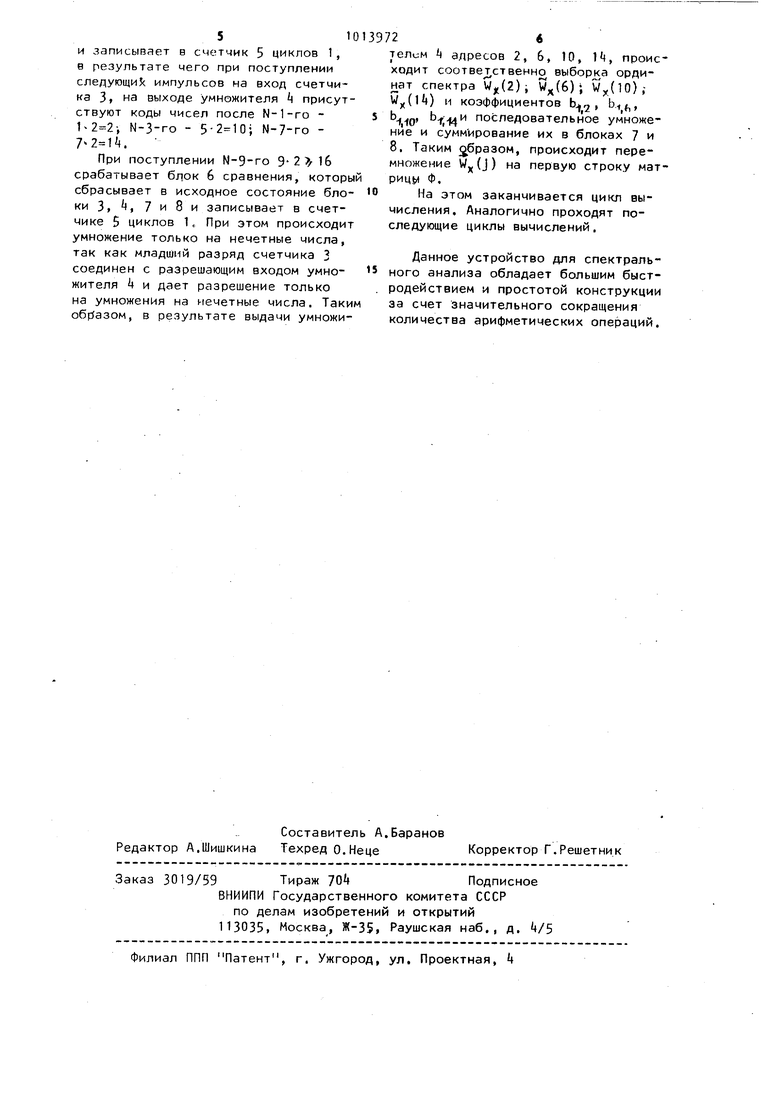

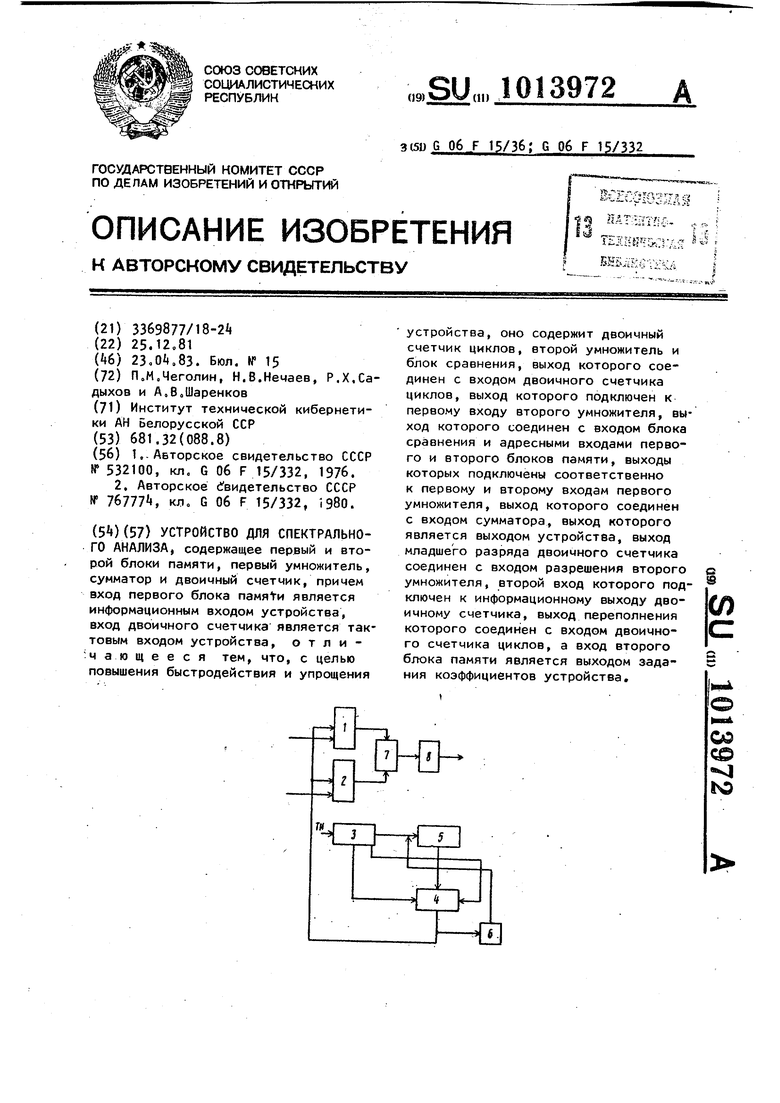

Ийобретенйе относится к вычислительной технике и может быть использовано для спектрального анализа случайных процессов. Известно устройство для вычисления спектра мощности Фурье, содержащее блок вычисления корреляционной функции, сумматор, два переключателя, блок памяти, блок вычисления спектра мощности Фурье, счетчик, триггер и соответствующие связи. Уст ройство обеспечивает вычисление спек ра мощности Фурье черезкорреляционную функцию l. Однако устройство не позволяет вы числять спектр мощности Фурье через спектр мощности Уолша, а также обладает низким быстродействием. Наиболее близким к изобретению по технической сущности является устройство для спектрального анализа, содержащее первый, второй и третий блоки памяти, первый и второй триггеры, сумматор, счетчик, коммутатор, регистр, дешифратор, два блока формирования дополнительного кода, блок у ножения, элемент И, элемент ИЛИ и соответствующие связи 2. Недостатками устройства являются сложность конструкции и низкое быстродействие вследствие большого числа вычислительных операций. Целью изобретения является повышег ние быстродействия (за счет значительного уменьшения вычислительных операций) и упрощение устройства. Поставленная цель достигается тем, что устройство для спектрального анализа, содержащее первый и второй блоки памяти, первый умножитель, сумматор и двоичный счетчик, причем вход первого блока памяти является ин формационным входом устройства, вход двоичного счетчика является тактовым входом устройства, содержит двоичный счетчик циклов, второй умножитель и блок сравнения, выход которого соединен с входом двоичного счетчика циклов, выход которого подключен к первому входу второго умножителя, выход которого соединен с входом блока срав нения и адресными входами первого и второго блоков памяти, выходы которых подключены соответственно к первому и второму входам первого умножителя, выход которого соединен с,входом сум .матора, выход которого является выхо дом устройства, выход младшего разряда двоичного счетчика соединен с вхоДОМ разрешения второго умножителя, второй вход которого подключен к икформационному выходу двоичного сметчика, выход переполнения которого соединен с входом двоичного счетчика циклов, а вход второго блока памяти, является выходом задания коэффициентов устройства. На чертеже приведена блок-схема устройства. Устройство содержит первый 1 и второй 2 блоки памяти, двоичный счетчик 3, умножитель Ц, двоичный счетчик 5 циклов, блок 6 сравнения, умножитель 7, сумматор 8. Вычисление оценки спектральной плотности мощности Фурье основано на использовании существующего матричного соотношения связи между арифметической RjjCf) и логической Pj{ (t) автокорреляционными функциями Ру (СО . , - где матричный оператор связи. Умножив(1) слева и справа на матрицу преобразования Фурье, получим РХ-PDPX 2) где Sy - спектр мощности Фурье. Всвою очередь . ) где W - матрица преобразования Уолша, Ww- энергетический спектр мощности Уолша. Тогда, подставляя (З) в (2) имеем 55j FD Так как W(2j-f)W,(2j); j Vrif2rTj N.2. Vo )MW(j), . Для N«8 00 1/2+t2/2 000 1/2-1 /2 О 0-. О 1 О О О 1/2-Y2/2 000 1/2+1 /2 О О О о о о 1/2+Y2/2 о о о 1/2Ч-У2/2 000 1/2-У2/2 0. Как видно из (7) матрица связи яв ляется слабоэаполненной, что позволяет существенно повысить быстродействие спектрального Фурье-анализа при упрощении конструкции устройства, реализующего выражение (6). В общем виде матрица Ф содержит в каждой {-и строке ненулевых элементов, если р N/i,и один элемент, равный 1, если р7,ЫА, где jb - больший общий делитель чисел I и N. Ненулевые элементы матрицы р расположены в столбцах с номерами J«2p+hk; keO, , где h - шаг, равный tip, .. Если же , то I принимает одно из следующих значений: О, N/2 N/2-N/ и в этих строках единственный ненулевой элемент, равный 1, расположен соответственно в столбцах с номерами 0; N/2; N-1; N/2. Для пояснения работы устройства ра рассмотрим пример для , Необходимо отметить, что нижняя по ловина матрицы ф неинформативна, (j)Sx(N-j), JH, N/2-1, поэтому для получения спектра мощности Фурье достаточно умножить вектор Wj( на верхнкио половину . матрицы 4 размерностью (N/2-fl)N, Для NslS коэффициенты Ь -принимают следующие значения 1., Ь +1/2 Vf/2 -V2/4 + if2 y +W/4; V%4i°V.b - -3/2 Т/112 -Т/214 + 1/2Vfr2+y2/4 ; ,fe V6 Цу.10 Ф-У2/4 1-3f2 Vl/Z W/4 - il2 Vl/2 ; Vl/2-T /4- -f/2 ii/Z + lf2/4 , Чб 4.,4 ; 2.« V 444l2 ; , +f/2 VHy.Tf2h-112Vl/2 T5/4 ; з. +1/2yi/2 Я/4-f 3/2 ; Vo b-V S o -1/2 /1/2 - Vf/4 -3/2Vf/2 +/2/4 ; V V 1,2--4i -1/2 71/2-1 +1/2 yi/2+f5/4 } %-48 V5 48 Работа устройства происходит следующим образом. Предварительно в первый блок 1 памяти заносятся в естественном порядке значения ординат спектра Ублша Wj((j), а во второй блок 2 памяти значения коэффициентов последовательно по строкам матрицы Ф, т.е. в нулевую ячейку Ьц, в первую во вторую Ь.и т.д, С выхода двоичного счетчи1 а 5 циклов подаются на вход второго умножителя только два младших разряда, в результате чего в зависимости от значения кода в них в умножителе происходит умножение на 0,2 или Q,i. Если значение кода 00, происходит умножение на О, если 10 или 11, происходит умножение на 2, если 01, на k. Такой умножитель реализуется на регистре сдвига. При поступлении первых N-1 тактовых импульсов на вход двоичного счетчика 3 во втором умножителе t происходит умножение на О, так как а счетчике 5 циклов все нули, в результате чего происходит выборка из nepBOjTO блока 1 памяти значения спектра Wj(O) и из второго блока 2 памяти коэффициента Ь, которые , перемножаются в умножителе 7 и далее поступают в сумматор, в результате чего на его выходе имеем значение, равное произведению векторстолбца Wj на нулевую строку матрицы Ф. С этого момента начинается следующий цикл вычисления. По приходу на вход счетчика 3 N-ro импульса, последний вырабатывает импульс переполнения, который устанавливает блоки 7 и 8 в исходное состояние

5101

и записьтает в счетчик 5 циклов 1, в результате чего при поступлении следующи( импульсов на вход счетчика 3, на выходе умножителя Ц присутствуют коды чисел после N-1-го N-3-го - N-7-го .

При поступлении срабатывает бл.ок 6 сравнения, который сбрасывает в исходное состояние блоки 3 . 7 и 8 и записывает в счетчике 5 циклов 1. При этом происходит умножение только на нечетные числа, так как младший разряд счетчика 3 соединен с разрешающим входом умножителя k и дает разрешение только на умножения на нечетные числа. Таким образом, в результате выдачи умножи26

телсм Ц адресов 2, 6, 10, I, происходит соответ ственно выборк а ординат спектра W(2)j W(6); W(10); Wj(1i) и коэффициентов Ц tfi

последовательное умножение и суммирование их в блоках 7 и 8. Таким бразом, происходит перемножение W(J) на первую строку матРИЦЬ( Ф.

На этом заканчивается цикл вычисления. Аналогично проходят последующие циклы вычислений.

Данное устройство для спектрального анализа обладает большим быстродействием и простотой конструкции

за счет значительного сокращения

количества арифметических операций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для спектрального анализа | 1978 |

|

SU767774A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Устройство для спектральногоАНАлизА | 1978 |

|

SU813286A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Анализатор спектра | 1981 |

|

SU1013970A1 |

| Анализатор спектра | 1983 |

|

SU1151987A1 |

| Генератор случайного процесса | 1982 |

|

SU1020820A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР СПЕКТРА | 1991 |

|

RU2022352C1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА, содержащее первый и второй блоки памяти, первый умножитель, сумматор и двоичный счетчик, причем вход первого блока naMfltH является информационным входом устройства, вход двоичного счетчика является тактовым входом устройства, о т л и чающееся тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит двоичный счетчик циклов, второй умножитель и блок сравнения, выход которого соединен с входом двоичного счетчика циклов, выход которого подключен к первому входу второго умножителя, выход которого соединен с входом блока сравнения и адресными входами первого и второго блоков памяти, выходы которых подключены соответственно к первому и второму входам первого умножителя, выход которого соединен с входом сумматора, выход которого является выходом устройства, выход младшего разряда двоичного счетчика соединен с входом разрешения второго i умножителя, второй вход которого под(Л ключен к информационному выходу двоичному счетчика, выход переполнения которого соединен с входом двоичного счетчика циклов, а вход второго бгюка памяти является выходом задания коэффициентов устройства. со ч1 1чд

Авторы

Даты

1983-04-23—Публикация

1981-12-25—Подача