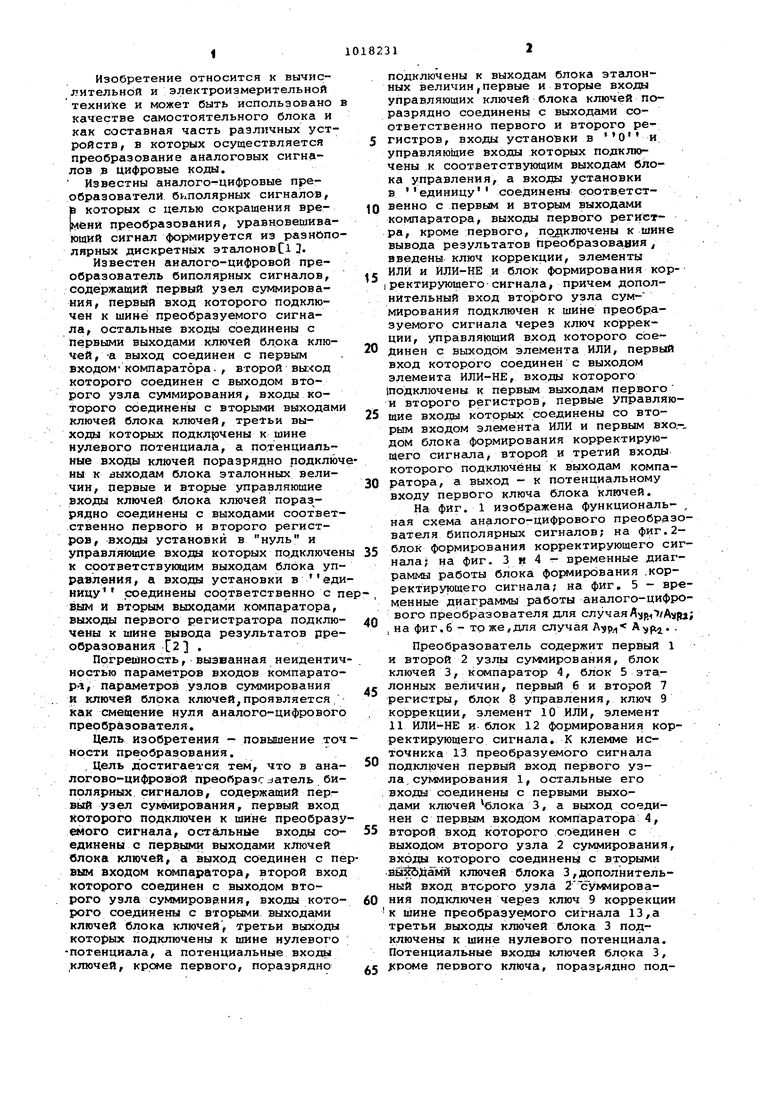

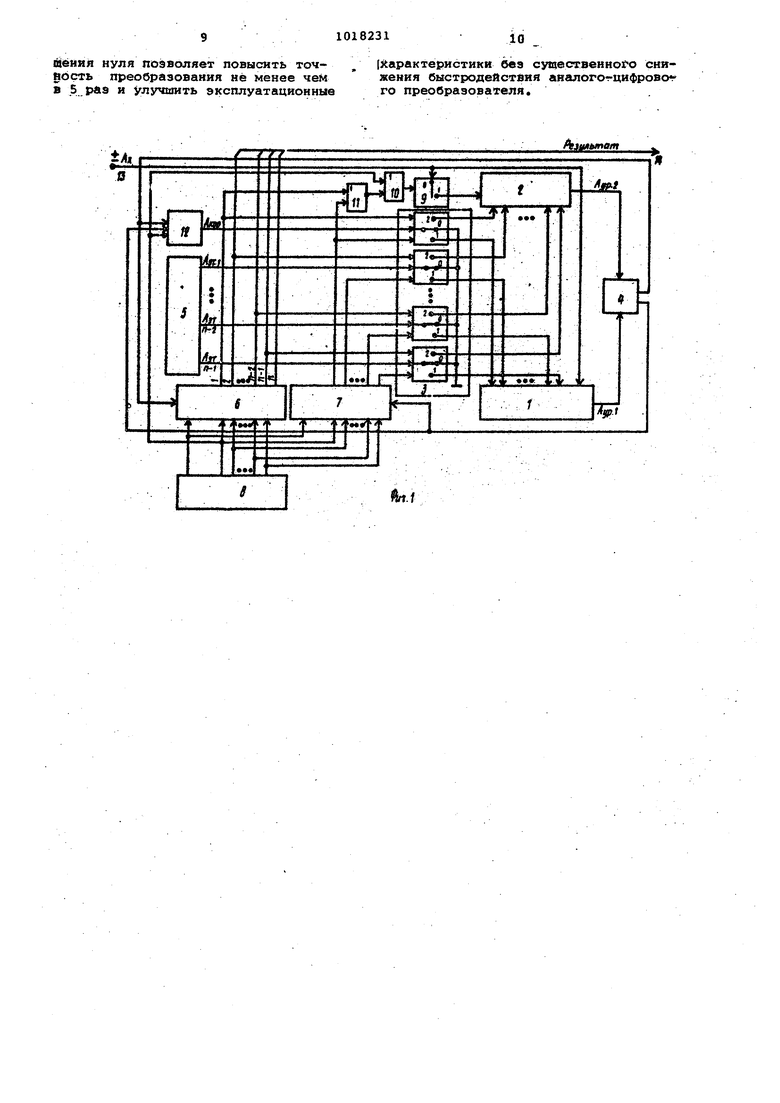

Изобретение относится к вычислительной и электроизмерительной технике и может быть использовано качестве самостоятельного блока и как составная часть различных устройств, в которых осуществляется преобразование аналоговых сигналов в цифровые коды. Известны аналого-цифровые преобразователи биполярных сигналов, Ё которых с целью сокращения вре у1ени преобразования, уравновешивающий сигнал формируется из раэнопо лярных дискретных эталонов J. Известен аналого-цифровой преобразователь биполярных сигналов, содержащий первый узел суммирования, первый вход которого подключен к шине преобразуемого сигнала, осташьные входы соединены с первыми выходами ключей блока ключей, -а выход соединен с первым входом-компаратора-, второй которого соединен с выходом второго узла суммирования, входы которого соединены с вторыми выходам ключей блока ключей, третьи выходы которых подключены к шине нулевого потенциала, а потенциальные входы ключей поразрядно подклю ны к выходам блока эталонных величин, первые и вторые управляющие входы ключей блока ключей поразрядно соединены с выходами соответ ственно первого и второго регистров, входы установки в нуль и управляющие входы которых прдключе к соответствующим выходам блока уп равления, а входы установки в ед ницу соединены соответственно с вым и вторым выходами компаратора, выхода первого регистратора подклю чены к шине вывода результатов рре образования 2 . Погрешность, вызванная неиденти ностью параметров входов компарато Р1, параметров узлов суммирювания и ключей блока ключей,проявляется. как смещение нуля аналого-цифровог преобразователя. Цель изобретения - повышение то ности преобразования. . Цель достигается тем, что в ана логово-цифроаой преолразс атель би полярных сигналов, содержащий первый узел суквиирования, первый вход которого подключен к шине преобраз fMoro сигнала, остальнйе входы со единены с первыми выходами ключей блока ключей, а выход соединен с п вым входом компаратора, второй вхо которого соединен с выходом второго узла суммирования, входы кото рого соединены с вторыми выходами ключей блока ключей, третьи выходы которых подключены к шине нулевого потенциала, а потенциальные входы ключей, первого, поразрядно подключены к выходам блока эталонных величин,первые и вторые входы управляющих ключей блока ключей поразрядно соедннень с выходами соответственно первого и второго регйстров, входы установки в управляющие входы которых подклюгчены к соответствующим выходам блока управления, а входы установки в единицу соединены соответственно с первым и вторым выходгшш компаратора, выходы первого регистра, кроме первого, подключены к шине вывода результатов преобразования j введены ключ коррекции, элементы ИЛИ и ЙЛИ-НЕ и блок формирования кор1ректирующего-сигнала, причем дополнительный вход второго узла суммирования подключен к шине преобразуемого сигнала через ключ коррекции, упра;вляющий вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом элемента ИЛИ-НЁ, входы Которого 1подключены к первым выходам первого и второго регистров, первые управляющие входа КОТОРЫХ соединены со вторым входом элемента ИЛИ и первым вхо.-„ дом блока формирования корректирующего сигнала/ второй и третий входы которого подключены к выходам компаратора, а выход - к потенциальному входу первого ключа блока ключей. На фиг. 1 изображена функциональ- , ная схема аналого-цифрового преобразователя биполярных сигналов; на фиг.2блок формирования корректирующего сигнала; на фиг. 3 н 4 г- временные диаграммы работы блока формирования .корректирующего сигнала; на фиг, 5 - временные диаграммы работы аналого-цифрового преобразователя для случаяЛ) . на фиг.6 - то же,для случая . . Преобразователь содержит первый 1 и второй 2 узлы суммирования, блок ключей 3, Компаратор 4, блок 5 эталонных величин, первый 6 и второй 7 регистры, блок 8 управления, ключ 9 коррекции, элемент 10 ИЛИ, элемент 11 ЙЛИ-НЕ и блок 12 формирования корректирующего сигнала. К клемме источника 13 преобразуемого сигНгша подключен первый вход первого узла суммирования 1, остальные его входы соединены с первыми выхо дами ключейЛблока 3, а ВЕЛХОД соединен с первым входом компаратора 4, второй вход которого соединен с выходом второго узла 2 суммирования, входы которого соединены с вторыми вйй5йа мй ключей блока 3,дополнительный вход второго узла 215уммирования подключен через ключ 9 коррекция к шине преобразуемого сигнала 13,а третьи выходы ключей блока 3 подключены к шине нулевого потенциала. Потенциальные входы ключей блока 3, jcpoMe первого ключа, поразрядно подключеиы к выходги блока 5 эталонных величин, первые и вторые управляющие входы ключей блока 3 поразрядно соединены с вьрсодами, соответственно , первого б и второго 7 регистров, входы установки в О и управляющие вхол ко.торых подклю чены к соответствующим выходам блока 8 управления, а входы установки в единицу первого 6 и второго 7 регистров соединены, соответственно, с первшл и вторьол выходами компара тора 4. К шпене вывода результатов преобразования 14. подключены все, кремне. первого, выходы первого регистра 6 Упр1авляю11Шй. вход кл1рча коррекции 9 соединен с выходом элемента 10 ИЛИ, первый звход которого соединен с выходом элемента 11 йЛИ-НЕ, входаг которого подключены к Евьосодам первого 6 и второго 7 регистров, первые управляющие входы которых соединены с вторым .входом элемента 10 ИДИ и первым входом блока 12 формирования корректирующего сигнала, два входа которого подключены к выходам компаратора 4, а выход блока 12 формирования;корректирующего сигнала 1 соединен с потенциальным входом первого ключа блока 3,

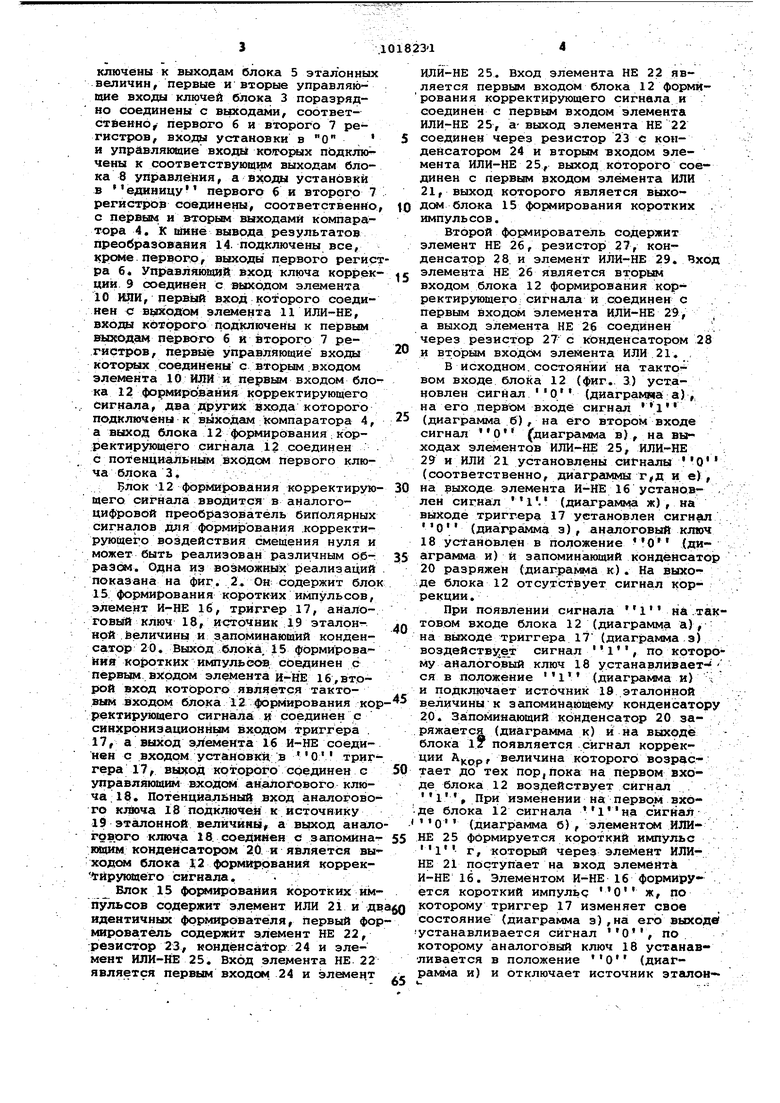

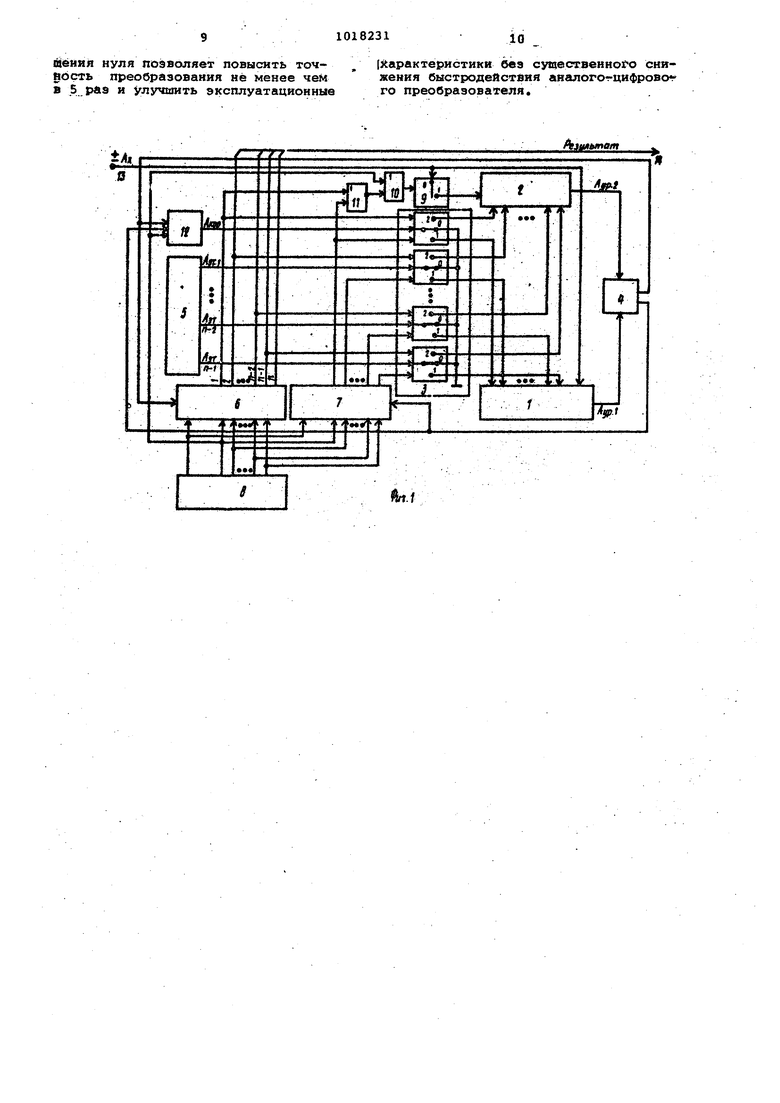

5лок 12 формирования ко рректирующего сигнала вво датся в аналогоцифровой преобразователь биполярных сигналов д;1я формирования .корректирующего воздействия смещения нуля и может быть реализован различным Об-t разом. Одна из возможных реализаций показана на фиг. 2. Он содержит блок 15 формирования коротких импульсов, элемент И-НЕ 16, триггер 17, аналоговый ключ 18, источник 19 эталон ной величины и з апоминаюший конденсатор 20, Выход блока, 15 формирования коротких импульёов соединен с первым входом элемента и-НЕ 16,второй вход которого является тактовым входом блока 12 формирования корректирующего сигнала; и соединен с синхрбнизационйым входом триггера . 17, а выход sjteMema 16 И-НЕ соединен с входом установки в Отриггера 17, вызсод которого соединен с управляющим входом аналогового ключа . 18. Потенцйад11Ьный вход аналогового ктаоча IВ подклю ея к источнику 19 эталонной величины/ а выход аналогового ключа 18. соединен с запоминающим конденсатором 20 и является выходом блока 1:2 формирования коррек йрукядего сигнала.

Блок 15 формирования коротких имtfynbcoB содержит элемент ИЛИ 21 и дв идентичных формирователя, первый формирователь содержит элемент НЕ 22, :резистор 23, конд енсатор 24 и элемент ИЛИ-НЕ 25. Вход элемента НЕ.22 является первым входом 24 и элемент

.ЛЙ-НЕ 25. Вход элемента НЕ 22 явяется первым входом блока 12 формиования корректирующего сигнала и оединен с первым входом элемента ЛИ-НЕ 25, а- выход элемента НЕ 22 оединен через резистор 23 с коненсатором 24 и вторБм входом элеента ИЛИ-НЕ 25, выход которого соеинен с первым входом элемента ИЛИ 21, выход которого является выхое блока 15 формирования коротких . импульсов.

Второй формирователь содержит элемент НЕ 26, резистор 27, коненсатор 28 и элемент ИЛИ-НЕ 29. Вход элемента НЕ 26 является вторым входом блока 12 формирования корректирующего: сигнала и соединен с первым входом элемента ИЛЙ-НЕ 29, . а выход элемента НЕ 26 соединен через резистор 27 с конденсатором 28 и вторым входом элемента ИЛИ 21.

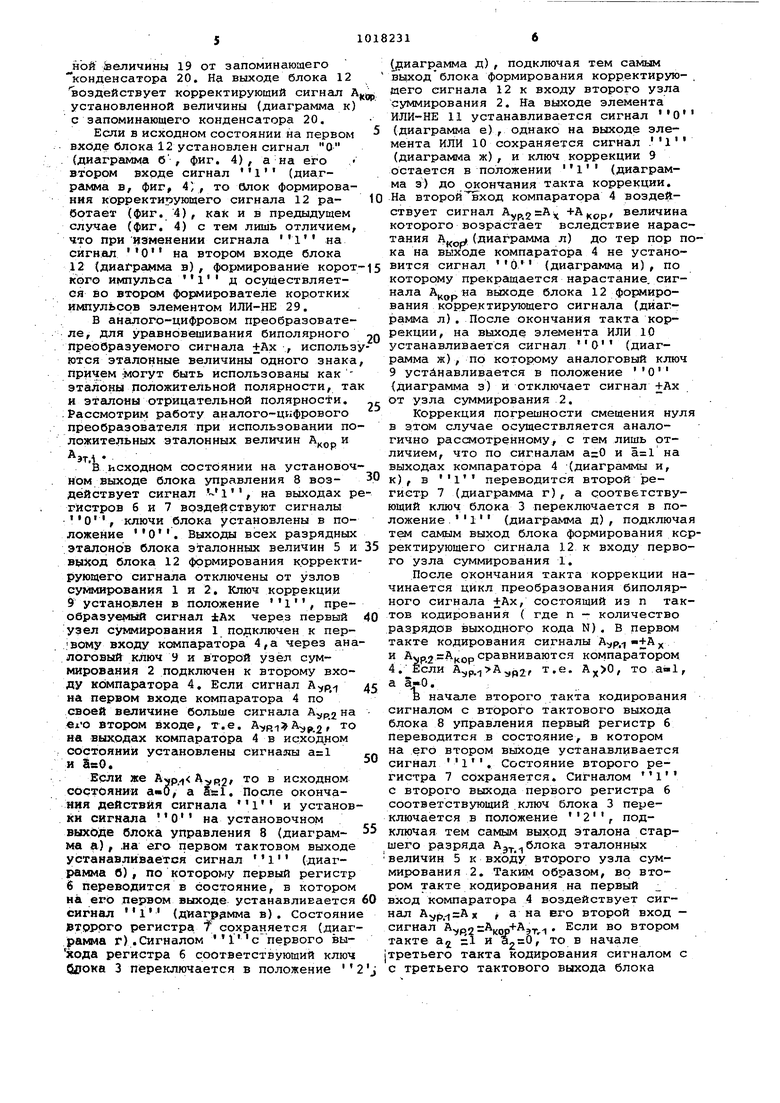

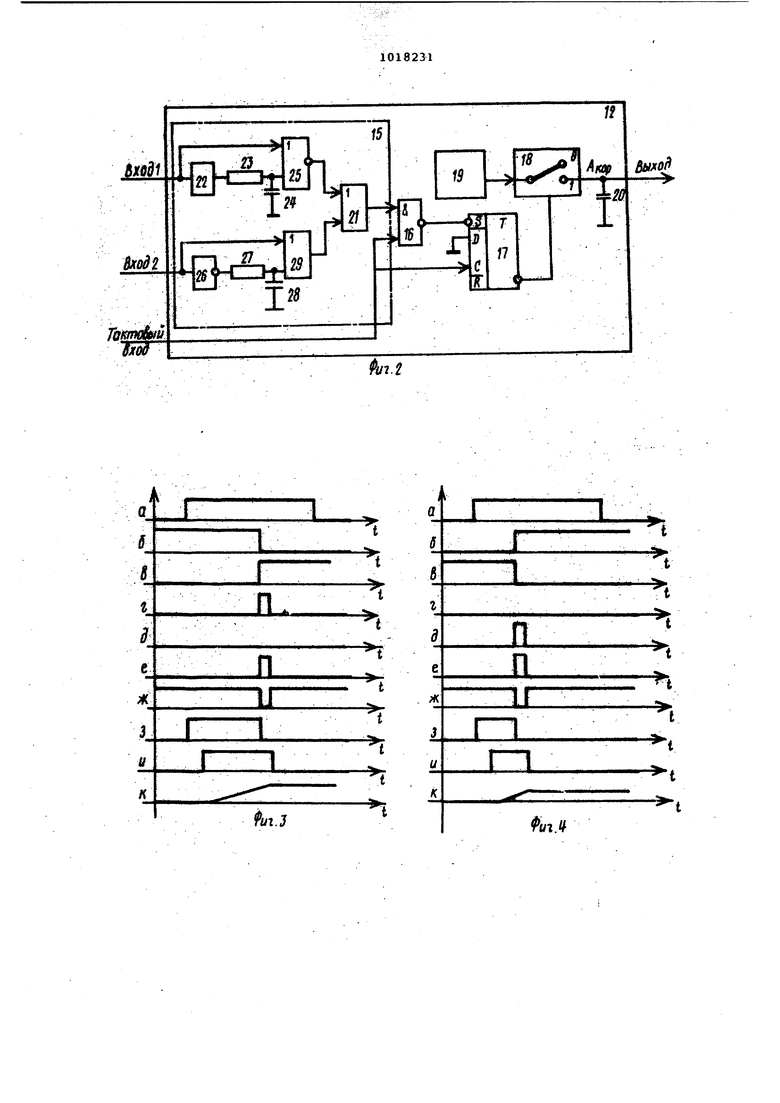

В Исходном.состоянии на такто вом входе блока 12 (фиг.. 3) установлен сигнсш О/ (диаграмйа а), На его .первх вхоДё сигнал .1 (диаграмма б), на его втором входе

О

{диагра1.вла в) , на высигнал

ходах элагентов ИЛИ-НЕ 25, ИЛИ-НЕ 29 и ИЛИ 21 установлены си гналы О (соответственно, диаграммы и е), на выходе элемента И-НЕ 16 установ- .: лен сигнал . (диаграьола ж) , на выходе триггера 17 установлен сигнал О (диаграмма з) , аналоговый ключ 18 установлен в положение О (диаграмма и) и запоминающий конденсатор 20 разряжен (диаграмма к). На выходе блока 12 отсутствует сигнал коррекции.

При появлении сигнала 1 на .тактовом входе блока 12 (диаграмма а), ; на выходе триггера 17 (диаграмма э) воэдействуе т сигнал 1, по KOTOpioму аналоговый ключ 18 устанавливается в положение Ч (диаграмма и) ч и подключает источник 19 эталонной величины к запоминающему конденсатору 20. запог инающий конденсатор 20 заряжается (диаграмма к) и на выходе блока Iz появляется сигнал коррекции , величина которого возрастает до тех пор,пока на первом входе блока 12 воздействует сигнал , При изменении на первом входе блока 12 сигнала 1на сигнал О (диаграмма б) , элементе ИЛИНЕ 25 формируется короткий импульс г, который через элемент ИЛИНЕ 21 поступает на вход элемента И-НЕ 16. Элементом И-НЕ 16 формируется короткий импульс О ж, по которому триггер 17 изменяет свое состояние (диаграмма з),на его выходе устанавливается сигнал О, по которому аналоговбД ключ 18 устанав(диагливается в положение

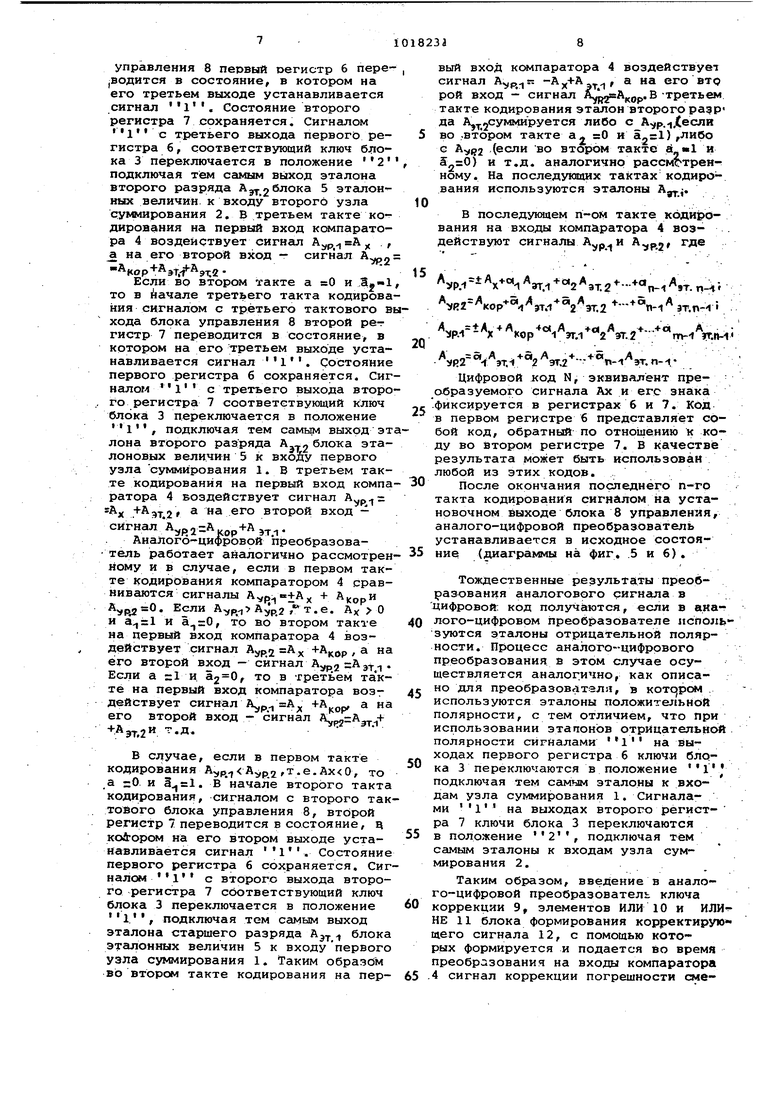

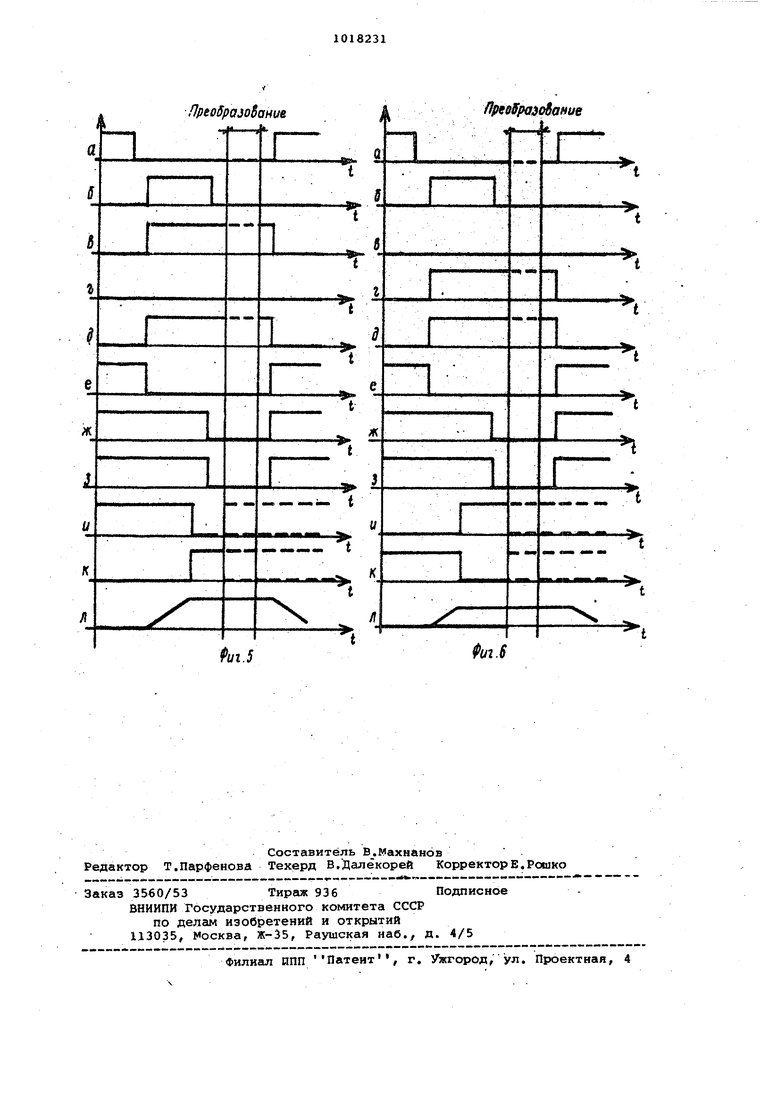

рамма и) и отключает источник эталон- ной величины 19 от запоминающего конденсатора 20. На выходе блока 12 воздействует корректирующий сигнал А установленной величины (диаграмма к) с запоминающего конденсатора 20. Если в исходном состоянии на первом входе блока 12 установлен сигнал О . (диаграмма б , фиг. 4), а на его втором входе сигнал Ч (диаграмма в, фиг, 4}, то блок формирования корректирующего сигнала 12 работает (фиг. 4), как и в предыдущем случае (фиг. 4) с тем лишь отличием, что при изменении сигнала Ч на на втором входе блока сигн;ал 12 (диаграмма в), формирование корот кого импульса «i д осуществляется во втором формирователе коротких кштульсрв элементом ИЛИ-НЕ 29. В аналого-цифровом преобразователе, для уравновешивания биполярного преобразуемого сигнала ±Ах , использ ются эталонные величины одного знака причем могут быть использованы какэталоны положительной полярности, та и эталоны отрицательной полярности. .Рассмотрим работу аналого-цифрового преобразователя при использовании по ложительных эталонных величин В исходном состоянии на установоч ном выходе блока управления 8 воздействует сигнал -1, на выходах р гистров б и 7 воздействуют сигналы О, ключи блока установлены в положение . Выходы всех разрядных .эталонов блока эталонных величин 5 и выход блока 12 формирования корректи рующего сигнала отключены от узлов су1 шрования 1 и 2. Ключ коррекции 9 установлен в положение , преобразуемый сигнал ±Ах через первый узел суммирования 1 подключен к пер;вому входу компаратора 4,а через ана логовый ключ 9 и второй узел суммирования 2 подключен к второму входу компаратора 4, Если сигнал As, на первом входе компаратора 4 по своей величине больше сигнала на «iO втором входе, т.е. А-ур.-|: А г на выходах компаратора 4 в исходном состоянии установлены сигналы и SsO. Если же ,Av92 то в исходном состоянии авО, а SWl. После окончания действия сигнгша и установО на установочном ки сигнала . .. ,,. выходе блока управления 8 (диаграмма а), .на его первом тактовом выходе устанавливается сигнал Ч (диаграмма в), по которому первый регистр б переводится в состояние, в котором на его первом выходе устанавливается сигнал Ч (диагрэмма в). Состояние ВТОРОГО регистра f сохраняется (диаграмма Г) .Сигналом Чспервого регистра б соответствующий ключ 3 переключается в положение 2 (риаграмма д) , подключая тем самым выход блока формирования корректирую- , иего сигнала 12 к входу второго узла суммирования 2. На выходе элемента ИЛИ-НЕ 11 устанавливается сигнал (диаграмма е), однако на выходе элемента ИЛИ 10 сохраняется сигнал . Ч (диаграмма ж), и ключ коррекции 9 остается в положении i (диаграмма з) до окончания такта коррекции. На второй вход компаратора 4 воздействует сигнал , величина которого возрастает вследствие нарастания (диаграмма л) до тер пор пока на выходе компаратора 4 не установится сигнал О (диаграмма и), по которому прекращается нарастание, сигнала выходе блока 12 формирования корректирующего сигнала (диаграмма л). После окончания такта коррекции, на выходе элемента ИЛИ 10 устанавливается сигнал О (диаграмма ж), по которому аналоговый ключ 9 устанавливается в положение О (диаграмма з) и отключает сигнал +Ах от узла суммирования 2. Коррекция погрешности смещения нуля в этом случае осуществляется аналогично рассмотренному, с тем лишь отличием, что по сигналам и на выходах компаратора 4 (диаграммы и, к) , в переводится второй регистр 7 (диаграмма г), а соответствующий ключ блока 3 переключается в положение . 1 (диаграмма д), подключая тем самым выход блока формирования корректирующего сигнала 12 к входу первого узла суммирования 1. После окончания такта коррекции начинается цикл преобразования биполярного сигнала +Ах, состоящий из п тактов кодирования ( где п - количество разрядов выходного кода N). В первом такте кодирования сигналы А.,р,-+А , и Ач,р 2-АКОР компаратором 4. Если .А,,р2, т.е;. , то a«l, а а-О. В начале второго такта кодирования сигналом с второго тактового выхода блока 8 управления первый регистр 6 Переводится в состояние, в котором на его втором выходе устанавливается сигнал Ч . Состояние второго регистра 7 сохраняется. Сигналом Ч с второго выхода первого регистра 6 соответствующий .ключ блока 3 переключается в положение 2 , подключая тем самым выход эталона старшего разряда АЗ блока эталонных величин 5 к входу второго узла суммирования 2. Таким образом, во втором такте кодирования на первый вход компаратора 4 воздействует сигнал А,р.-,Ах а на ЕГО второй вход сигнал AVR ,i Если во втором а,,0, то в начале такте а/. третьего такта кодирования сигналом с с третьего тактового выхода блока управления 8 первый регистр 6 пере|Водится в состояние, в котором на его третьем выходе устанавливается сигнал 1 . Состояние второго регистра 7 сохраняется. Сигналом 1 с третьего выхода первого регистра 6, соответствующий ключ блока 3 переключается в положение 2 подключая тем самым выход эталона второго разряда А,2 блока 5 эталонных величин к входу второгсэ узла суммирования 2. В третьем такте кодирования на первый вход ксжпаратора 4 воздействует сигнал Aj,,A , на его второй вход - сигнал -А ор+Аэт +А9т.2 Если BQ втором такте а егО и .Щм - 1 то в йачале третьего такта кодирова ния сигналом с третьего тактового в хода блока управления 8 второй регистр 7 переводится в состояние, в котором на его третьем выходе устанавливается сигнал . Состояние первого регистра 6 сохраняется. Сиг налом с третьего выхода второ го регистра 7 соответствующий ключ блока 3 переключается в положение , подключая тем самым выход эт лона второго разряда А„2 блока эталоновых величин 5 к вхоДу первого узла суммирования 1. В третьем такте кодирования на первый вход компа ратора 4 воздействует сигнал sA +Аэт2 на его второй вход - сигнал АУР 1-А р +А „, Аналого-цифровой преобразователь работает аналогично рассмотрен ному и в случае, если в первом такте кодирования компаратором 4 сравниваются сигналы Аур:,+Ах + . Если А,р-, А,р2 , т.е. АХ О и и а:,0, TO во втором такте на первый вход компаратора 4 воздействует сигнал Aj,p2 АХ цор его второй вход - сигнал эт1 Если а 1 и , то в третьем такте на первый вход компаратора возг действует сигнал off а на его второй вход - сигнал В случае, если в первом такте кодирования А,,,т.е., то а гО и . В начале второго такта кодирования, сигналом с второго так тового блока управления 8, второй регистр 7 переводится в состояние, ц коЛ-ором на его втором выходе устанавливается сигнал . Состояние первого регистра 6 сохраняется. Сиг налом 1 с второго выхода второго регистра 7 ссютветствующий ключ блока 3 переключается в положение , подключая тем самым выход эталона старшего разряда -t блока эталонных величин 5 к входу первого узла сукмирования 1, Таким образом во втором такте кодирования на первый вход компаратора 4 воздействует сигнал -Ajj+A „. , а на его вто рой вход - сигнал ,B -третьем такте кодирования эталон второго радр да А 2 уммируется либо ,р,1,(если во .втором такте а 0 и ) ,либо с Ауи2 (если во втором такте й и S 0) и т,д, аналогично расскй трен ному. На последующих тактах кодирования используются эталоны А, В последунвдем п-ом такте кодирования на входы компаратора 4 воздействуют сигналы А,,р и , где УР.1 ..2 - n-H9T. n-V ..2 эт.п-1 .1 2V2 -: «m- f tn-1i R2 Vn 2 - п-Иэт;п-1Цифровой код N, эквивалент пре- образуемого сигнала Ах и егс знака .фиксируется в регистрах 6 и 7, Код в первом регистре 6 представляет собой код, обратный по отношению к коду во втором регистре 7. В качестве результата может быть использован любой из этих кодов. После окончания последнего п-го такта кодирования сигналом на уста- , новочном выходе блока 8 управления, аналого-цифровой преобразователь устанавливается в исходное состояние (диаграммы на фиг. .5 и 6). Тождественные результаты преобразования аналогового сигнала в цифровой: код получаются, если в аналого-цифровом преобразователе псполь зуются эталоны отрицательной полярности. Процесс аналого-цифрового преобразования в этом случае осуществляется аналогично, как описано для преобразовлтэля, в используются эталоны положи7;ельНой полярности, с тем отличием, что при использовании этапонов отрицательной полярности сигналами 1 на выходах первого регистра 6 ключи блока 3 переключаются в положение i подключая тем сс№1ым эталоны к входам узла суммирования 1. Сигналами 1 на выходах второго регистра 7 ключи блока 3 переключаются в положение 2, подключая тем сгииым эталоны к входам узла суммирования 2, Таким образом, введение в аналого-цифровой преобразователь ключа коррекции 9, элементов ИЛИ 10 и 11 блока формирования корректирующего сигнала 12, с помощью которых формируется и подается во время преобразования на входы компаратора 4 сигнал коррекции погрешности смешёния нуля позволяет повысить точйость преобразования не менее чем в 5.раэ и Улучшить эксплуатационные

|}(арактеристики без с5Ш1ественно чэ снижения быстродействия аналогог-цифрово го преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Многоканальный аналого-цифровой преобразователь | 1977 |

|

SU726664A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Устройство формирования сигнала для коррекции искажений телевизионного изображения | 1985 |

|

SU1317687A2 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Адаптивный аналого-цифровой преобразователь | 1972 |

|

SU493019A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Аналого-цифровой преобразователь | 1973 |

|

SU711676A1 |

АНАПбгО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ БИПОЛЯРНЫХ СИГНАЛОВ,содержащий первый узел суммирования, первый вход которого подключен к шине преобразуемого сигнала, остальные входы соединены с первыми выходг1ми ключей блока ключей, а выход соединен с первым входом компаратора, второй вход которого соединен с выходом второго узла суммирования, входы которого соединены с вторыми выходами ключей блока ключей, третьи выходы которых подключены к шине нулевого потенциала, а потенциальные входы ключей,кроме первог о, поразрядно подключены к выходам блока эталонных величин, первые и вторые управлякядие входы ключей блока ключей поразрядно соединены с выходами соответственно первого и второго регистров, входы установки в нуль и управляющие входы которых .подключены к соответствующим входам блока управления, а входы установки в единицу соединены Соответственно с первым и вторым выходами компаратора, выходы первогорегистра, кроме первого, подключены к шине вывода результатов преобразования, отличающийся тем, что, с целью повьшения точности преобразования, в него введены ключ коррекции, элементы ИЛИ и ИЛИ-НБ и блок формирования корректирукицего сигнала, причем дополнительный &ход S второго узла сукмирования подключен к шине преобразуемого сигнала через со ключ коррекции, управлякияий вход которого соединен с выходом элемента с ИЛИ, первый выход которого соединен с выходом элемента ИЛИ-НЕ, входы которого подключены к первым выходам первого и второго регистров, первые управляющие входы которых соединены с вторым входом элемента ИЛИ и первым входом блока формирования корректирующего сигнала, второй и тре00 тий входи которого подключены к выto ходам компаратора, а выход - к потенциальном/входу первого ключа . 00 блока ключей.

зилнпат

Pui.5

11ре9Ураз(

$ui.S

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Одновибратор | 1983 |

|

SU1129716A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Проблемы создания преобразователей формы информации | |||

| Тезисы докладов IV Всесоюзного симпозиума | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-05-15—Публикация

1981-11-30—Подача