Изобретение относится к вычиспительаой технике. Известен многоканальный аналого-цифровой нреобразователь, содержащий блоки эталонов, ключи, блоки суммирования, компараторы, шифратор двоичного кода, дешиф ратор, блоки эталонов через ключи, цифровые входы которых соединены через триггеры с выходами временного распределителя, подключены каждый к соответствующему блоку суммирования, а выходы блоков суммирования соединены с компараторами, выходы которых соединены с шифратором Двоичного.кода и с дешифратором, выходы которого подсоединены к управляющим входам ключей, через которые блоки эталонов соединены с каждым из блоков суммирования YJ. OcHOBH iM недостатком устройства явгляется неэффективное использование оборудования. Известен многоканяльный аналого-цифровой преобразоплтель, сопержяишй блок .)1ОИ, выход КО1С))ГО СОР ДИНен С бЛОком коммутации, регистр результата, устройство управления и N разрядных блоков, каждый из которых включает в себя блок сравнения, блок суммирования, N линий задержки, формирующих разряды результата преобразования от первого до N -го разряда, N -канальный коммутатор, выход которого подсоединен к входу первого разрядного блока, формирующего первый разряд кода результата, выхор последнего - к входу второго разрядного блока, и так далее, а выход (N -1) -го разрядного блока подключен к входу М -го разрядного блока, в каждом разрядном блоке выход блока сравнения подсоединен к регистру результата и к блоку коммутации, выход которого подсоединен к первому входу блока суммирования, к второму входу которого через линию задержки присоединен первый вход блока сравнения, к второму входу которого подсоединен соответствующий выход блока эталонов, а выход блока суммирования соединен с входом бледуюШего разрядного блока 2,

Недостатком устройства является }1али ие коммутатора и линии задержки, котоые значительно снижают точность преобазования.

Целью изобретения является повышение точности результата преобразования.

Для этого в многоканальный аналого- ифровой-преобразователь, содержащий блок управления, N блоков сравнения, N регистров результата, блок коммутации, блоки суммирования, введены N двухтактных запоминающих устройств и N счетных триггеров, причем счетные входы счетных триггеров соединены с выходами соответствующих блоков сравнения, а вы- ходы счетных триггеров соединены с упр;авляющйии входами соответствующих двухтактных запоминающих устройств выходы которых соединены с вторыми вхо-. дам и соответствующих блоков суммирования, выходы которых соединены с входами соответствующих двухтактных запоминающих устройств, а входы счетных триггеров соединены с вторыми входами регису- ров результата и с вторым выхрдом блока управления.

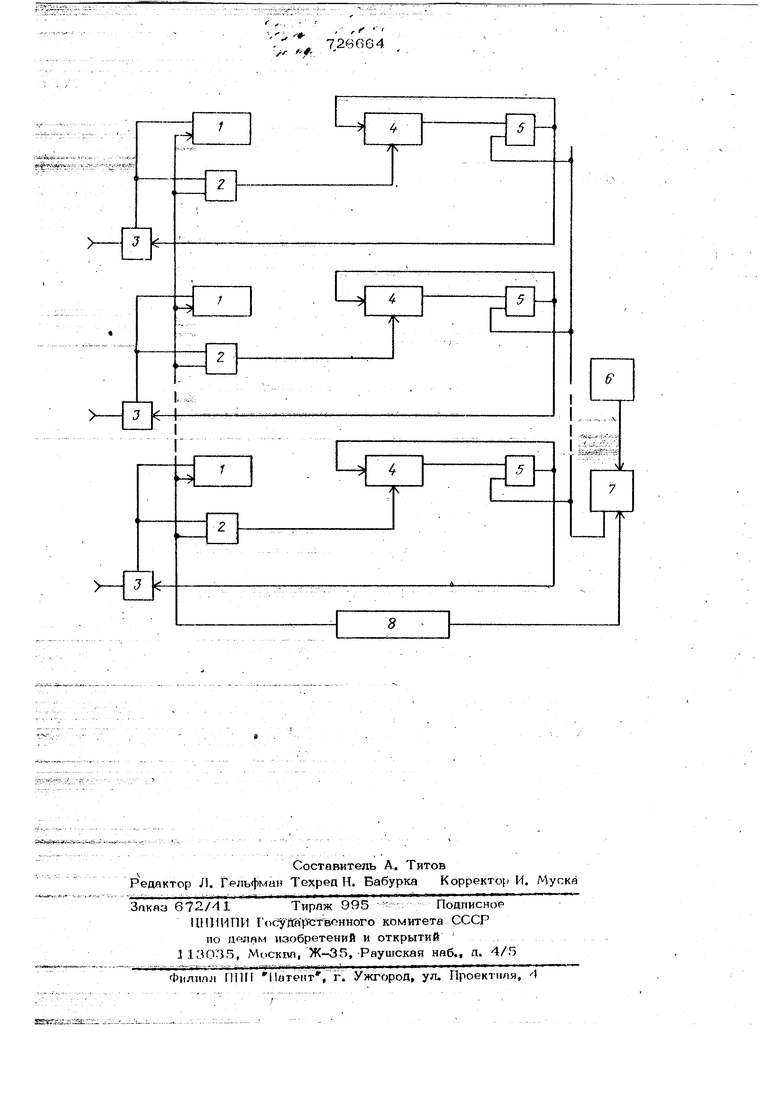

Структурная электрическая схема устройства приведена на чертеже.

Устройство содержит Ы регистров 1 результата, К счетных триггеров .2, Н блоков 3 сравнения, N двухтактных запоминающих устройств 4, Н блоков 5 суммирования, блок 6 эталонов, блок 7 коммутации эталонов, блок 8 управления. Первые входы регистров 1 и счетные входы счетных триггеров 2 соединены с соответствующими выходами блоков 3, к первым входам которых подсоединены щиИысоответствующих входных источников сигналов, а к второму входу - соответствующие входы двухтактных запоминающих устройств 4 и выходы блоков 5, выходы счетных триггеров2 подсоединены к управляющим входамсоответствующих .двухтактных запоминающих устройств 4.

Устройство реализует алгоритм поразрядного кодирования по каждому из каналов. В регистрах 1 каждого канала фор мир;у ётся код в Со6твётст1вий с вь1ражёнием

..-оС,

а Ни выходах соответствующих двухтактных запоминающих устройств 4 в конце процесса преобразования устанавливается аналоговый эквивалент, равный

эт эт-,х; иэ,-,. ос, „

2 кI- i выходные

сигналы блока 3 на первом, втором и последующих тактах.

Работа устройства осуществляется сле дующим образом.

В начальный момент времени блок 8 устанавливает счетные триггеры 2 в исходное состояние, при этом ключи двухтакных запоминающих устройств 4 принимают такое состояние, что на их выходах присутствует нулевой потенциал. На первом такте кодирования блок 8 подключает через блок 7 коммутации эталонов вес старщего ) -го эталона блока 6 к первому входу блока 5. С выхода блока 5 сигнал поступает на второй вход блока 3 и вход двухтактного запоминающего, устройства 4. В случае, если на выходе блока сравнения 3 появится единичный сигнал, он одновременно,, запишется в регистр 1 и перебросит по счетному входу сче1ный триггер 2, переводя двухтактное запоминающее устройство 4 в режим хранения суммы, полученной на первом запоминающем элементе, двухтактного запоминающего устройства 4, отслеживавшем на первом такте измененияза выходным сигналом блока 5. В случае, если на выходе блока 3 появится нулевой сигнал, счетный триггер 2 не изменит своего первоначального состояния, тем самым оставляя на первом входе блока 5 нулевой потенциал. На втором ;такте кодирования к первому входу блока 5 подается следующий (i -1 )-й эталон. При подключении к первому входу блока 5 (i -1)-го эталона он суммируется с выходным сигналом двухтактного запоминающего устройства 4, значение которого равно весу старшего i гЬ эталона, если на первом такте кодирования на выходе блока 3 был единичный сигнал, или нулевому потенциалу, если на выходе блока 3 был нулевой потенциал. С выхода блока 5 суммирующий сигнал поступает на вход блоков 3 и устройств 4, и по сигналу с блока 3 устройство 4 либо изменит свое состояние, либо нет.

С подключением V -го эталона к второму каналу устройства кодирование производится аналогично случаю подключения I старшего разряда эталонного сигнала к первому каналу устройства на первом такте кодирования. На третьем такте кодирования на первые входы трех блоков 5 соответственно подаются {г-2)-и, (| 1)-й, i -и эталонные напряжения. На втором входе сумматора первого блока формируется напряжение, равное сумме: 5726 aric.M.-OXгде ot. и сх: принимают значение О или 1 в зависимости от состояния блока 3 на 1-м и 2-м тактах соответственно. По второму и третьему каналам кодирование осуществляется .также, как по первому,соответственно на втором и первом тактах кодирования. Таким образом, в процессе кодирования эталонные напряжения грубой шкалы складываются с эталонными напряжениями бо- Ю лее точной шкалы и запоминаются в двухтактном запоминающем устройстве 4на все время преобразования входного сигнала, причем каждое из эталонных напряжеНИИ участвует в преобразовании сигнала по каждому каналу устройства в течение одного такта. Следовательно, на -м такте кодирования на выходе первого канала устройства формируется код результата преобразования, на втором канале 2 выходной код будет сформирован на (i « )-м такте, а на -м канале код будет получен на ( + )-м такте преобразования. Устройство позволяет значительно по- высиТь точность преобразования путем замены линии задержки на двухтактные запоминающие устройства, отказа от использования коммутатора и обеспечения возможности синхронизации моментов считывания результатов преобразований. Формула изобрет е н и я Многоканальный аналого-цифровой преобразователь, содержащий блок управления 46 f/ блоков сравнения, к входам которых подсоединены выходы соответствующих блоков суммирования, М регистров результата, к первым входам которых подсоедийены выходы соответствующих блоков сравнения, блок эталонов, выход которого через блок коммутации эталонов соединен с первыми входами соответствующих блоков суммирования, а управляющий вход .блока коммутации эталонов соединен с первым выходом блока управления, о. т личающийся тем, что, с целью повышения точности результата преобразования, в него введены Н двухтактных запоминающих устройств и М счетных триггеров, причем счетные входы счотньк триггеров соединены с выходами соответствующих блоков сравнения, а выходы счетных триггеров соединены с управляющими входёми соответствующих двухтактных запоминающих устройств, выходы которых соединены с вторыми входами соответствуккдих блоков суммирования, выходы которых соединены с входами соответст- вующих двухтактных запоминающих уст- ройств, а входы счетных триггеров соединены с вторыми входами регистров результата и вторым выходом блока управпения. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство ССО- №200872, кл. Н 04 L 23/ОО, 1966. 2,Гитис Э. И. Преобразователи информации для электронных цифровых вычислительных устройств. М., Энергия, 1975, с. 416.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197079A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Аналого-цифровой преобразователь биполярных сигналов | 1981 |

|

SU1018231A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

Авторы

Даты

1980-04-05—Публикация

1977-09-12—Подача