2. Устройство по п. 1, отличающееся тем, что цифроаналоговый преобразователь выполнен на первых и вторых стабилизаторах тока, на первых и вторых переключателях тока, на весовом сумматоре, выход которого соединен с выходом цифроаналогового преобразователя, а вхо ды соответственно соединены через последовательно соединенные первые

переключатели тока и первые стабилизаторы тока и через вторые переключатели тока и вторые стабилизатрры тока с шиной питания, при этом управляющие входы первых переключателей тока соединены с первыми входами цифроаналогового преобразователя, вторые входы которого соединены с управляющими входами вторых переключателей тока

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1987 |

|

SU1547059A1 |

| Цифровой режекторный фильтр | 1988 |

|

SU1608786A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| Электроразведочная станция | 1987 |

|

SU1469489A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

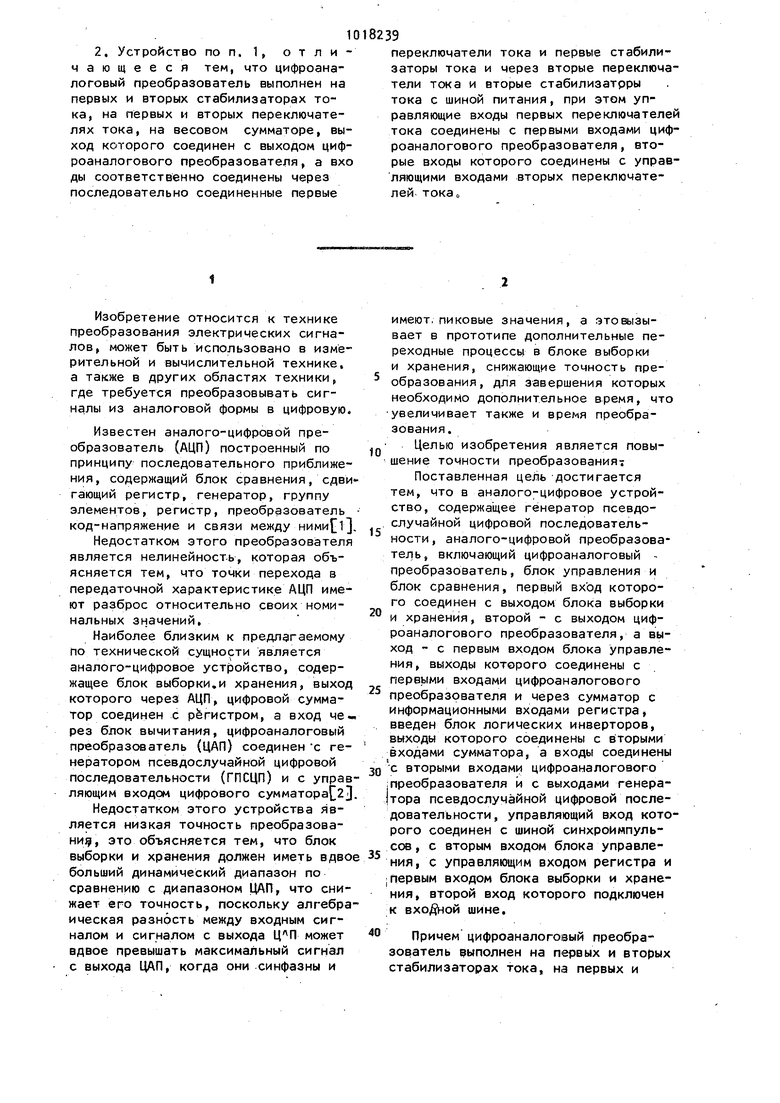

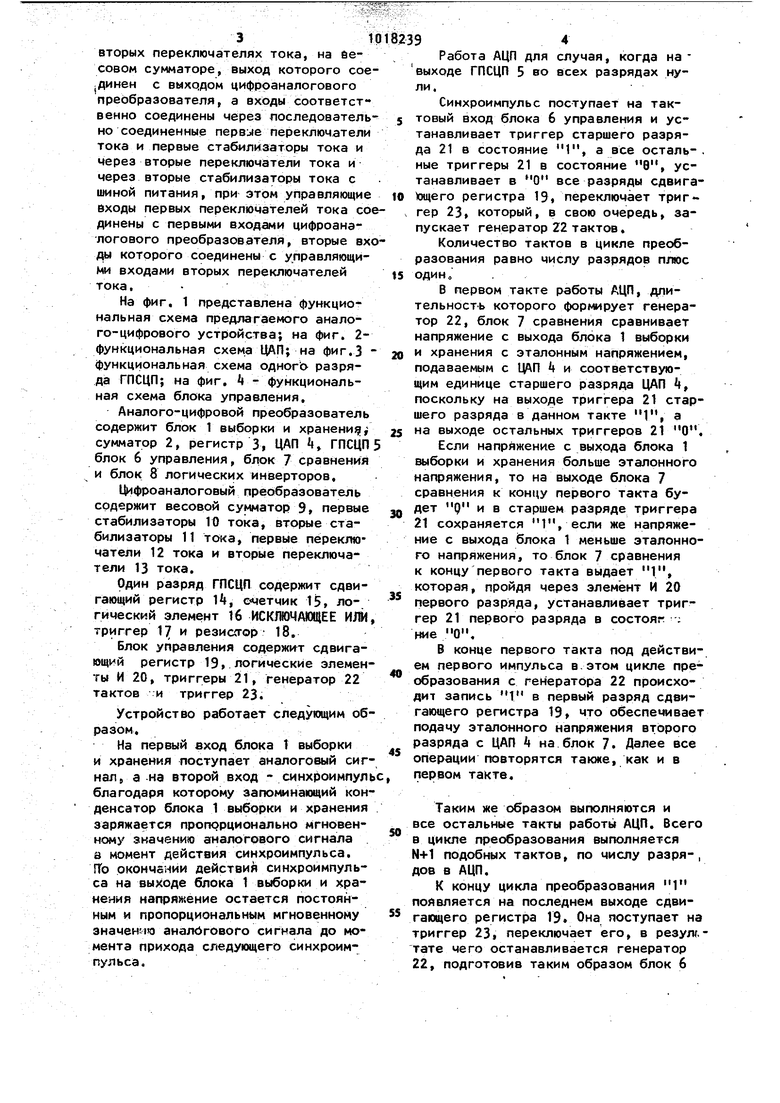

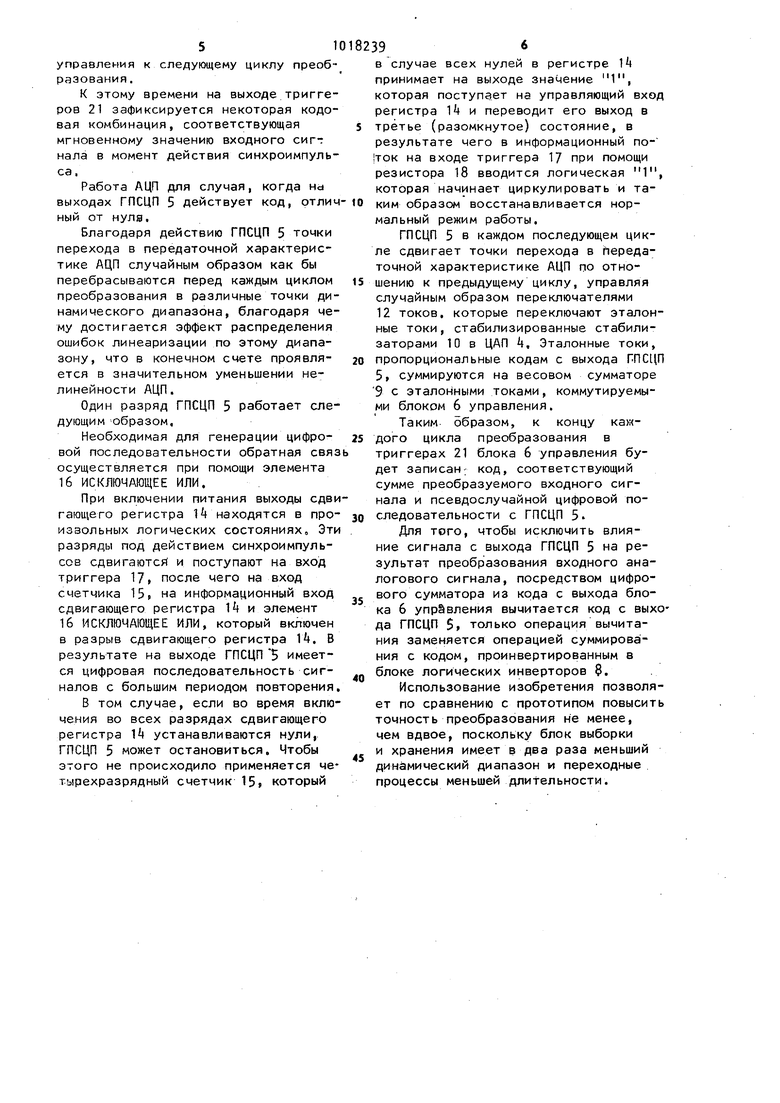

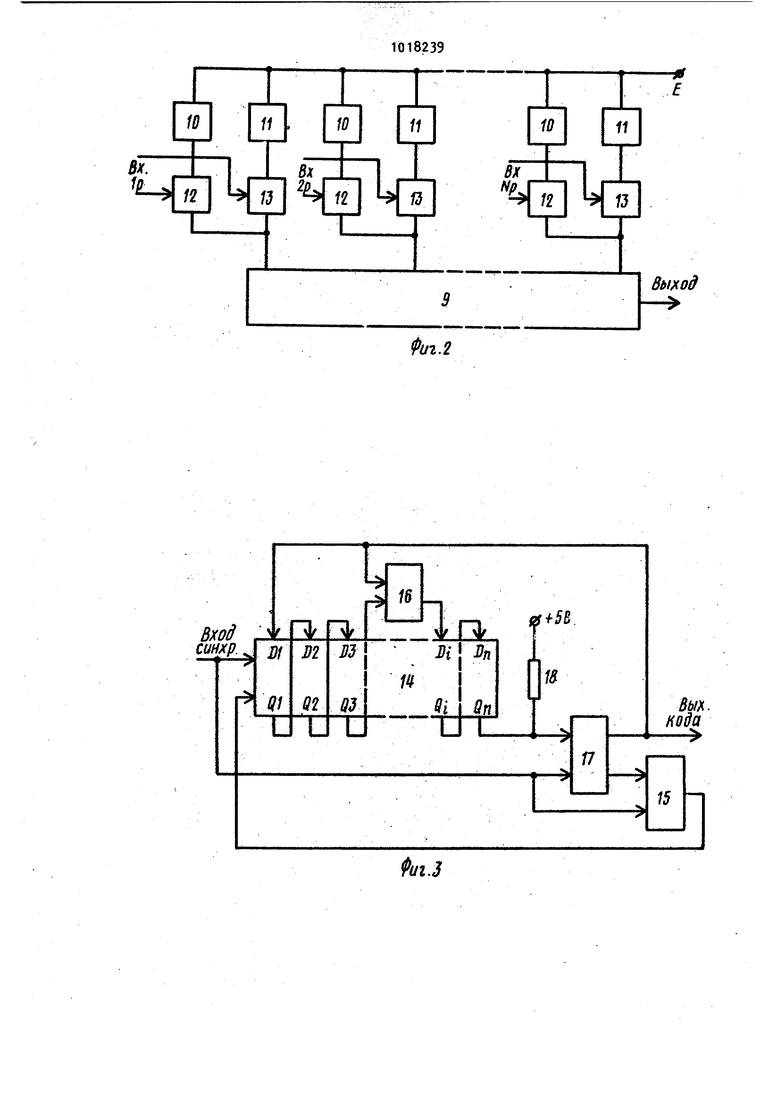

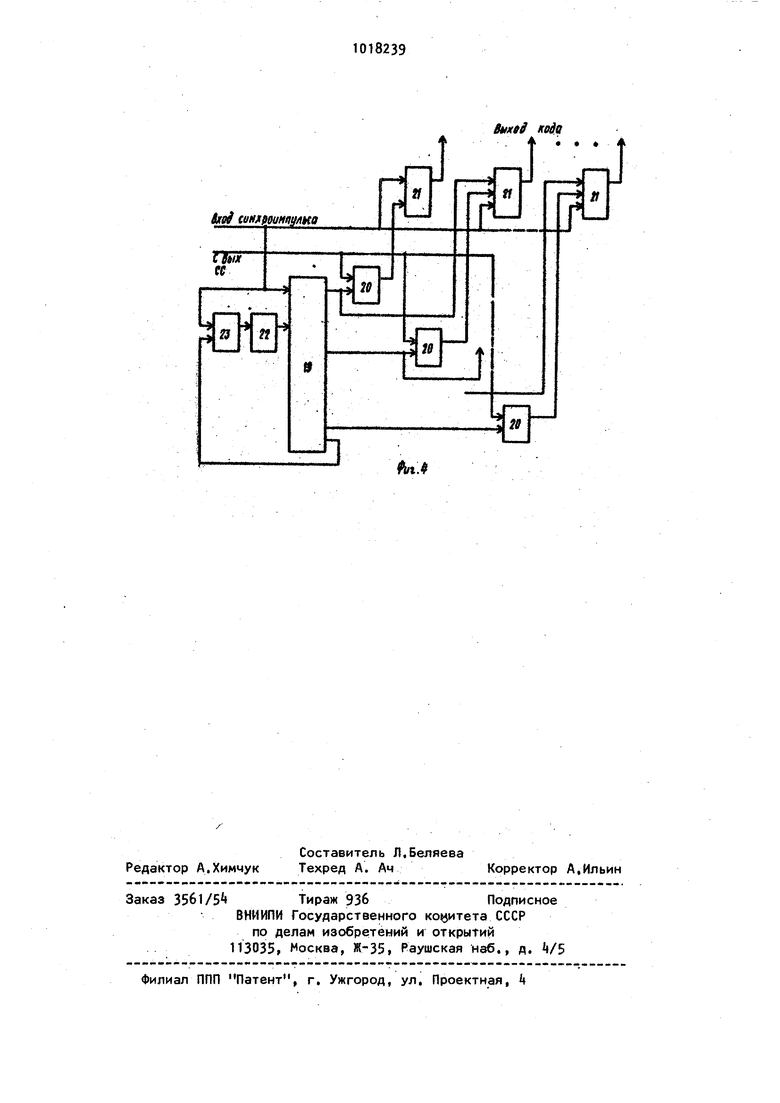

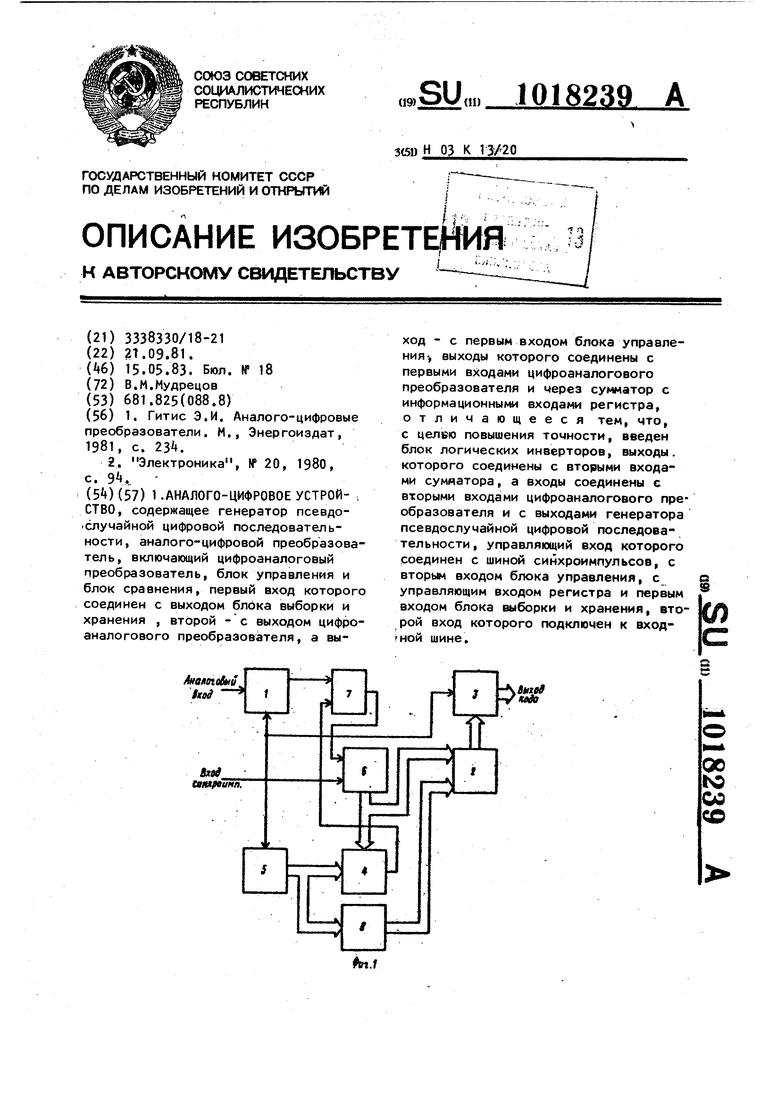

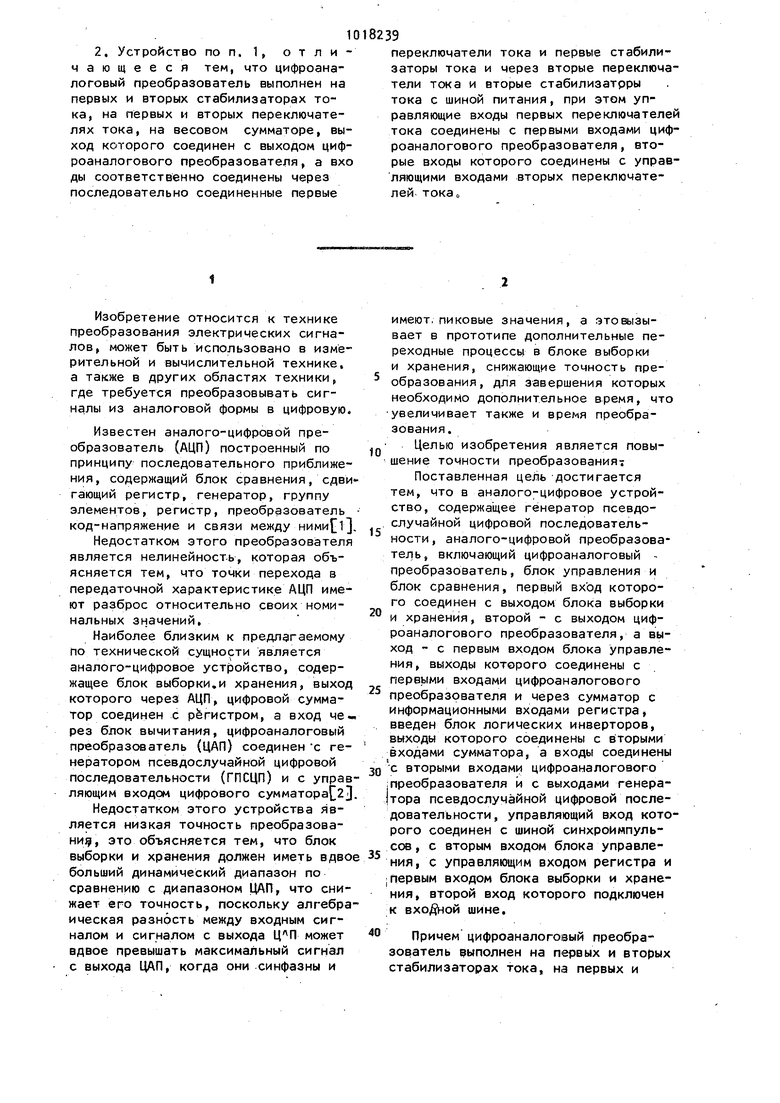

Изобретение относится к технике преобразования электрических сигналов, может быть использовано в измерительной и вычислительной технике, а также в других областях техники, где требуется преобразовывать сигналы из аналоговой формы в цифровую. Известен аналого-цифровой преобразователь (АЦП) построенный по принципу последовательного приближения, содержащий блок сравнения, сдви гающий регистр, генератор, группу элементов, регистр, преобразователь код-напряжение и связи между ними| Т Недостатком этого преобразователя является нелинейность, которая объясняется тем, что точки перехода в передаточной характеристике АЦП имеют разброс относительно своих номинальных значений, Наиболее близким к предлагаемому По технической сущности является аналого-цифровое уст(эойство, содержащее блок выборки.и хранения, выход которого через АЦП, цифровой сумматор соединен с регистром, а вход че« рез блок вычитания, цифроаналоговый преобразователь (ЦАП) соединен с генератором псевдослучайной цифровой последовательности (ГПСЦП) и с управ ляющим входом цифрового сумматора(2 Недостатком этого устройства является низкая точность преобразоваНИ9, это объясняется тем, что блок выборки и хранения должен иметь вдво больший динамический диапазон по сравнению с диапазоном ЦАП, что снижает его точность, поскольку алгебра ическая разность между входным сигналом и сигналом с выхода может вдвое превышать максимальный сигнал с выхода ЦАП, когда они синфазны и имеют, пиковые значения, а этовызывает в прототипе дополнительные переходные процессы в блоке выборки и хранения, снижающие точность преобразования, для завершения которых необходимо дополнительное время, что увеличивает также и время преобразования . Целью изобретения является повышение точности преобразования Поставленная цель достигается тем, что в аналого-цифровое устройство, содержащее генератор псевдослучайной цифровой последовательности, аналого-цифровой преобразователь, включающий цифроаналоговый преобразователь, блок управления и блок сравнения, первый вход которого соединен с выходом блока выборки и хранения, второй - с выходом цифроаналогового преобразователя, а выход - с первым входом блока управления, выходы которого соединены с первыми входами цифроаналогового преобразователя и через сумматор с информационными входами регистра, введен блок логических инверторов, выходы которого соединены с в торыми входами сумматора, а входы соединены с вторыми входами цифроаналогового преобразователя и с выходами генератора псевдослучайной цифровой последовательности, управляющий вход которого соединен с шиной синхроимпульсов , с вторым входом блока управления, с управляющим входом регистра и первым входом блока выборки и хранения, второй вход которого подключен к шине. Причем цифроаналоговый преобразователь выполнен на первых и вторых стабилизаторах тока, на первых и вторых переключателях тока, на весовом сумматоре, выход которого сое .динен с выходом цифрраналогового преобразователя, а входы соответственно соединены через последователь но соединенные первые переключатели тока и первые стабилизаторы тока и через вторые переключатели тока и через вторые стабилизаторы тока с шиной питания, при этом управляющие входы первых переключателей тока со динены с первыми входами цифроаналогового преобразователя, вторые вх да которого соединены с уяравляющиМи входами вторых переключателей тока, На фиг. 1 представлена функциональная схема предлагаемого аналого-цифрового устройства; на фиг. 2функциональная схема ЦАП; на фиг.З функциональная схема одногЬ разряда ГПСЦП; на фиг, l - функциональная схема блока управления. Аналого-цифровой преобразователь содержит блок 1 выборки и хранение сумматор 2, регистр 3, ЦАП k ГПСЦП блок 6 управления, блок 7 сравнения и блок 8 логических инверторов. Цифроаналоговый преобразователь содержит весовой сумматор 9, первые стабилизаторы 10 тока, вторые стабилизаторы 11 тока, первые переключатели 12 тока и вторые переключатели 13 тока. Один разряд ГПСЦП содержит сдвигающий регистр It, с четчик 15, логический элемент 16 ИСКЛЮЧАЮЩЕЕ ИЛ1 триггер 17 и резиагор 18. Блок управления содержат сдвигающий регистр 19, логические элемен ты И 20, триггеры 21, генератор 22 тактов и триггер 23. Устройство работает следукнцим об разом. На первый аход блока 1 выборки и хранения поступает аналоговый сиг нал, а на второй вход - синхроимпул благодаря которому запокмнающий кон денсатор блока 1 выборки и хранения заряжается пропорционально мгновенному зкачени аналогового сигнала 8 момент действия синхроимпульса. Но окончании действия синхроимпульса на выходе блока 1 выборки и хранения напряжение остается постоянным и пропорциональным мгновенному значению аналогового сигнала до момента прихода следующего синхроимпульса. Работа АЦП для случая, когда на выходе ГПСЦП 5 во всех разрядах нули. Синхроимпульс поступает на тактовый вход блока 6 управления и устанавливает триггер старшего разряда 21 в состояние 1, а все осталь- . ные триггеры 21 в состояние 9, устанавливает в 0 все разряды сдвигайщего регистра 19, переключает триггер 23, который, в свою очередь, запускает генератор 22 тактов. Количество тактов в цикле пресЛразования равно числу разрядов плюс. одино . В первом такте р аботы АЦП, длительность которого формирует генератор 22, блок 7 сравнения сравнивает напряжение с выхода блока 1 выборки и хранения с эталонным напряжением, подаваемым с ЦАП k и соответствующим единице старшего разряда ЦАП Ц, поскольку на выходе триггера 21 старшего разряда в данном такте 1, а на выходе остальных триггеров 21 О. Если напряжение с выхода блока 1 выборки и хранения больше эталонного напряжения, то на выходе блока 7 сравнения к концу первого такта будет О и в старшем разряде триггера 21 сохраняется 1, если же напряжение с выхода блока 1 меньше эталонного напряжения, то блок 7 сравнения к концу первого такта выдает 1, которая, пройдя через элемент И 20 первого разряда, устанавливает триггер 21 первого разряда в состояг -; ние О. В конце первого такта под действием первого импульса в. этом цикле преобразования с генератора 22 происходит запись t в первый разряд сдвигающего регистра 19, что обеспечивает подачу эталонного напряжения второго разряда с ЦАП 4 на блок 7. Далее все операции повторятся также, как и в первом такте. Таким же образом выполняются и все остальные такты работы АЦП. Всего в цикле преобразования выполняется N+1 подобных тактов, по числу разря-, дов в АЦП. К концу цикла преобразования 1 появляется на последнем выходе сдвигающего регистра 19. Она поступает на триггер 23. переключает его, в резуттате чего останавливается генератор 22, подготовив таким образом блок 6 управления к следующему циклу преобразования. К этому времени на выходе триггеров 21 зафиксируется некоторая кодовая комбинация, соответствующая мгновенному значению входного сигнала в момент действия синхроимпульса. Работа АЦП для случая, когда на выходах ГПСЦП 5 действует код, отлич ный от нулд. Благодаря действию ГПСЦП 5 точки перехода в передаточной характеристике АЦП случайным образом как бы перебрасываются перед каждым циклом преобразования в различные точки динамического диапазона, благодаря чему достигается эффект распределения ошибок линеаризации по этому диапазону, что в конечном счете проявляется в значительном уменьшении нелинейности АЦП. Один разряд ГПСЦП 5 работает следующим образом. Необходимая для генерации цифровой последовательности обратная связ осуществляется при помощи элемента 16 ИСКЛЮЧАЮЩЕЕ ИЛИ. При включении питания выходы сдви гающего регистра 14 находятся в произзольных логических состояниях. Эти разряды под действием синхроимпульсов сдвигаются и поступают на вход триггера 17, после чего на вход счетчика 15, на информационный вход сдвигающего регистра 1 и элемент 16 ИСКЛЮЧАЮЩЕЕ ИЛИ, который включен в разрыв сдвигающего регистра Т. В результате на выходе ГПСЦП 5 имеется цифровая последовательность сигналов с большим периодом повторения В том случае, если во время включения во всех разрядах сдвигающего регистра 14 устанавливаются нули, ГПСЦП 5 может остановиться. Чтобы этого не происходило применяется четырехразрядный счетчик 15} который В случае всех нулей в регистре 14 принимает на выходе значение 1, которая поступает на управляющий вход регистра 14 и переводит его выход в третье (разомкнутое) состояние, в результате чего в информационный поITOK на входе триггера 17 при помощи резистора 18 вводится логическая 1, которая начинает циркулировать и таким образом восстанавливается нормальный режим работы. ГПСЦП 5 в каждом последующем цикле сдвигает точки перехода в hepeдaточной характеристике АЦП по отношению к предыдущему циклу, управляя случайным образом переключателями 12 токов, которые переключают эталонные токи, стабилизированные стабилизаторами 10 в ЦАП 4, Эталонные токи, пропорциональные кодам с выхода ГПСЦП 5, суммируются на весовом сумматоре 9 с эталонными токами, коммутируемыми блоком 6 управления. Таким образом, к концу каждого цикла преобразования в триггерах 21 блока 6 управления будет записан; код, соответствующий сумме преобразуемого входного сигнала и псевдослучайной цифровой последовательности с ГПСЦП 5. Для того, чтобы исключить влияние сигнала с выхода ГПСЦП 5 на результат преобразования входного аналогового сигнала, посредством цифрового сумматора из кода с выхода блока 6 упр&вления вычитается код с выхода ГПСЦП 5, только операция вычитания заменяется операцией суммирова ния с кодом, проинвертированным в блоке логических инверторов 8. Использование изобретения позволяет по сравнению с прототипом повысить томность преобразования не менее, чем вдвое, поскольку блок выборки и хранения имеет в два раза меньший динамический диапазон и переходные процессы меньшей длительности.

tiiof {внлцоимпцлм

Btixti кеда

fin.l

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И | |||

| Аналого-цифровые преобразователи | |||

| М., Энергоиздат, 1981, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электроника, № 20, 1980, с | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-05-15—Публикация

1981-09-21—Подача