Изобретение относится к вычислительной технике, а именно к устройствам для управления обменом информа- цией, и может быть использовано при обмене информацией между различными бпокЗмя вычислительных систем при наличии дефектных узлов.

Целью изобретения является повышение достоверности функционирования и быстродействия.

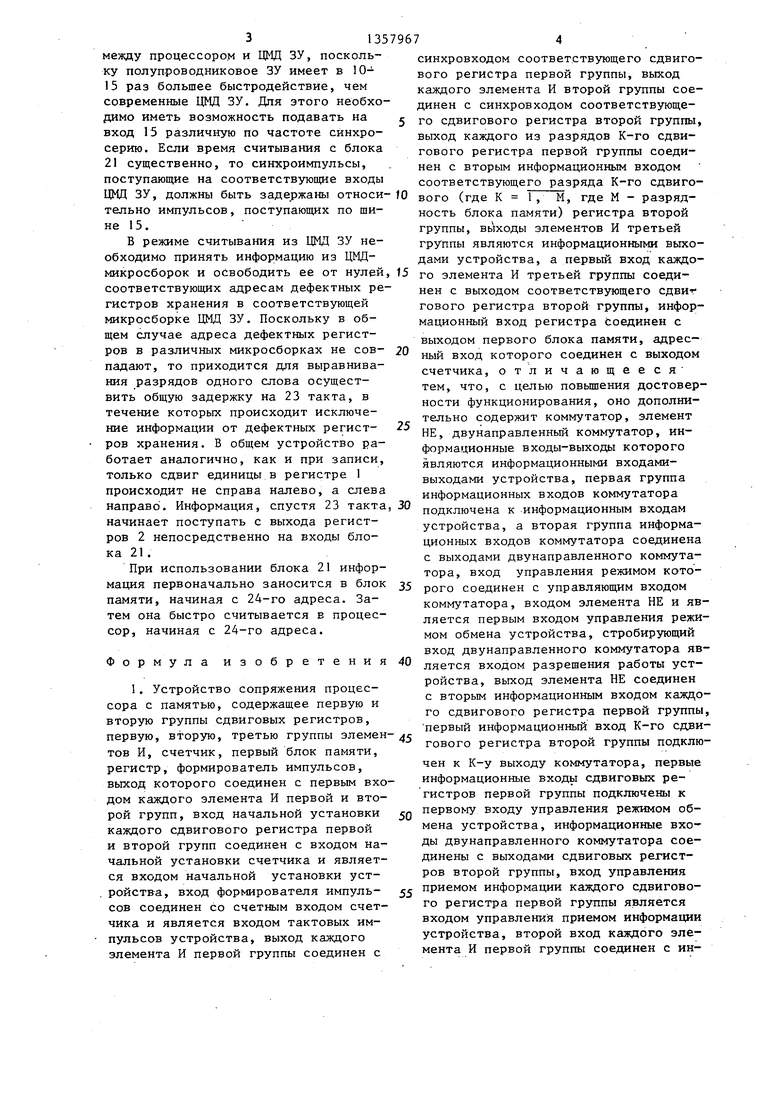

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит сдвиговые регистры первой I и второй 2 групп, элементы И первой 3, второй 4 и третьей 5 групп, счетчик 6, первый блок 7 памяти, регистр 8, формирователь 9 импульсов, коммутатор 10, элемент НЕ 11, двунаправленный коммутатор 12, информационные входы-выходы 13, вход 14 начальной установки, вход 15 так20 гистр). При этом, если соответствующий регистр хранения в ЦМД ЗУ исправен, то на прямых выходах регистра 8 1, что обеспечивает вьщачу записанной информации в крайнем правом разтовых импульсов, первый вход I6 управления режимом обмена, вход 17 раз- 25 ряде на выход через открытый элемент

решения работы, информационные входы 18 и информационные выходы 19, вход 20 управления приемом информации, второй блок 21 памяти, элементы ИЛИ 22 группы, элементы И 23 четвертой группы, второй вход 24 управления режимом -обмена.

Устройство работает следзтощим образом.

В режиме начальной установки на входе 16 устанавливают режим работы: логическая 1 - запись в ЦМД ЗУ, логический О - считывание из ЦМД ЗУ, на входы 20 подают сигнал управления;

И 5 на выход 19 и далее в ЦМД ЗУ. Если соответствующий регистр хранения дефектен, то передача информации не происходит. В течение паузы Т2 форми- 30 рователь 9 производит сдвиг информации одного из регистров в паре первого, когда в течение такта Т1 дефектный регистр хранения в ЦМД-микросбор- ке соответствующего разряда, второго когда в течение такта Т1 запись в исправный регистр хранения. Единица в регистре 1 двигается влево каждьй раз, когда встречается дефектный регистр, стробируя поочередно прием ин35

при использовании регистров К155ИР15 40 в различные разряды регист первоначально устанавливают режим па- Ра 2, вследствие чего поступление раллельного занесения информации по первому или второму информационным

этих разрядов на выход регистра 2 задержано, что приводит к разбавлению нулями последовательности поступаюсдвига влево при записи и режим сдви- 45 информации по данному разряду в га вправо - при считывании. На вход тех позициях, которые соответствуют

входам, а затем устанавливают режим

дефектным регистрам хранения в ЦМД ЗУ. Количество разрядов в регистрах 1 и 2 должно быть на единицу больше, чем допустимое количество дефектных регистров в ЦМД-микросборке (у К1602РЦ2 их 22). Использование блока 21 позволяет разбавленную нулями последовательность предварительно записать в блок памяти (на входе 24 устанавливают режим записи), а затем переписать в ЦМД ЗУ, установив на входе 24 режим считывания. Это позволяет существенно увеличить скорость обмена

14 подают сигнал начальной установки, по окончании которого счетчик 6 и регистры 2 обнуляются, а в регистры 1 заносится 1. После этого можно пе- рейти к режиму записи или считывания.

Режим записи информации в Щ-Щ ЗУ. Мы рассматриваем ЦМД ЗУ, состоящее из нескольких параллельно включенных ЦМД микросборок, например из восьми- для обмена информацией байтами. На вход 17 подают сигнал включения блока 12, а на вход 16 логическую 1, что обеспечивает передачу информации

с входов 13 через блоки 12 и 10 на входы регистров 2. Поскольку 1 в режиме записи в регистрах 1 записана в крайнем правом разряде, то строби- руется запись информации в крайний правый разряд регистров 2. На вьпсоде счетчика 6 нулевой код, что обеспечивает выборку информации из блока 7 по первому адресу о На вход 15 подают синхроимпульсы с частотой 100 кГц при использовании К1602РЦ2 с длительностью импульса Т1 и длительностью паузы Т2. По переднему фронту импульса Т1 код с выходов блока 7 переписывается в регистр 8, а синхронно поступающая информация от процессора - в первый разряд каждого из регистров 2 (каждый разряд байта в свой регистр). При этом, если соответствующий регистр хранения в ЦМД ЗУ исправен, то на прямых выходах регистра 8 1, что обеспечивает вьщачу записанной информации в крайнем правом разряде на выход через открытый элемент

И 5 на выход 19 и далее в ЦМД ЗУ. Если соответствующий регистр хранения дефектен, то передача информации не происходит. В течение паузы Т2 форми- 0 рователь 9 производит сдвиг информации одного из регистров в паре первого, когда в течение такта Т1 дефектный регистр хранения в ЦМД-микросбор- ке соответствующего разряда, второго когда в течение такта Т1 запись в исправный регистр хранения. Единица в регистре 1 двигается влево каждьй раз, когда встречается дефектный регистр, стробируя поочередно прием ин5

информации по данному разряду в тех позициях, которые соответствуют

дефектным регистрам хранения в ЦМД ЗУ Количество разрядов в регистрах 1 и 2 должно быть на единицу больше, чем допустимое количество дефектных регистров в ЦМД-микросборке (у К1602РЦ2 их 22). Использование блока 21 позволяет разбавленную нулями последовательность предварительно записать в блок памяти (на входе 24 устанавливают режим записи), а затем переписать в ЦМД ЗУ, установив на входе 24 режим считывания. Это позволяет существенно увеличить скорость обмена

между процессором и ЦМД ЗУ, поскольку полупроводниковое ЗУ имеет в 10- 15 раз большее быстродействие, чем современные ЦМД ЗУ. Для этого необходимо иметь возможность подавать на вход 15 различную по частоте синхро- серию. Если время считывания с блока 21 существенно, то синхроимпульсы, поступающие на соответствующие входы ЦМД ЗУ, должны быть задержаны относи тельно импульсов, поступающих по шине 15.

В режиме считывания из ЦМД ЗУ необходимо принять информацию из ЦМД- микросборок и освободить ее от нулей соответствующих адресам дефектных регистров хранения в соответствующей микросборке ЦМД ЗУ. Поскольку в общем случае адреса дефектных регистров в различных микросборках не сов- падают, то приходится для выравнивания разрядов одного слова осуществить общую задержку на 23 такта, в течение которых происходит исключение информации от дефектных регист- ров хранения. В общем устройство работает аналогично, как и при записи, только сдвиг единицы в регистре 1 происходит не справа налево, а слева направо. Информация, спустя 23 такта начинает поступать с выхода регистров 2 непосредственно на входы блока 21 .

При использовании блока 21 информация первоначально заносится в блок памяти, начиная с 24-го адреса. Затем она быстро считывается в процессор, начиная с 24-го адреса.

Формула изобретения

1. Устройство сопряжения процессора с памятью, содержащее первую и вторую группы сдвиговых регистров, первую, вторую, третью группы элемен тов И, счетчик, первый блок памяти, регистр, формирователь импульсов, выход которого соединен с первым входом каждого элемента И первой и второй групп, вход начальной установки каждого сдвигового регистра первой и второй групп соединен с входом начальной установки счетчика и является входом начальной установки устройства, вход формирователя импуль- сов соединен со счетным входом счетчика и является входом тактовых импульсов устройства, выход каждого элемента И первой группы соединен с

синхровходом соответствующего сдвигового регистра первой группы, выход каждого элемента И второй группы соединен с синхровходом соответствующего сдвигового регистра второй группы, выход каждого из разрядов К-го сдвигового регистра первой группы соединен с вторым информационным входом соответствующего разряда К-го сдвигового (где К , где М - разрядность блока памяти) регистра второй группы, выходы элементов И третьей группы являются информационными выходами устройства, а первый вход каждого элемента И третьей группы соединен с выходом соответствующего сдвиг гового регистра второй группы, информационный вход регистра соединен с выходом первого блока памяти, адресный вход которого соединен с выходом счетчика, отличающееся тем, что, с целью повышения достоверности функционирования, оно дополнительно содержит коммутатор, элемент НЕ, двунаправленный коммутатор, информационные входы-выходы которого являются информационными входами- выходами устройства, первая группа информационных входов коммутатора подключена к информационным входам устройства, а вторая группа информационных входов коммутатора соединена с выходами двунаправленного коммутатора, вход управления режимом которого соединен с управляющим входом коммутатора, входом элемента НЕ и является первым входом управления режимом обмена устройства, стробирующий вход двунаправленного коммутатора является входом разрешения работы устройства, выход элемента НЕ соединен с вторым информационным входом каждого сдвигового регистра первой группы первый информационный вход К-го сдвигового регистра второй группы подключен к К-у выходу коммутатора, первые информационные входы сдвиговых регистров первой группы подключены к nepBot-ty входу управления режимом обмена устройства, информационные входы двунаправленного коммутатора соединены с выходами сдвиговых регистров второй группы, вход управления приемом информации каждого сдвигового регистра первой группы является входом управления приемом информации устройства, второй вход каждого элемента И первой группы соединен с ин

версным выходом соответствующего разряда регистра, вторые входы каждого элемента И второй и третьей групп соединены с прямым выходом соответствующего разряда регистра, синхровход которого соединен с вхрдом тактовых импульсов устройства.

2. Устройство по п.1, от л и - чающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит четвертую группу элементов И, группу элементов ИЛИ и второй блок памяти, выходы которого подключены к информационным выходам устройства и соединены с информационными входами двунаправленного коммутатора, адресный вход второго блока памяти соединен с выходом счетчика, вход выборки второго блока памяти со

Редактор О,Головач Заказ 6000/50

Составитель М.Силин Техред Л.Сердюкова

Корректор Г.Р

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственио-псшиграфическое предприятие, г. Ужгород, ул. Проектная, 4

единен с входом тактовых импульсов устройства, вход чтения записи второго блока памяти является вторым входом управления режимом обмена устройства, первый вход каждого элемента И четвертой группы соединен с первым входом управления режимом обмена устройства, второй вход каждого элемента И четвертой группы соединен с выходом соответствующего сдвигового регистра второй группы, первый вход каждого э.лемента ИЛИ группы соединен с выходом соответствующего элемента И третьей группы, а второй вход каждого элемента ИЛИ группы соединен с выходом соответствующего элемента И четвертой группы, выход каждого элемента ИЛИ группы ёоединен с соответствующим разрядом информационногг входа второго блока памяти.

Корректор Г.Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357966A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357968A1 |

| Устройство для управления доменной памятью | 1985 |

|

SU1304076A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1352496A1 |

| Устройство для обхода дефектных регистров в доменной памяти (его варианты) | 1985 |

|

SU1305773A1 |

| Устройство для переадресации информации | 1981 |

|

SU1001177A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1989 |

|

SU1698907A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Устройство для управления обращением к памяти | 1985 |

|

SU1262494A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1152035A1 |

Изобретение относится к области вычислительной техники и может быть использовано в устройствах управления обменом процессора с памятью. Целью изобретения является повьшение достоверности функционирования и быстродействия. Устройство содержит сдвиговые регистры 1 и 2 групп, элементы И 3, 4, 5, 23 групп, счетчик 6, блоки 7, 21 памяти, формирователь 9 импульсов, двунаправленный коммутатор 12, коммутатор 10, элемент НЕ 11, элементы ИЛИ 22 группы, регистр 8. Цель изобретения достигается за счет введения режимов ускоренного считывания информации и обхода неисправных ячеек памяти. 1 з.п. ф-лы, 1 ил. (Л со ел со Р5

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Стеклорез | 1984 |

|

SU1248966A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1985-04-29—Подача