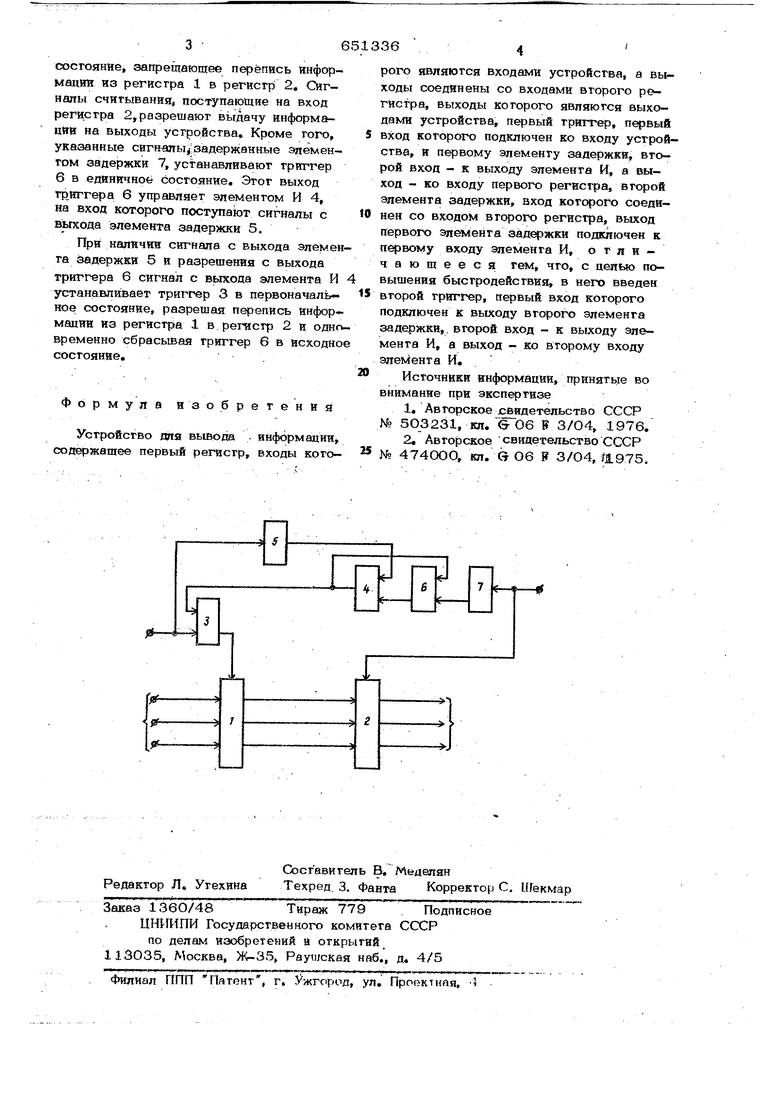

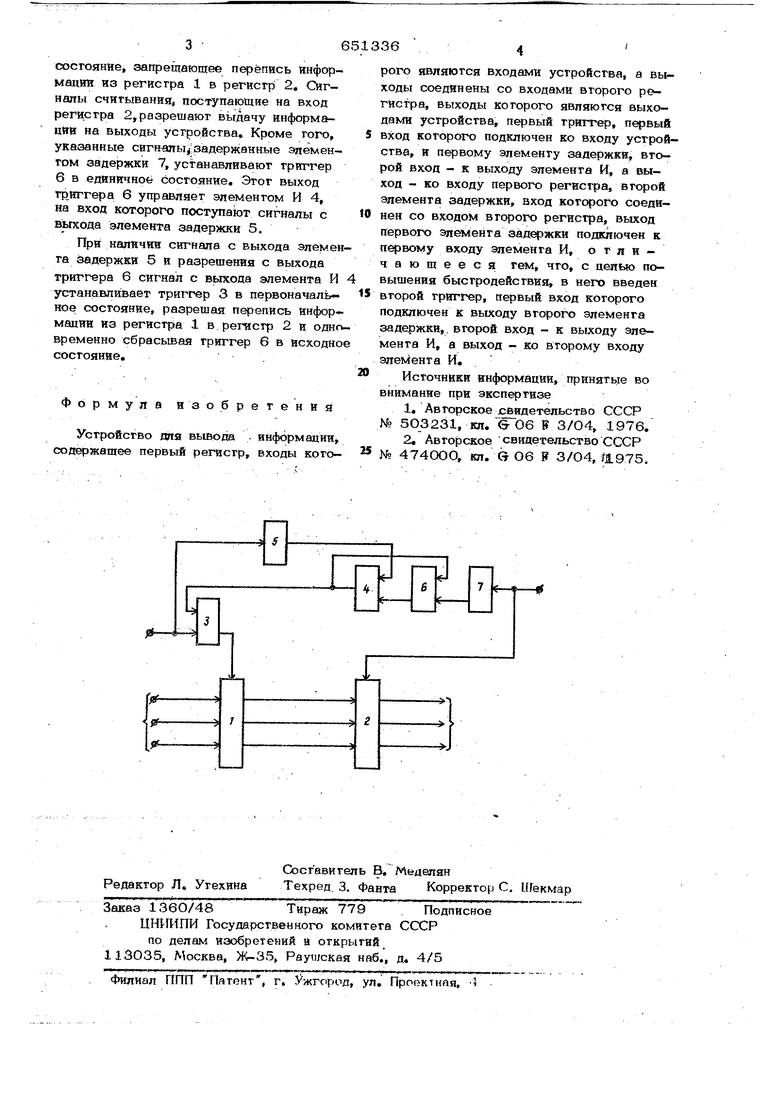

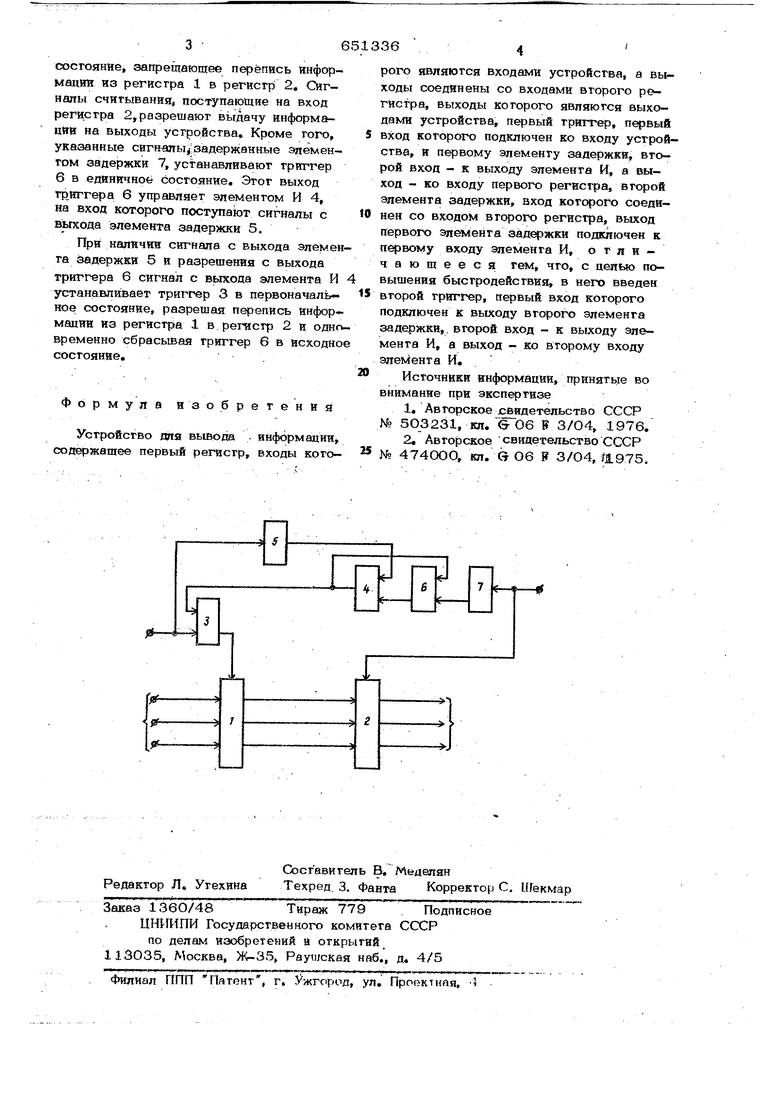

Изобретение огносигся к области вычислительной техники и предназначено для вывода информации с запоминающих устройств (ЗУ). Известно устройство для обмена информацией, содержащее ЗУ, согласующий регистр, буферный регистр и блок управления 1. Недостатком этого устройства являет ся низкое быстродействие. Наиболее близким но технической сущ ностн к изобретению является устройство отя вывода информации с ЗУ, содержащее первый регистр, входы которого являются входами устройства, а выходы соединены со входами второго регистра, выходы которого являются выходами уст ройства, первый триггер, первый вход которого подключен ко входу устройства н первому элементу задержки, второй вход - к выходу элемента И, а выход ко входу первого регистра, второй элемент задержки, вход которого соединен со входом второго регистра, выход первого элемента задержки подключен к первому входу элемента И 2. Целью изобретения является повыптение быстродействия устройства. Поставленная цель достигается тем, что в предложенное устройство введены втсрой триггер, первый вход которого подключен к выходу второго элемента задержки, второй вход - к выходу элемента И, а выход - ко второму входу элемента И. Структурная схема устройства представйена на черте.же. Устройство содержит регистр 1, второй регистр 2, первый триггер 3, элемент И 4, первый элемент задержки 5, второй триггер 6 и второй элемент задержки 7, Устройство работает следующим образом. Сигналы информации с ЗУ поступают на входы регистра 1, Одновременно тактовые сигналы поступают на элемент задержки 5 н устанавливают триггер 3 в сосгояние, запрещающее перепись информации из регистра 1 в регистр 2, Сигналы считывания, поступающие на вход регистра 2,разрешают выдачу информации на выходы усгройства. Кроме того, указанные сигналы задержанные элементом задержки 7, устанавливают триггер 6 в единичное состояние. Этот выход триггера 6 управляет элементом И 4, на вход которого поступаЬт сигналы с выхода элемента задержки 5. При наличии сигнала с выхода элемен та задержки 5 и разрешения с выхода триггера б сигнал с выхода элемента И устанавливает триггер 3 в первоначальное состояние, разрешая перепись информации из регистра 1 в регистр 2 и одно временно сбрасывая триггер 6 в исходно состояние,. Формула изобретения Устройство для вывода . информации, содфжашее первый регистр, входы которого являются входами устройства, а выходы соединены со входами второго регистра, выходы которого являются выходами устройства, первый триггер, первый вход которого подключен ко входу устройства, и первому элементу задержки, второй вход - к выходу элемента И, а вы:ход - ко входу первого регистра, второй элемента задержки, вход котороГ-о соединен со входом второго регистра, выход первого элемента задержки подключен к первому входу элемента И, отличающееся тем, что, с целью повышения быстродействия, в него введен второй триггер, первый вход которого подключен к выходу второго элемента задержки,, второй вход - к выходу элемента И, а выход - ко второму входу элемента И, Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 503231, кл. е 06 В 3/О4, 1976, 2. Ав торское свидетельство СССР № 474ООО, кл. От Об F 3/О4, fl975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Устройство для задержки импульсов | 1979 |

|

SU805483A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство для считывания информации с почтовых отправлений | 1982 |

|

SU1070579A1 |

| Устройство для сопряжения двух вычислитель-НыХ МАшиН | 1979 |

|

SU805296A1 |

| Устройство для снятия характеристик аналого-цифровых преобразователей | 1981 |

|

SU991600A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Устройство для вычисления функций синуса и косинуса | 1974 |

|

SU531161A1 |

| Устройство для вывода информации | 1981 |

|

SU991405A1 |

| Устройство для регистрациииНфОРМАции | 1979 |

|

SU849254A1 |

Авторы

Даты

1979-03-05—Публикация

1977-11-01—Подача