Изобретение относится к вычислительной и измерительной технике и может быть использовано в растровых преобразователях перемещения, напри мер, при контроле кинематической по грешности зубчатых колёс и передач. Известны устройства ( амплитудные интерполяторы ), работа которых заключается в амплитудной дискриминации взвешенных сумм синусоидаль ного и косинусоидального напряжений снимаемых с растрового датчика. Они делят квант шкалы (шаг растрового сопряжения) на определенное число, зависящее от числа дискриминаторов. Сложность таких устройств возрастает с увеличением коэффициента интер поляции (числа частей, на которые разбивается квант), поэтому для получения больших коэффициентов интер поляции используются различные аналоговые преобразования синусио-коси нусного двухфазного сигнала. Известно устройствоинтерполяции , выполняющее операции формирования модулей синуса .и косинуса, ум ножения полученных напряжений на коз|ффициенты, меньшие единицы, суммирования и вычитания результатов в различных комбинациях, дискриминации и логической обработки полученных сигналов, в результате чего получаются пять сигналов, образующих код Грея. Таким образом, в этом устройстве производится деление ква та на 32 участка D i Наиболее близким к изобретению по технической сущности являются поляторы фирмы bpton-Zeiss, имеющие коэффициенты интерполяции 4о и 80. Аналоговая часть этих интерполяторов формирует из синусно-косинусного сигнала три сигнала: сигнал в ви симметричной пилы и два разнополярных опорных напряжения, соответству ющие максимальному и минимальному напряжению пилы, Опорные напряжения поступают на два делителя напряжения , выходные напряжения которых сравниваются с симметричным пилообразным напряжением с помощью линейки компараторов. Еще три компаратора (в дальнейшем первый, второй и третий компараторы), используются для сравнения синусоидального, коси нусоидального и симметричного пилообразного напряжений с нулевым напряжением. Выходные логические сигналы компараторов имеют перепады (0/1 или 1/0), равномерно расположенные в 0 или 80 отсчетных точках на каждом шаге растров., С помощью дешифратора (комбинационной логической схемы) из этих сигналов формируются выходные сигналы в виде двух сдвинутых на четверть периода меандров, удобные для реверсивного счета. Изобретение описывается применительно к коэффициенту интерполяции 80 С2. . . Недостатком известных устройств является .сложность аналоговой части; в известном устройстве она содержит b операционных усилителей, имеющих 2-8 входных суммируемых сигналов. Целью изобретения ЯЕШяется упрощение устройства. Указанная цель достигается тем, что устройство для интерполяции аргумента гармонических функций, содержащее два блока формирования модуля, входы которых являются входами устройства, два резистивных делителя напряжения с h выходами каждый, первый и второй компараторы, неинвертирующие входы которых соединены с соответствующим входом устройства, а инвертирующиес шиной нулевого потейциала, третий компаратор, две группы по и компарат оров, при этом выходы первого резистивного делителя напряжения соединены с неинвертирующими входами соответствующих компараторов первой , группы, и дешифратор, соответствующие входы которого соединены с выходами всех компараторов, а первый и второй выходы являются выходами устройства, первый резистивный делитель напряжения включен между выходом первого блока формирования модуля и шиной нулевого потенциала, второй резистивный делитель напряжения включен между выходом второго блока формирования модуля и шиной нулевого потенциала, выходы второго резистивного делителя напряжения -соединены с инвертирующими входам .-(ростветствующих компараторов- второ группы, инвертирующие входы Tpflifj ero компаратора и компараторов первой группы подключены к выходу второго блока формирования модуля, неинве1ртирующие входы третьего компаратора и компараторов второй группи nof ключены к выходу первого блока формирования модуля.

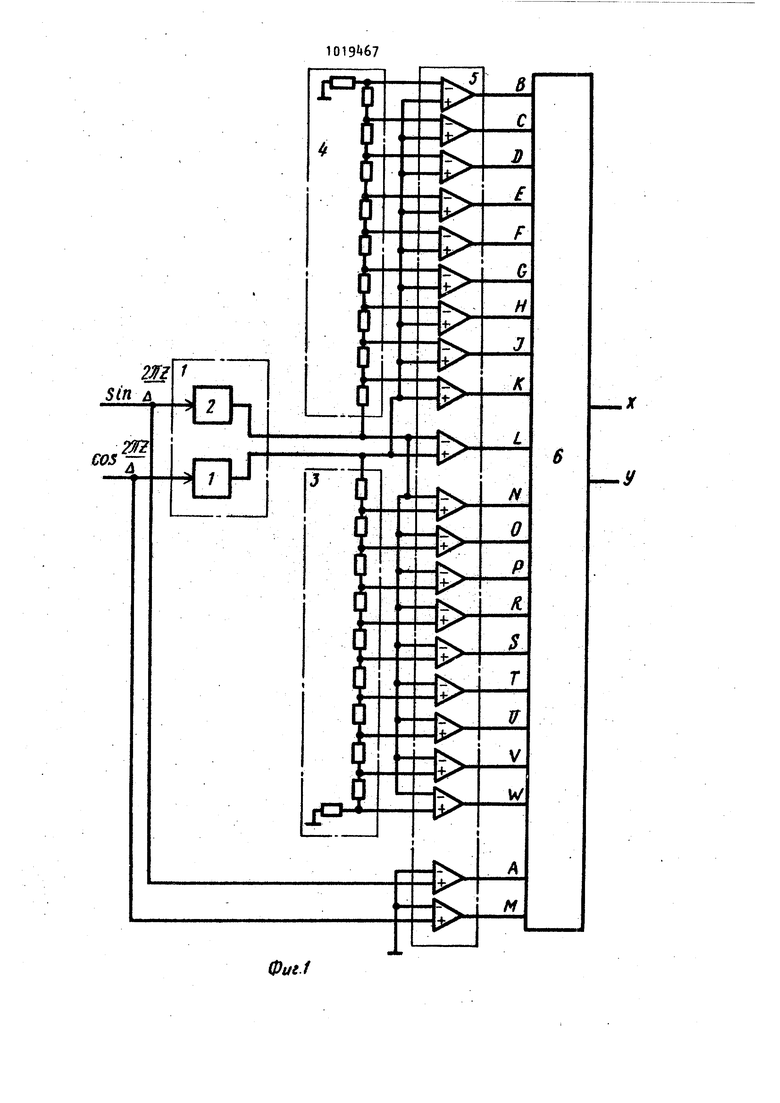

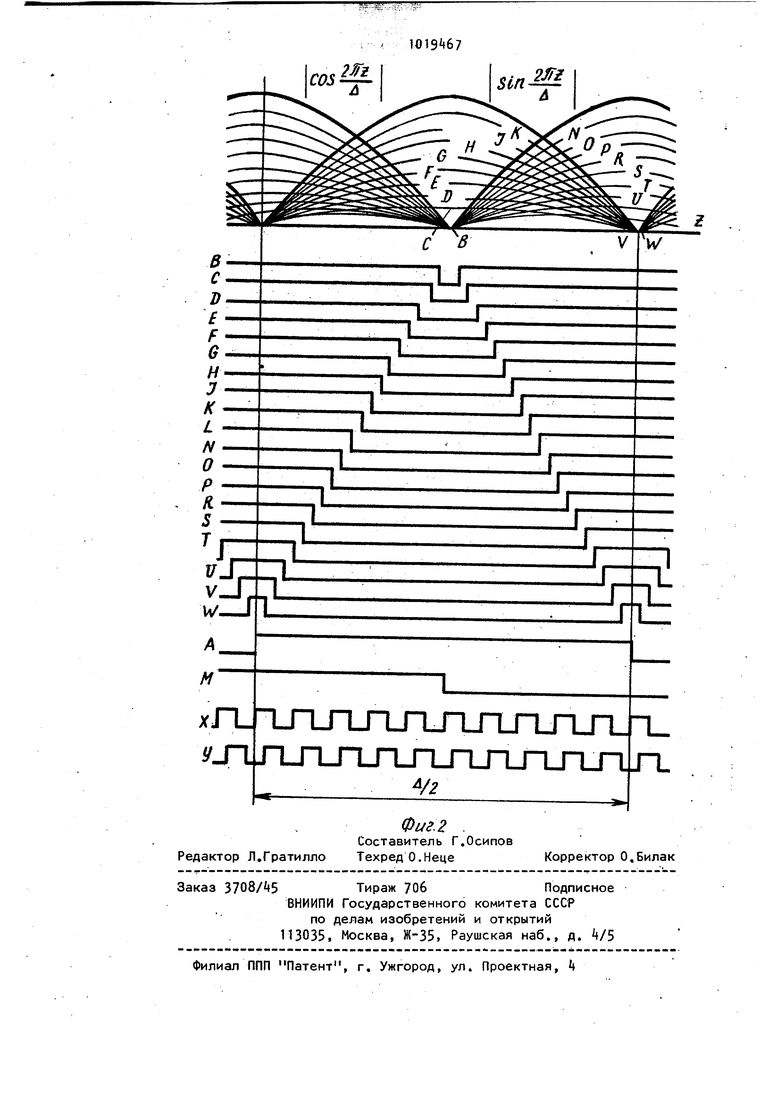

На фиг, 1 представлена схема устpoftcTBaJ на фиг. 2 - диаграмма напряжений.

Устройство содержит блоки 1 и 2 формирования модуля, резистивные делители 3 и напряжения, компараторы 5, дешифратор 6,

Устройство работает следующим обРа ом.«РУ

Двухфазный входной сигнал sIn cos2Л1. поступает на входы устройства (здесь

2 - йзЛ - квант шкалы,меряемое перемещение.

В линейке компараторов 5 производится сравнение между собой модулей входных сигналов и их долей, выделяемых делителями 3 и .

Порядок чередования перепадов выходных сигналов компараторов 5 Учитывается дешифрат эром 6, который формирует из 21 выходного сигнала линейки компараторов два выходных меандра X и у, сдвинутые на четвер5РЬ периода и имеющие в совокупности 80 перепадов в пределазк кванта ;шкалы. Для того, чтобы перепады выходных сигналов устройства интерполяции были распределены по кванту шкалы равномерно, необходимо определенным образом выбрать сопротивления делителей 3 и i напряжения.Перепады:выходного сигнала верхнего компаратора (фиг. 1) должны отстоять от находящегос между ними перепада сигнала на общем случае, На 4/т, где ткоэффициент интерполяции. Обозначив верхнее по схеме сопротивление в делителе k R, а суммарное сопротивление делителя - К,и прене- брегая нагрузкой на делитель напряжения со стороны компараторов, ус- ловия срабатывания компаратора в указанных точках можно записать, вид

С / . 1 /о 360°11

1. -)(,

откуда, задавшись из схемотехнических сообрак ений суммарным сопротивлением R, легко найти Я„ Аналогич- . но рассчитываются остальные сопро5тивления.

Таким образом, в известном устройстве входной аналоговый блок выполняет в общей сложности четыре операции формирования модуля и шесть 20 операций суммирования или вычитания напряжении, а в предлагаемом устройстве - только две операции формирования модуля, В связи с этим; число операционных усилителей в нем сокращается от 8 до i. Наряду с упрощением схемы достигается улучшение её качествеимых характеристик: в связи с уменьшением числа каскадно , включенных операционных элементов возрастает быстродействие, более равномерной становится нагрузка узлов, что приводит к уменьшению потребления, уменьшается динамический диапазон сигналов на входах компараторов, что повышает надежность. .

Фаг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор пилообразного напряжения с переменной крутизной | 1987 |

|

SU1495982A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 1987 |

|

SU1438439A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД ПАРАЛЛЕЛЬНОГО ТИПА | 1987 |

|

SU1454219A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1503072A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ИНТЕГРИРУЮЩЕГО ТИПА ДЛЯ ИЗМЕРЕНИЯ МАЛЫХ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 2018 |

|

RU2693647C1 |

| СЕНСОРНЫЙ ПЕРЕКЛЮЧАТЕЛЬ | 1990 |

|

RU2067354C1 |

| Устройство для вычисления алгебраических выражений | 1979 |

|

SU864298A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Рекурсивное вычислительное устройство | 1988 |

|

SU1522264A1 |

УСТРОЙСТВО ДЛЯ ИНТЕРПОЛЯЦИИ АРГУМЕНТА ГАРМОНИЧЕСКИХ ФУНКЦИЙ, содержащее два блока формирования модуля, входы которых являются входами устройства, два резистивных делителя напряжения с п выходами каждый, первый и второй компараторы, неинвертирующие входы которых соединены с соответствующим входом устройства, а инвертирующие - с шиной нулевого потенциала, третий компаратор, две группы по п компараторов, при этом выходы первого резистивного делителя напряжения соединены с нейнвертирующими входами соответствующих компараторов первой группы, и дешифратор, соответствующие входы которого соединены с выходами всех компараторов, а первый и второй выходы являются выходами устройства, о т л и ч а ю щ ее с я тем, что, с целью упрощения. Первый резистивный делитель напряжения включен между выходом первого блока формирования модуля и шиной нулевого потенциала, второй резистивный делитель наНряжения включен между выходом второго блока формирования модуля и шиной нулевого потенциала, выходы (Л второго резистивного делителя на пряжения соединены с инвертирующими входами соответствующих компараторов второй группы, инвертирующие входы третьего компаратора и компараторов первой группы подключены к выходу второго блока-формирования модуля, неинвертирующие входы третьего компаратора и компаратоS ров второй группы подключены к выхо4 ду первого блока формирования модуО) ля. 1

Авторы

Даты

1983-05-23—Публикация

1982-02-04—Подача