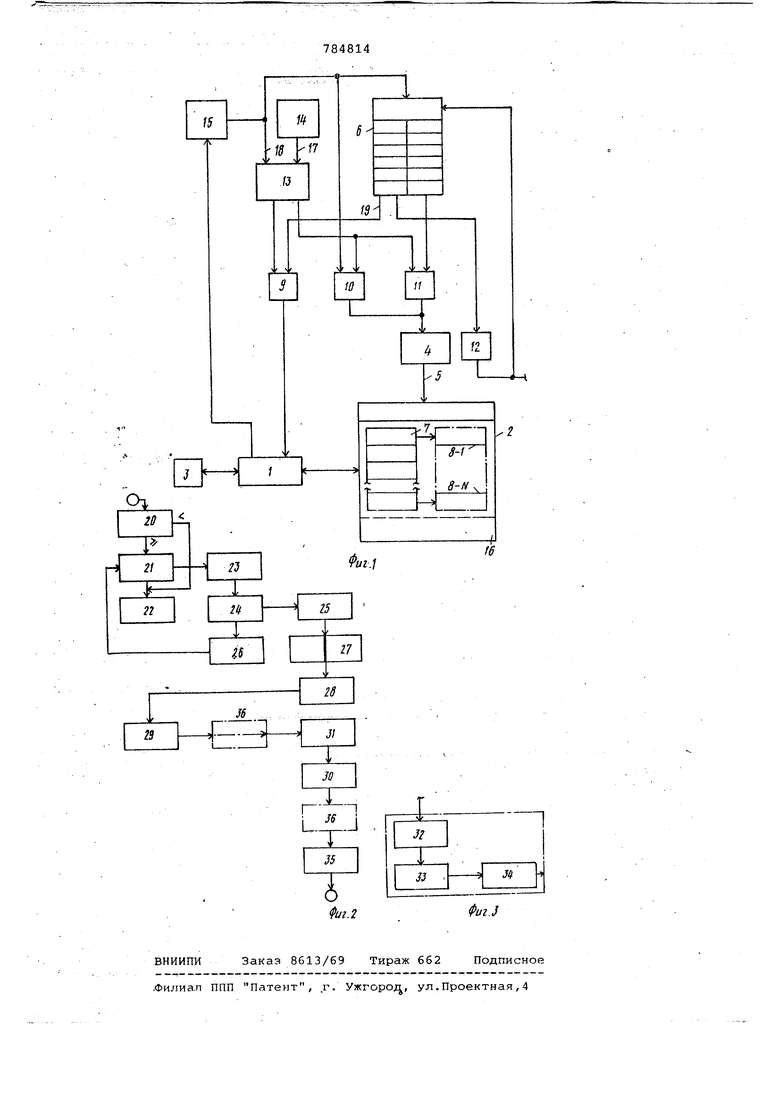

страничной обработки/ фиг. 3 иллгастр рует альтернативный метод для устано ления величины, которая может быть занесена в граничный регистр. Устройство для выбора адреса (см. фиг. 1) содержит логический блок 1, служащий для обработки данных; блок оперативной памяти 2, блок памяти на магнитных дисках 3, первый адресный регистр,4, служащий для хранения реального адреса и имеющий выход 5, блок ассоциативной памяти 6. Блок оп ративной пак.яти 2 содержит зоны 7, 8 называемые таблицей сегментов (7) и таблицами страниц (8-1 - 8-N). Устройство также содержит первую 9, вторую 10 и третью 11 группы логи ческих элементов, блок установки адр сов 12, схему сравнения 13, икформационный регистр 14, второй адресный регистр 15, служащий для хранения виртуального адреса. Бло: оперативной памяти 2 содержит также ядерную зону 16. Входы 17 и 18 схемы сравнения 13 подключены к выходам второго адресного регистра 15 и информационного регистра 14, а один из выходов к Одним из входов логических элементов ДО и 11. Одни из входов логичёскЦх элементов 9 соединены с первым выходом 19 блока 6. Другие входы логических элементов 9-11 подключена СОответ ственно к другому выходу схемы сравнения 13, выходу второго адресного регистра 15 и второму выхо ду блока 6. Выходьа логических элементов 10 и 11 соединены со входом первого адресного регистра 4. Устройство работает следующим образом. Когда требуется выбрать ячейку и блока 2 (см. фиг.1), то блок 1 пере даёт виртуальный адрес на схему сра нения 13 и блок б через -регистр 15. PefMCTp 14 хранит величину, равн старшим разрядам (величину страницы граничного адреса в блоке 2, ниже которого виртуальнвле и соответст.ву щие Им реальные адреса равны. Напри , ёслистраница равна двум тысяч бит, ТО нижние двенадцать бит стран адреса не хранятся в регистре Сетментная таблица 7 и страничные таблицы с 8-1 по 8-Н находятся в блоке 2. Таблица 7 имеет вход для к дого из Ы сегментов виртуальной пам ти вблоке 3. Каждглй вход имеет адр есйь1йуз :азатель начала сботвстству щей страницы таблицы с 8-1 по 8-W. Каждая страничная таблица имеет мно жество входов для страниц соответствуюи1его сегмента, который может б1тьть вызв.ан в блок 2 из блока 3. Ка дый вход действительной страничной га1эли 1Ы содержит в себе указатель начала стр1аницы в блоке 2. Сигнал с одного из врходов схёмы сранп.;7г1И1 13 с-Г1х-|Г)йруотс я .пёг-йЧески ми :.ч;;омгптлм1 ГО-ут.ля того, чтбРЫ пр пустить виртуальный адрес в регистр 4, когда старшие разряды виртуального адреса, подаваемого с блока 1, меньше, чем величина, храня1Г1аяся в регистре 14. Этот же сигнал поступает также в качестве запрещающего сигнала в логические элементы 11 для того, чтобы препятствовать передаче какогонибудь реального адреса из блока б в регистр 4, когда преобразование не требуется. Сигналы с логических элементов 9 необходимы для того, чтобы вести поиск таблиц 7 и с 8-1 до 8-N, когда сигналы прикладываются ко входам этих элементов. Сигналы подаются на входы логических элементов 9 тогда, когда текущий виртуальный адрес в регистре 15 больше или равен граничной величине в регистре 14 и не находится,в блоке 6. Блок 12 устанавливает новое значение виртуального и соответствующего реешьного адреса в блоке б. Более подробно работа устройства поясняется с помощью фиг. 2 и 3, ,Этапы 20-22 (см.фиг.2) представляют собой описанную выше работу устройства. Виртуальный адрес, который ,поступает из блока 1, сравнивается с величиной, хранящейся в регистре 14. Если виртуальный адрес меньше, чем граничный адрес, то блок 2 выбирается виртуальным адресом. Если виртуальный адрес больше или граничному адресу, то виртуальный адрес используется как аргумент поиска в блоке б. Ассоциативная матрица блока б зондируется для того, чтобы определить, содержит ли матрица виртуальный адрес и соответствующий ему реальный адрес. Если виртуальный адреснаходится в ассоциативной матрице, то ее реальный адрес используется для выборки блока 2. Если виртуального адреса нет в ассоциативной матрице, то контроль передается к этапу 23. На этапах 23, 24 блок 1 передает таблицы 7 и с 8-1 до 8-N в блок 2, например, с помощью микропрограммы для того, чтобы определить место требуемого реальногоадреса в таблицах. Если соответствующая страница имеется в блоке 2, то соответствующий ей реальный адрес будет найден в одной из таблиц с 8-1 до 8-N. Действительный бит в страничной таблице используется Для того, чтобы определить, является ли виртуальная страница действительной или нет, то есть находится ли она в блоке 2 И доступна ли для выборки. Если страница, не является действительной, то контроль передается на этап 25. В предлагаемом устройстве каяодый виртуальный адрес включает в себя сегментную часть, представленную самыми старшими разрядами адреса, страничную часть, пpeдcтaвлeнн K1 т1рг)межуточит 7ми разрядами, и словари и битовую часть, представленную младшими разрядами. Сегментная часть вир ального адреса вместе с сегментной .таблицей указателя начала (хранится регистре, который на фиг. 1-3 не показан) выбирает требуемый вход в таб лице 7. Страничная часть виртуальног сщреса и вход считывания таблицы 7 в время поиска на этапах 23-24 используется для выборки требуемого входа в выбранной таблице с 8-1 до 8-М. Выбранные табличные данные в одной из таблиц с 8-1 до 8-N имеют словарную часть виртуального адреса, связанного, к тому же, с соответствующим реальным адресом. Если страница действительная, то контроль передается наэтап 26, в ко тором виртуальный адрес и реальный адрес устанавливается в блоке б для контроля наименее недавно используемого адреса (с помощью блока 12). Блок 2 теперь мохсет быть выбран пере дачейсигналов блока 6. Передача контроля к этапу 25 опре деляется аппаратурой, обеспечивающей хранение виртуального адреса в ранее определенном месте в ячейках блока 2 Далее блок 1 выбирает новый директив ный адрес из другой ранее определенной зоны и начинает выполнение новог директивного действия в этапе 27. На этапе 27 страница в блоке 2 вы бирается для восстановления. Передач контроля далее осуществляется на эта пах 28 и 29, где табличная директива используется-для того, чтобы очистит (сбросить все битовые позиции до нуля) блок б с целью согласования анну лирования страницы, которая была заменена. Последующий этап 29 или взаимно исключающий последующий этап 30 пред ставленного устройства вызывает изме нение содержимого регистра 14. Этот процесс может или восстановить ранее определенную величину или сканировать страничные таблицы.Подача сигналов 1 и О,, необхр димая для ввода в требуемую страницу выполняется в этапе 31 и реальный ад рес запоминается на соответствующем входе страничной таблицы и делается действительным на этапе 30. Директивный адрес, запоминаемый на этапе 25, повторно загружается в блок 2 с инструкции загрузки и процесс возвращается к этапу 20. Этапы 32, 33 (см. фиг. 3) представляют собой г/1икропрограммный контур, который начинается при нулевом виртуальном адресе в страничных таблицах и осуществляет установку реального адреса в виртуальный адрес, т.е реальный адрес считывается и сравнивается с виртуальным адресом для проверки 5.1авенства. Кслй виртуальный акPGC pnric 1)са.пыюму a,i;pecy, то виртуальиы ллро: (пашегсч ггрнращоннем страничного размера и контур cF-ова сравнивает следующую виртуальную страничную таблицу входа адреса с реальным адресом, хранящимся в табличных данных. Это повторяется до тех пор, пока виртуальный адрес не станет равным установленному реальному адресу или пока не произойдет переполнение регистра 15. На этапе 34 самая большая величина виртуального адреса, появиви1аяся в этапах 32 и 33, поступает в регистр 4, как граничный адрес в блоке 2. В типовом устройстве этапы, представленные позициями 27, 28, .31, 30 и 35 (и, возможно, 36) выполняются методом директивных подпрограмм. В описанном устройстве в противоположность известному устройству производится преобразование не всех виртуальных адресов. Опроделен)ые виртуальные адреса используются для обращения к блоку оперативной памяти непосредственно, без преобразования. Указанные адреса соответствуют ячейкам памяти, к которым часто обращаются. Обращение к таким ячейкамзанимает меньше времени, так как не требуется преобразования адреса. Таким образом, удается получить общее повышение быстродействия, равное 15-25%, Формула изобретения Устройство для выбора адреса, содержащее блок оперативной памяти, один из входов которого подключен к выходу первого адресного регистра, второй адресный регистр, выход которого соединен со входом блока ассоциативной памяти, первую группу логических элементов, одни из входов которых подключены к Первому выходу блока ассоциативной памяти, а выходы - ко входу логического блока, соединенного со вторым адресным регистром и с блоком оперативной памяти, о т л и ч а iщ е е с я тем, что, с целью повышени быстродействия устройства, оно содегг жит вторую и третью группы логически; элементов, информацио(Ный регистр и схему сравнения, которой подклг чены к выходам второго адресного регистра и информационного регистра, .а выходы - к одним из входов логических элементов второй и третьей групп, выходы которых соединены со входом первого адресного регистра, другие входы логических элементов подключены соответственно к выходам cxeMij сравнения, второго адресного регистра и второму выходу блока ассоциативной памяти. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3412382, кл. 340-172.5, опублик. 1968. 2.Патент ШЛ № 353307S, кл. 340-172.5, опу|Л1 к. 1.470 (прототип ) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Устройство для динамического преобразования адреса | 1983 |

|

SU1124300A1 |

| Устройство управления виртуальной памятью | 1980 |

|

SU1023336A1 |

| Устройство для управления виртуальной памятью | 1986 |

|

SU1327113A2 |

| СПОСОБ ФОРМИРОВАНИЯ ВИРТУАЛЬНОЙ ПАМЯТИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2011 |

|

RU2487398C1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Устройство для трансляции логических адресов в адреса памяти на магнитных дисках | 1981 |

|

SU966695A1 |

| Связанное с выбранными архитектурными функциями администрирование обработки | 2015 |

|

RU2665243C2 |

| Устройство для динамического преобразования адреса | 1985 |

|

SU1265771A1 |

| Устройство динамического преобразования адресов | 1978 |

|

SU765805A1 |

Авторы

Даты

1980-11-30—Публикация

1973-06-20—Подача