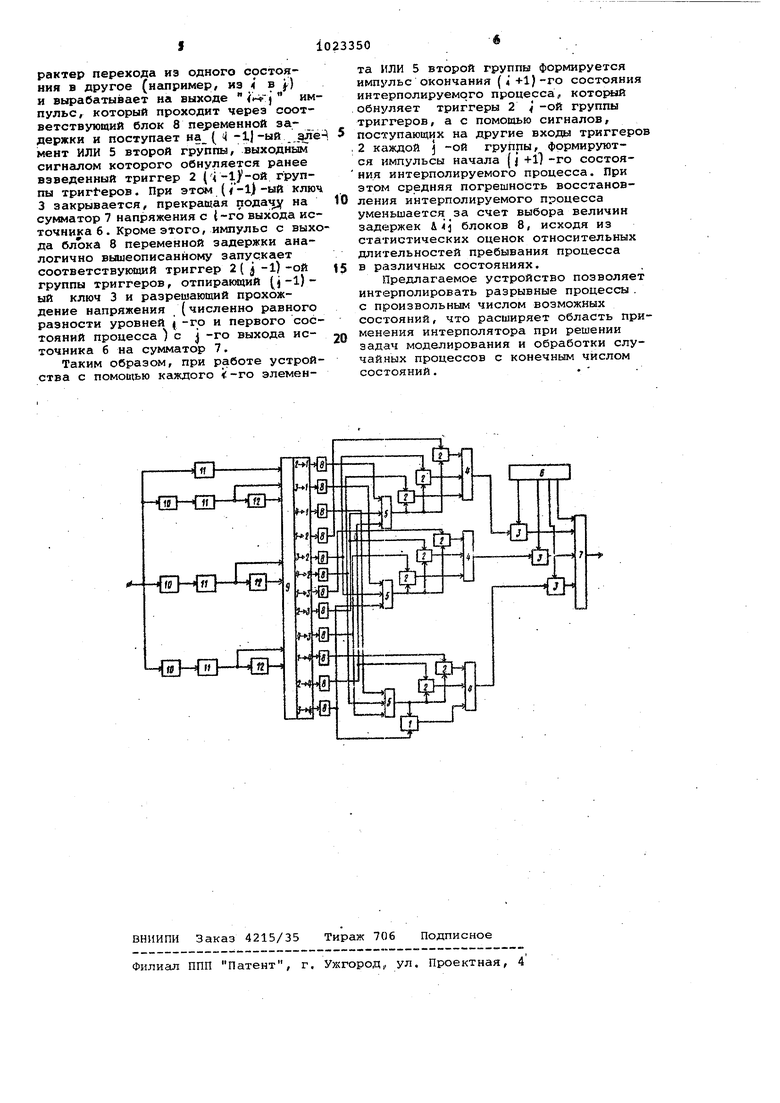

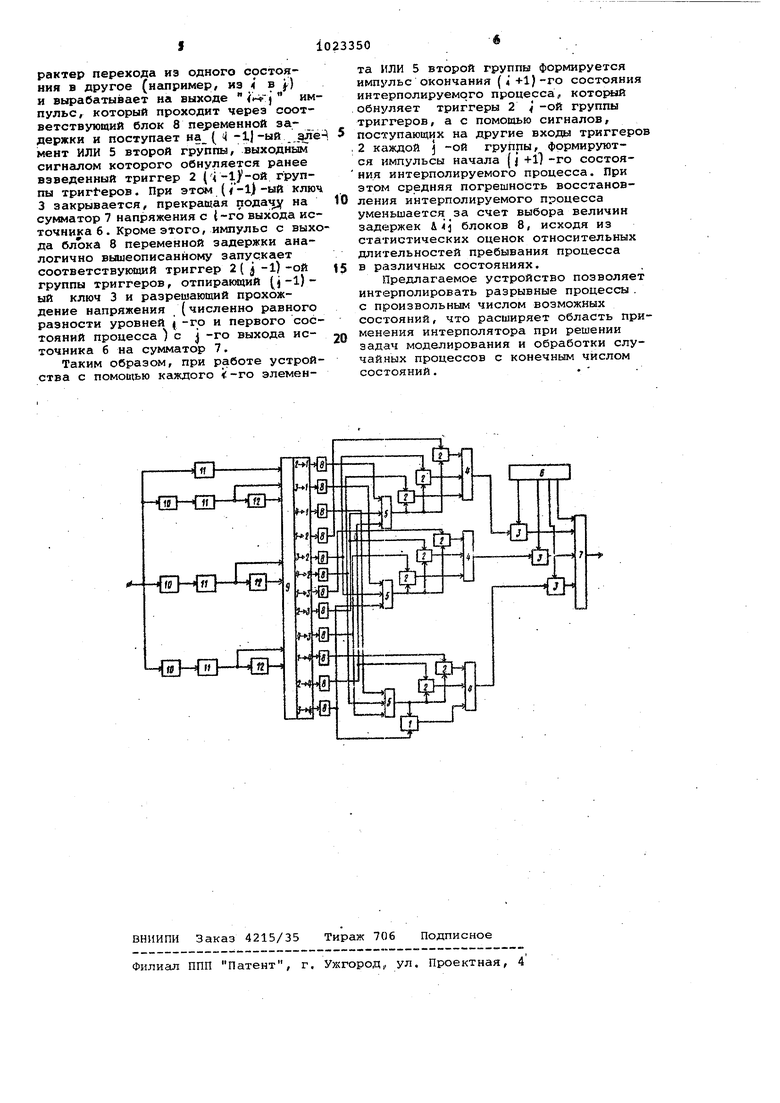

Изобретение относится к автомати ке и вычислительной технике и может найти применение, в частнооти, для восстановления реализаций разрывных случайных процессов. Известны интерполяторы разрывных процессов, содержйцие операционные .усилители, работаюшие в режиме выбо ки-хранения tl3 . ; Недостатками известных интерполя торов являются ограниченная крутизна восстановления процесса в.точках разрыва, а также пониженные помехоустойчивость и стабильность, Наиболее близким к предлагаемому является устройство для интерполяции разрывных процессов, содержашее блок постоянной задержки, ключ, два блока переменной задержки и триггер подключенный первым входом к выходу первого блока переменной задержки, выходом - к выходу устройства, а вторым входом - к выходу второго блока переменной задержки, соединенного входом с выходом ключа, под ключенного сигнальным входом к вход устройства, входу второго блока переменной задержки и к входу блока постоянной задержки/ а управляющим входом - к выходу блока постоянной задержки 2 . Недостатком известного.устройств является ограниченная область применения , так как оно может быть использовано , при восстановлении разрывных процессов только с двумя воз можными состояниями бинарных процессов . Цель изобретения - расширение об ласти применения устройства за счет интерполяции процессов с произвольным числом состояний. Поставленная цель достигается тем, что в устройство для интерполя ции разрывных процессов, содержащее блок постоянной задержки, ключ. Два блока переменной задержки и триггер подключенный первым входом к выходу первого блока переменной задержки, дополнительно введены N-1 (где N число возможных состояний интерполи руемого процесса) группа триггеров по (N-l)-My триггеру в первых(N-2)группах и N-2 триггера в (N-l)-oй группе, N - 2 ключей, две группы по N - 1 -му элементу ИЛИ, источник опорных напряжений, rN{N-l)-2j блоков переменной задержки, дешифратор переходов, N-1 пороговых элементов, N ограничителей, N - 2 блоков постоянной задержки и выходной сумматор, соединенный входгини с первым выходом источника опорных напряжений и с выходами всех ключей, каждый 1-ый (lil N - 1) из которых подключен сигнальным входом к(i + 1)-му выходу источника опорных напряжений, а управляющим входом - к выходу I-го элемента ИЛИ первой группы, соединенного входами с выходами триггеров t-ой группы, подключенных первыми входами к выходу {-го элемента ИЛИ второй группы, первый вход которого соединен через (+ 1)гый блок переменной задержки с выходом перехода процесса из ( I + 1)-го в первое состояние дешифратора переходов, подключенного выходом перехода процесса иэ первого в (+1)-ое состояние через (N « 1)-ый блок переменной задержки к второму входу первого триггера 1-ой группы, каждый J-ый (2i-|sN-1.) триггер которой соединен вторым вхог дом с k-ым ( при j;k« + 1 при i- t) входом t-ro (t«j при , при j 1) элемента ИЛИ второй группы и через 5 ( М-1) + ( +lj-ый блок переменной задержки ггс- выходом перехода процесса из { 6 -1) -го в ( +1)-ое состояние дешифратора переходов , подключенного первым входом через первый ограничитель к входу устройства, каждым ( +1)-ым входом - к выходу 4-го блока постоянной задержки, а каждым 2 -ым входом к входу сл -го блока постоянной задержки и к выходу(1+1)-го ограничителя, соединенного входом через -ый пороговый элемент с входом устройства, причем первый блок переменной задержки подключен входом к выходу перехода процесса из(К-1)-го в N-ое состояние дешифратора переходов, а ОСНОВНОЙ триггер подключен вторым входом и выходом соответственно к ВЫХОДУ { N-1) -го элемента ИЛИ второй группы и к (N-I) -му входу(-1) Io элемента ИЛИ первой группы. На чертеже изображена блок-схема устройства ДЛЯ интерполяции разрывных процессов (для случая N 4). -ч - , 1 Устройство содержит триггер 1, N- 1 (где Н - число возможных состояний интерполируемого процесса) группу триггеров 2 no(N-l) -му триггеру в первых(Н-2)-X группах и N-2 триггера в(М-1)-ой группе, N-1 ключей 3, первую группу из fN-1)-го элементов ИЛИ 4, вторую группу из. { N - l) -го элементов ИЛИ 5, источник б опорных напряжений, выходной сумматор 7,N (М- 1) блоков 8 переменной задержки, дешифратор 9 переходов, N - 1 пороговых элементов 10, К ограничителей 11 и N -1 блоков :12 постоянной задержки. Триггер 1 подключен к выходу первого бябка 8 переменной задержки. Выходной сумматор 7 соединен входами с первым выходом источника 6 опорных напряжений и с выходами ключей 3, каждаай -ый (li и N-I) из которых подключен сигнальным входст к ( ) МУ выходу источника 6, а управляющим

входом - к выходуf-го элемента ИЛИ

4первой группы, соединенного входами с выходами триггеров 2 -ой группы. Триггеры 2 i-ой группы подключены к выходу -го элемента ИЛИ 5 второй группы,, соединенного первым входом через ( 4 +1)-ый блок 8 переменной задержки с выходом i+l- l перехода процесса из {4+1)-го в первое состояние дешифратора 9 переходов. Выход перехода процесса из первого в -| +1) -о§ состояние дешифратора 9 подключен через (|N+) -ый блок 8 переменной задержки к второму входу первого триггера

2 -ой группы. Каждый -ый. j М триггер 2 i-ой группы соединен вторым входом с k -ым (к 4 при 1 , U +1 при ; :. j входом f -го (2 j при j ; j -1 при)1) элемента, ИЛИ

5второй группы и через з {N-1) + f -fllый блок 8 переменной задержки - с выходом Е + 1- 1 + 1 перехода процесса из ( и+1)-го в(ц+1)-ое состояние дешифратора 9. Дешифратор 9 подключен первьвм входом через первый ограничитель 11 к входу устройства, каждым 2 -i +1) -ым входом - к выходу i -го блока 12 постоянной задержки, а каждым 2 -ым входом - к входу i-ro блока 12 постоянной задержки

и к выходу (4+1) -го ограничителя 11, соединённого входом через -ый пороговый элемент 10 с входом устройства. Первый блок 8 переменной задержки п одк люче н в ходом к. .вых оду N -1-- Н перехода процесса из N -1) -го в N-ое состояние дешифратора 9, а триггер 1 подключен вторым входом и выходом соответственно к выходу { Н-1) -го элемента ИЛИ 5 второй группы и к(И-1)-м входу|Ц-1 -го элемента ИЛИ 4 первой группы, т.е. по JtapaKTepy своих связей с другими узлами , триггер 1 представляет собой(М-1) -ый триггер{1Ч-1) Ой группы триггеров 2 устройстга .

Устройство для интерполяции работает следующим образом.

На вход устройства поступает периодическая последовательность импульсов с различными значениями амплитуд, представляющих собой дискретные отсчеты реализации случайного разрывного процесса с ненулевым средним значением, таким, что наименьшее из значений разрывного процесса (соответствующее его первому состоянию) является положительной величиной. Последовательность OTCieтов поступает на вход первого из ограничителей 11 и входы пороговкк эле: ментов 10. Величина: ограничения в первом ограничителе 11 выбран а ран ной величине амплитуды наименьшего из входных импульсов,так что на выходе этого ограничителя формируется периодическая последовательность и 5пyльсов. Эта последойательность является синхронизирующей для дешифратора 9 переходов. Величины порогов в пороговых элементах 10 выбраны таким образом, чтобы на их выходы прохОДИ ли импульсы/ амплитуды которых сООФ ветствугот состояниям проЦвОса с tl®« мерами, равными или большиЙИ, чем номер порогового элемента плюс еДН ница. Например, на выход (N-1)-го порогового элемента 10 проходят иМ пульсы с амплитудой, соответствующей N-му состоянию процесса. На выход (N-2) -го порогового элемента 10 проходят импульсы с амплитудами, соответствующими (N-1) -му и N-му состояниям процесса и т.д.

-. г . ,

С выходов пороговых элементов 10 импульсы проходят через соответствукнцие ограничители 11, где норми- руются по ампдитуде. Затем они поступают на четные входы дешифратора 9 переходов непосредственно, а на нечетные входы - после задержки в блоках 12 на интервал дискретизации. По сочетанию нулевых и единичных сигналов, поступающих на входы д 1тфратора 9, последний определяет характер перехода процесса, происшед« шего во входной последовательности за предыдущий интервал дискретизации Если сочетание импульсов на входах дешифратора 9 соответствует переходу в интерполируемом процессе из состряния i в состояние (где lfN , i 1,N , i), то дешифратор 9 вырабатывает импульс на соответствую,шем выходе перехода .J - i . Этот импульс, пройдя через соответствующий блок 8 переменной задержки на время А j ч, меньшее чем интервал дискретизации, запускает соответствующий триггер .2 ( -1) -ой группы триггеров. Напряжение с выхода триггера через (-1)-ый элемент ИЛИ 4 первой группы элементов ИЛИ поступают иа управляющий вход(1-1) -г ключа 3 и отпирает его. При этом с источника б на соответствующий вход сумматора 7 начинает поступать напряжение, равное разности уровней . и первого (наименьшего),состояний интерполируемого процесса. Поскольку напряжение уровня первого состояния процесса поступает на пер.вый вход сумматора 7 постоянно, то выходной сигнал сумматора оказывается равным уровню i -го состояния процесса. ,

Если следующий отсчет, поступающий на вход устройства, имеет ту же амплитуду, что и предыдущий, то дешифратор 9 определяет отсутствие скачка на интервале дискретизации 1И нэ вырабатывает на выходе импульса. Если же новый отсчет имеет ам плитуду, отличную от предыдущего, то деишфратор 9 устанавливает характер перехода из одного состояния в другое (например, из в J.) и вырабатывает на выходе -

(- j импульс, который проходит через соответствующий блок 8 переменной задержки и поступает на ( але мент ИЛИ 5 второй груЪпы, выходным сигналом которого обнуляется ранее взведенный триггер 2 ()-ой группы TpHrt-epoB. При этом (i-l) -ый ключ 3 закрывается, прекращая подачу на сумматор 7 напряжения с 1-го выхода источника 6. Кроме этого, импульс с выхо да блока 8 переменной задержки аналогично вышеописанному запускает соответствующий триггер 2(з-1)-ой группы триггеров, отпиракяций у-1)ый ключ 3 и разрешающий прохождение напряжения (численно равного разности уровней j -го и первого состояний процесса ) с -го выхода источника б на сумматор 7.

Таким образом, при работе устройства с помощью каждого if -го элемента ИЛИ 5 второй группы формируется импульс окончания (4+1)-го состояния интерполируемого процесса, который обнуляет триггеры 2 i -ой группы триггеров, а с помощью сигналов, поступающих на другие входы триггеро ,2 каждой -ой группы, формируются импульсы начала (j +ll -го состояния интерполируемого процесса. При этом средняя погрешность восстановления интерполируемого процесса уменьшается за счет выбора величин зад 2ржек блоков 8, исходя из статистических оценок относительных длительностей пребывания процесса в различных состояниях.

Предлагаемое устройство позволяет интерполировать разрывные процессы . с произвольным числом возможных состояний, что расширяет область применения интерполятора при решении задач моделирования и обработки случайных процессов с конечным числом состояний.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения сопротивления до места короткого замыкания линии электропередачи | 1979 |

|

SU879504A1 |

| Устройство для вычисления непрерывно-логических функций | 1989 |

|

SU1695289A1 |

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОГО МОДЕЛИРОВАНИЯ СОСТОЯНИЯ ОБЪЕКТА ИСПЫТАНИЙ | 1991 |

|

RU2010323C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| Устройство для контроля параметров | 1979 |

|

SU842721A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1999 |

|

RU2153699C1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2503993C1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1999 |

|

RU2152072C1 |

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

УСТРОЙСТВО ДЛЯ ИНТЕРПОЛЯЦИИ РАЗРЫВНЫХ ПРОЦЕССОВ,солержаю.ее блок постоянной задержки, ключ, два блока переменной задержки и триггер, подключенный первым входом , к выходу первого блока переменной задержки, о тл ич. ающ ее с я тем, что, с целью расширения области применения устройства за счет интерполяции процессов с произвольным числом состояний, в него дополнительно введены N -1 (где N - число возможных состояний интерполируемого процесса) групп триггеров по { Ц -1) му триггеру в первых ( группах и 14-2 триггера в ( N -1) -и группе, ключей, .две группы поfj-i элементов ИЛИ, источник опорных напряжений, tj (N- 1) - 2 блоков переменной задержки, деигифратор переходов, N - 1 пороговых элементов , N ограничителей, N - 2 блоков постоянной задержки и выходной сумматОр, соединенный входами с первым выходом источника опорных напряжений и с выходами всех ключей, каждый -и

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Корн Г., Корн Т | |||

| Электронные аналоговые и аналого-цифровые вычислительные машины | |||

| М., Мир, 1968, т | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 756425, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-15—Публикация

1981-11-19—Подача