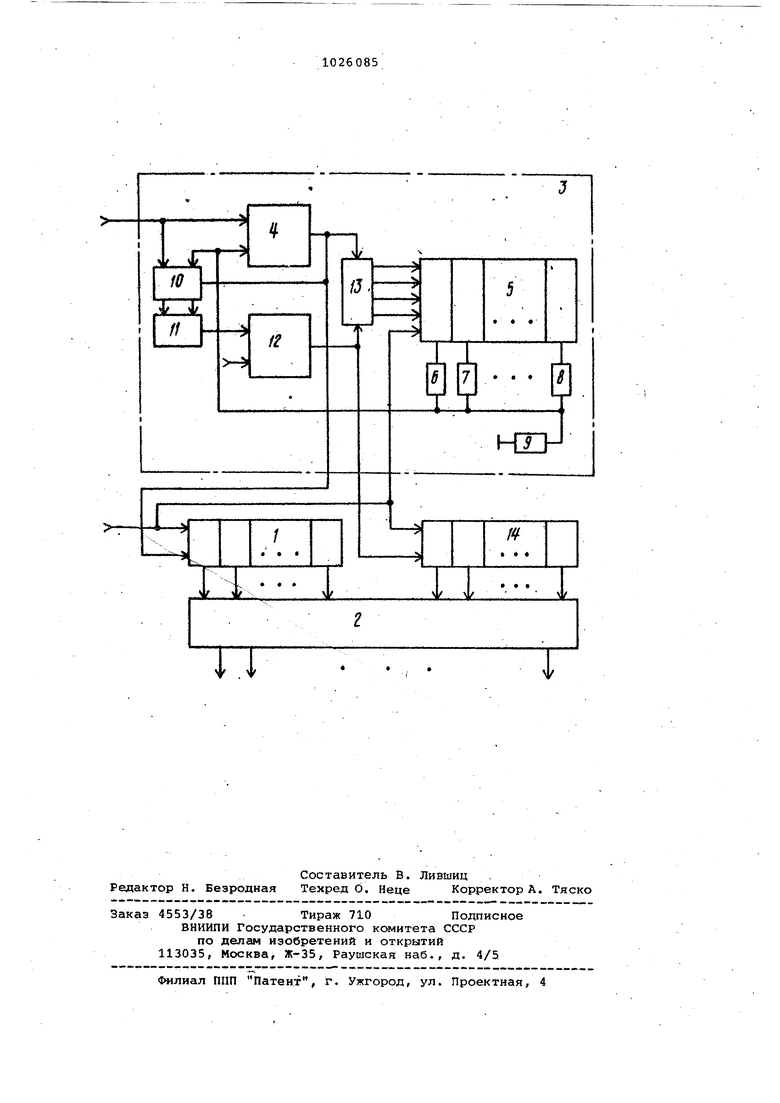

Изобретение относится к электроизмерительной технике и может быть использовано в системах передачи да ных по каналам связи, а также в уст ройствах дистанционного контроля и управления. Известен анализатор формы электрического сигнала, содержащий дельта-модулятор, сдвиговый регистр, де шифратор, блок автоматической регулировки усиления и дискриминатор спектра сигнала l . Недостаток известного устройства состоит в низкой разрешающей способности. Наиболее близким к предлагаемому по технической сущности является анализатор формы электрического сигнала, содержащий первый дешифраTol5, входы которого соединены с раз рядными выходами первого cдвигoвqго регистра, и дельта-модулятор, состоящий из второго сдвигового регистра, весовых и суммирующего резисторов и первого компаратора, первый вход которого подключен в шине входного сигнала, выход - к управляющему входу первого сдвигового регистра и информационному входу второго сдвигового регистра, а второй вход - к первому выводу суммирующего резистора и вторым выводам весовых резисторов, первые выводы которых связаны с разрядными выходами второго сдвигового регистра, тактирующим входом соединен ного с тактирующим входом первого сдвигового регистра и шиной тактового сигнала, причем второй вывод суммирующего резистора подключен к общей шине 2 . Недостатком такого устройства является низкая разрешающая способность, обусловленная тем, что аппро симирующее напряжение в каждом такте может изменяться только на заранее фиксированную величину и U того или иного знака. Цель изобретения - повы1иение раз решающей способности. Указанная цель достигается тем, что анализатор формы электрического сигнала, содержащий первый дешифратор, входы которого соединены с раз рядньоми выходами первого сдвигового регистра, и дельта-модулятор, состоящий из.второго сдвигового регист ра, весовых и суммирующего резисторов и первого компаратора, первый вход которого подключен к шине вход ного сигнала, выход - к управляющему .входу первого сдвигового регистра, а второй вход - к первому выводу суммирующего резистора и вторым выводам весовых резисторов, первые выводы которых связаны с разрядными выходами второго сдвигового регистра, тактирующим входом соединенного с тактирующим входом первого сдвигового регистра и шиной тактового сигнала, причем второй вывод суммирующего резистора подключен к общей шине, снабжен аналоговым ВЕаГчитающим блоком, вторым компаратором, вторым дешифратором, третьим сдвиговым регистром и коммутатором, первый и второй сигнальные входы которого связаны с входами первого компаратора, управляющий вход - с выходом первого компаратора, а пер- вый и второй выходы - с первым и вторым входами аналогового, вычитающего блока, выходом соединенного с ( первым входом второго компаратора, второй вход которого подключен к шине постоянного напряжения, а выход - к управляющему входу третьего сдвигового регистра и второму входу второго дешифратора, первый вход которого связан с выходом первого компаратора, а выходы - с управляю- щими входами второго сдвигового регистра, причем тактирующий вход третьего сдвигового регистра соединен с шиной тактового сигнала, а разрядные выходы - с входами первого дешифратора. На чертеже Показана структурная электрическая схема устройства. Устройство состоит из первого сдвигового регистра 1, первого дешифратора 2, дельта-модулятора-3, включающего первый компарат ор 4, второй сдвиговый регистр 5, весовые резисторы 6-8, суммирующий резистор 9, коммутатор 10, аналоговый вычитающий блок 11, второй компаратор 12, второй дешифратор 13, и третьего сдвигового регистра 14. Сдвиговый регистр 5 имеет четыре различных режима работы: сдвиг вправо на один разряд) сдвиг вправо на два разрядаf сдвиг влево на один разряд; сдвиг влево на дв-а разряда. Режим работы регистра 5 определяется тем, на какой из его управляющих входов подан единичный сигнал с выхода дешифратора 13, т.е. выходными сигналами компараторов 4 и 12.. Коммутатор 10 обеспечивает постоянство знака разности, формируемой блоком 11, меняя местами уменьшаемое и вычитаемое, если вычитаемое оказывается больше уменьшаемого, т.е. напряжение на выходе блока 11 равно r(t) /UBX (t) - Ua CtV, где Ug(t) - сигнал на входной шине устройства; U(jf(t) - аппроксимирующий сигнал, формируемый устройством на резисторе 9. Устройство работает следующим образ см. В исходном состоянии первый и третий регистры 1 и 14 установлены в нуль, в первом разряде второго ре гистра 5 установлена единица, в остальных его раэряадах - нули, на пер вом входе компаратора 4 присутствуе входной сигнал, на втором - аппроксимирующий сигнал, определяемый соотношением сопротивлений резисторов 6 и 9. При сдвиге содержимого регистра 5 на один разряд вправо (в этом регистре в единичном состоянии всег да находится только один из его раз рядов) напряжение на втором входе компаратора 4 возрастает на величин ли, а при сдвиге влево на один раз ряд уменьшается на величину Д U. Пр этом величина д U на каждом шаге определяется соотношением сопротивлений весовых и суммирующего резисторов. Единичный игнал на выходе компаратора 4 присутствует в случае, если и-бк (t) Uan(t),(1) а на выходе Компаратора 12/ если rCt)1,5AU(2). Пусть в момент поступления первого тактового импульса выполняется условие (1) и не выполняется условие (2) . Тогда тактовь1й импульс переместит единицу, содержавшуюся в первс разряде регистра 5, во второй его разряд} кроме того, это импульс сдвинет содержимое регистров 1 и 14 на один разряд вправо и запишет единицу в первый разряд регистра 1 (так как на его управляющем входе присутствует единичный сигнал). Пусгть входной сигнал резко увеличился так, что несмотря на уйе.личенйе аппроксимирующего сигнала на величину ди, обусловленное указанным сдвигом содержимого регистра 5, к моменту поступления второго тактового импульса оба условия (1) и (2) оказываются вштолненньтми, т.е. UBX (tj) - Uan ft) 1 ,5 Л U. ВЭтсм случае тактовый импульс сдвинет содержимое регистра 5 на два разряда вправо, т,е. аппроксимирующий сигИал увеличится на 2 Д U. Этот же тактовый импульс снова сдвинет на один разряд вправо содержимое регистров 1 и 14 и запишет единицу в их первые разряды. Диалогично, если выполняется условие (2)|И не выполняется условие (1) осуществляется сдвиг со;держимого регистра 5 на два разряда влево, т.е. напряжение 11 (t) уменьшается на 2 д и, при этом записывается единица в первый разряд регистра 14 (содержимое регистров 1 и 14 сдвигается вправо на один разряд каждым тактовым импульсом), если не выполняются оба условия (1) и (2), то содержимое регистра 5 сдвигается на один разряд влево, т.е. Uj,f, (t) уменьшается на д U при этом едини ха в первые разряды регистров 1 и 14 не записывается. Кодовая комбинация, образуемая состояниями разрядов регистров 1 и 14, однозначно определяет форму напряжения ступенчатого вида--1 ап Ct), которое аппро,ксимирует входной сигнал. Устройство формирует в каждом такте значения двух разрядов выходной кодовой комбинации, т.е. может различить 2 различных входных сигнала иньами словами, его разрешающая способность увеличивается в 2 раз,, а быстродействие не. изменяется..

i.i

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор формы сигнала | 1978 |

|

SU741197A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Устройство для нормализации чисел | 1980 |

|

SU953636A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

АНАЛИЗАТОР ФОРМЫ ЭЛЕКТРИЧЕСКОГО СИГНАЛА, содержащий первьМ дешифратор, входы которого соединены с разрядными выходами первого сдвигового регистра, и дельта-модулятор, состоящий из второго сдвигового регистра, весойУх и суммирующего резисторов и первого компаратора, первый вход которого подключен к шине входного сигнала, выход - к управляющему входу первого сдвигового регистра, а второй вход- к первому выводу суммирующего резистора и вторым выводам весовых резисторов, первые выводы которых связаны с разрядными выходами второго сдвигового регистра, тактирующим входом соединенного с тaктиps oщим входом первого сдвигового регистра и шиной тактового сигнала, причем второй вывод суммирующего резистора подключен к о(ей шине, отличающийся тем, что, с целью повьваения разрешающей способности, он снабжен аналоговым вычитающим блоком, вторым компаратором, вгорым дешифратором, третьим сдвиговым регистром и коммутатором, первый и второй сигнальные входы которого связаны с входс1ми первого к таратог ра, управляющий вход - с выходом первого кокларатор, а первый и бторой выходы - с первым и вторым входами аналогового вычитающего блрка, аыходом- соединенного с первым входом второго кбмпаратора, второй вход которого подключен к шине постоянного напряжения, а выход - к управляющему входу третьего сдвигового регистра и второму входу второго дешифратора, первый вход которого связан с выходе первого компаратора, а выходы - с управляющими входа ми второго сдвигового регистра, причем тактирующий вход третьего сдвигового регистра соединен с шиной тактового сигнала, а разрядные выходы - с.входами первого дешифратора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для анализа формы электрического сигнала | 1979 |

|

SU792174A1 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Анализатор формы сигнала | 1978 |

|

SU741197A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-06-30—Публикация

1982-03-31—Подача