Изобретение относится к евтоматике и вычисшггепьной технике и может быть использовано при построении устройств преобразования информещии.

Иавеоген преобразовапгепь двоичного коца в овоично-десятичный код, соаержадий регистр, разделенный на тетрады, четырехразрядньй счетчик, накопительный сумматор, блок управления вычитанием, блок анализа знака числа, блок формировании управляющих сигналов l .

Недостаток известного преобразовеггеля состоит в большом объеме аппаратуры, что связано с наличием накопительнотх) сумматора

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является преобразователь двоичного кода в авоично-десятичный код, соаержаций сдвиговый регистр, вычитатепь и блок управления, выход которого соединен с управляющими входами регистра сдвига и вычитателя, первый вход вычитателя соединен с выходом сдвигового р&гнстра. Кроме того, это устройство содержит 4ор ирОватель двоичных эквивалентов и переключатель двоичных эквивалентов 2 .

Недостатком этого преобразователя является относительно большой объем аппаратуры.

Цель изобретения - упрощение преобразователя за счет новой реализации бло ка делэния на десять.

10

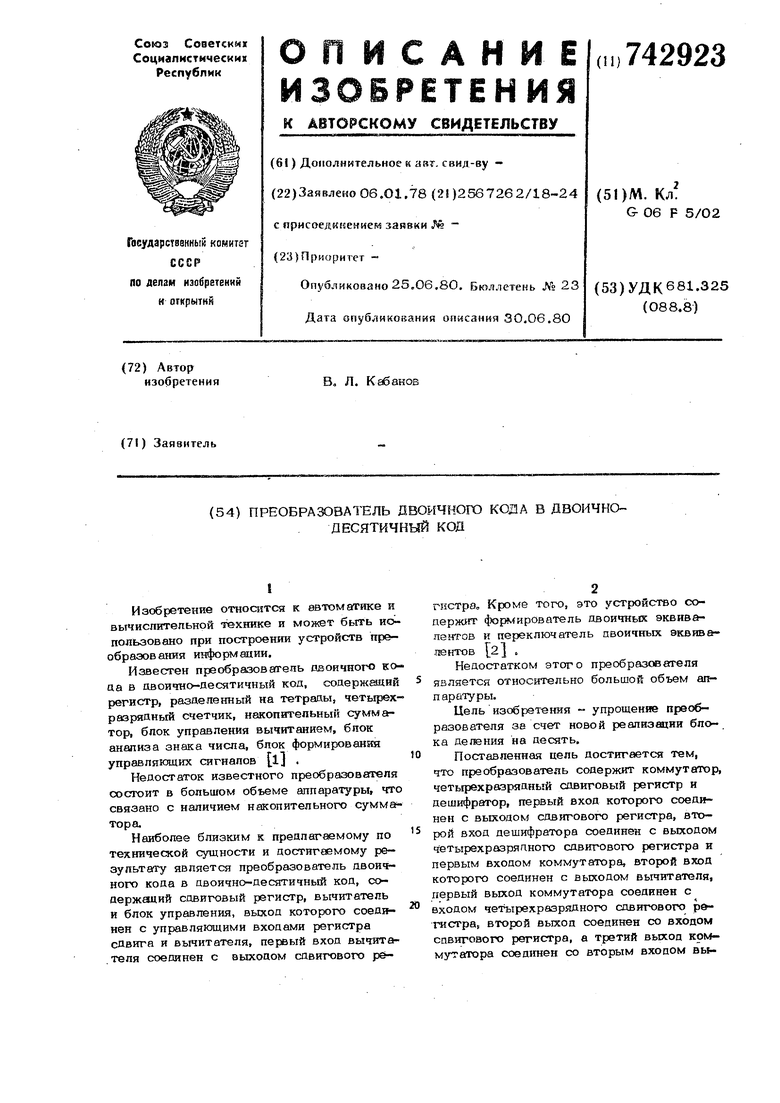

Поставленная цель достигается тем, что преобразователь содержит коммутатор, четьфехразрядный сдвиговый регистр н дешифратор, первый вход которого соединен с выходом сдвигового регистра, вто15рой вход дешифратора соединен с выходом четырехразрядного сдвигового регистра и первым входом коммутатора, второй вход которого соединен с выходом вычитателя, первый выход коммутатора соединен с

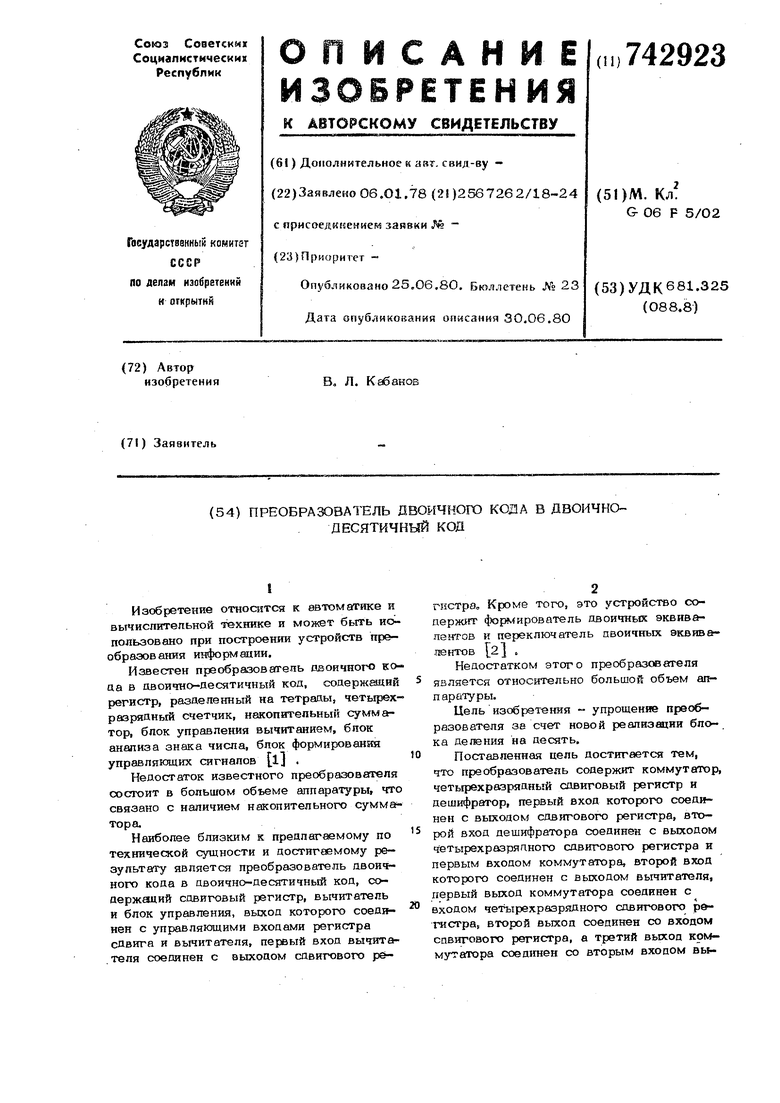

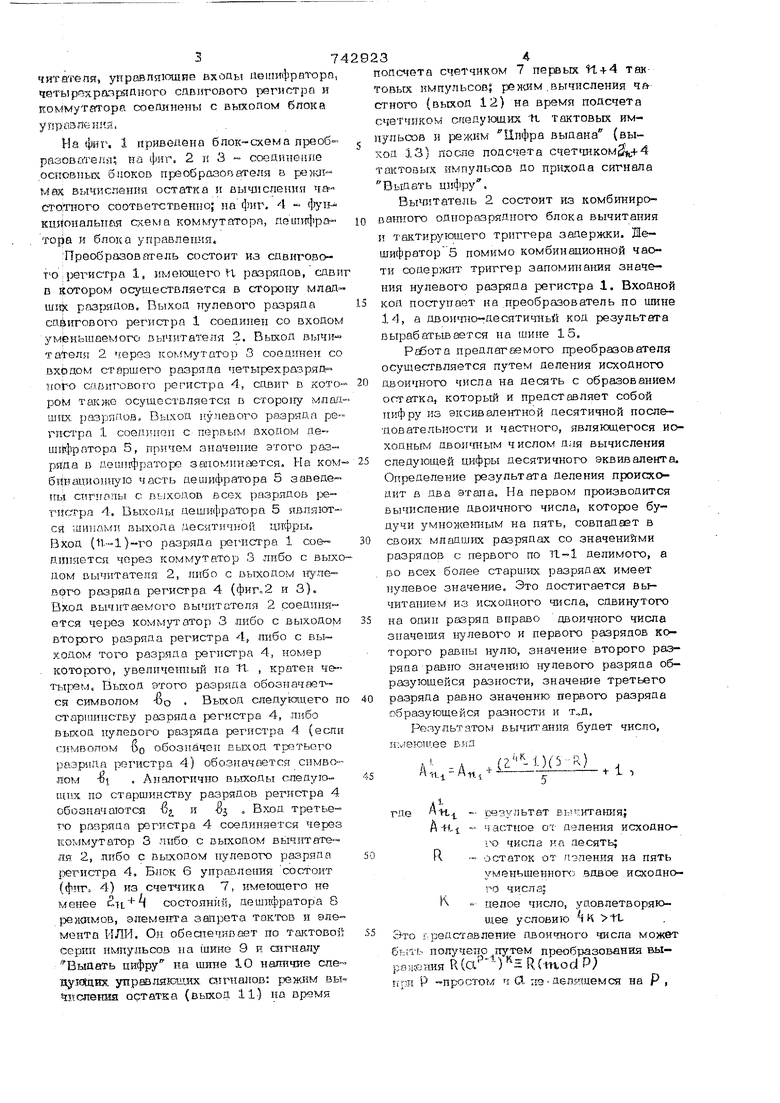

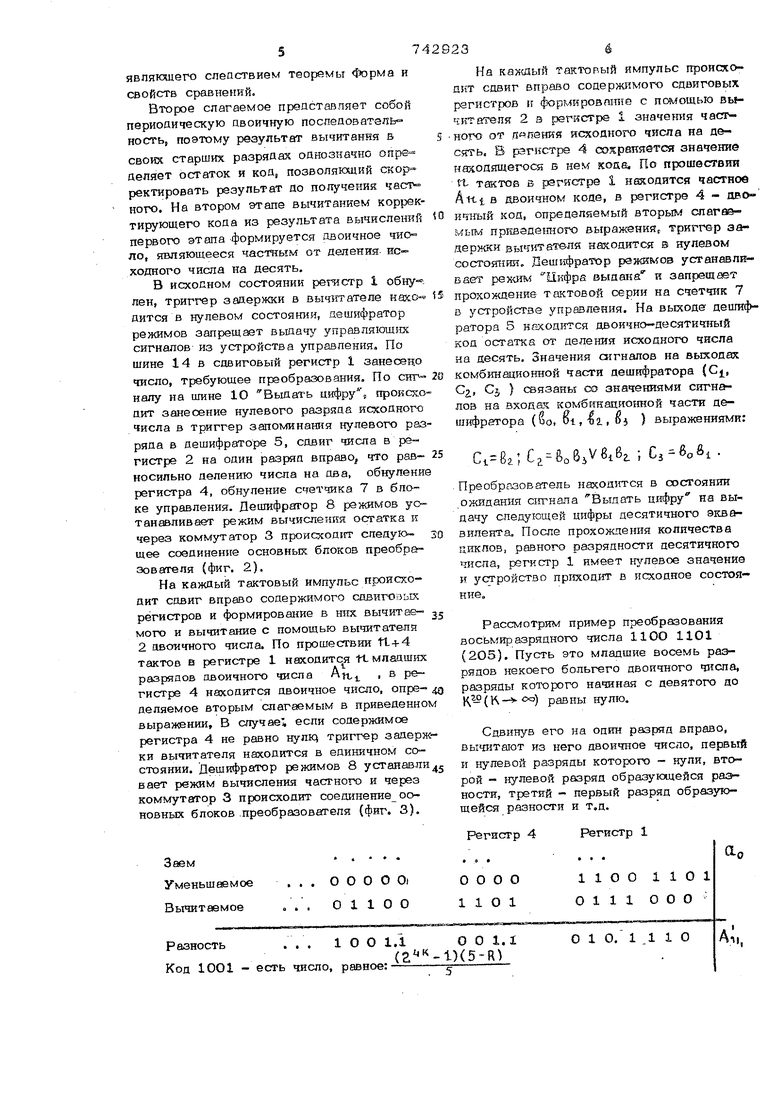

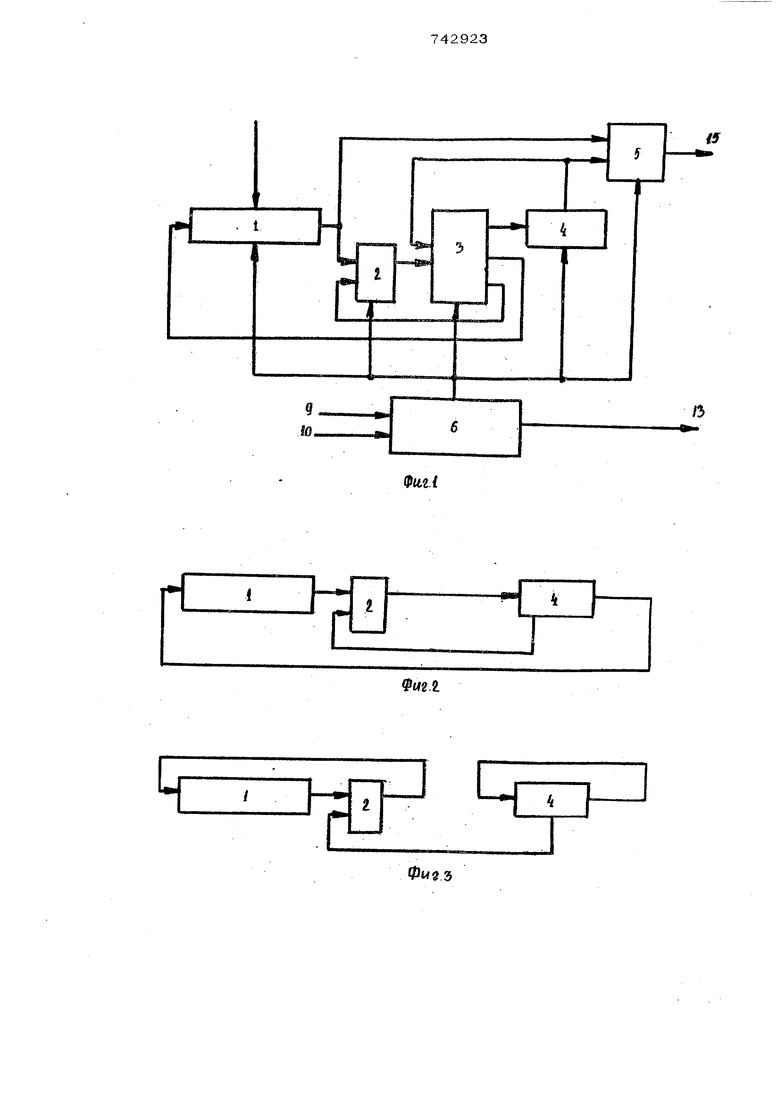

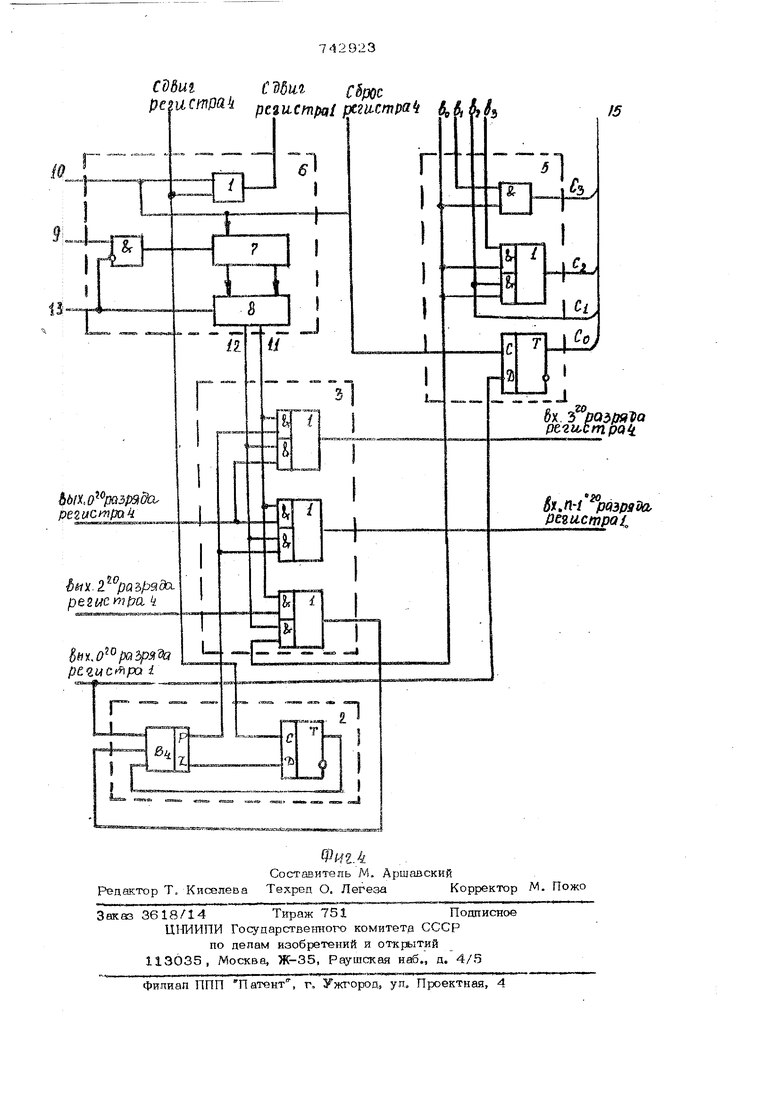

М входом четырехразрядного сдвигового р& гистра, второй выход соединен со входом спвигового регистра, а третий выход коммутатора соед1шен со вторым входом въьчитателя, угфавпяющие вхоаы авшнфратора, четырехразрядного сдвнговото регистра к коммутатора соеЩ1нвны с выхопом бпока упдйзггекия, На фиг. 1 привепена блок-схема преоб- разовctrersii на фиг. 2 п 3 - соедипеипе рсиов 1ых блоков преобразователя в ремг ы&п ВЫЧЙСП9НПЯ остатка я выщзсления часто:тного соответ-ственно; иа фнт 4 « (lyi кционапьпад схема коммутатора, acjuiwjipaтора и бпока управпепия. ;Пр9образователь состоит из сдвигового, регистр а 1, имеющего Н разрядов, сдви в котором осущес твпяется в ci opoiiy млад шщ разрядов. Выход 7тулево1-ю разряда сд$игово1Х5 регистра 1 соединен со входом уменьшаемого вычитатепя 2. Выход вычн- тагеля 2 герез кок мутатор 3 соединен со входом старшего разряда четырехразряП:него савнгового регистра 4, сдвиг в кото ром такжо осуществляетсл в сторону млаа ргазрядов. Выход нулевого разряда регистра 1 соедшген с первым входом деШ1р:1гратора 5, причем значение этого раз- ряда в Дешифраторе запоминается. На ком бнвациониую часть деи ифра1Т ра 5 заведены снг гольт с BbixojioB всех разрядов гпсгра 4. Выходы дешифратора 5 явл;т1отей шипами выхода десятичной цифры. Вход (tl-l)-ro разряда регистра 1 соедипяется через коммутатор 3 либо с выхо дом вычитатепя 2, либо с выходом нуле- всрго разряда регистра 4 (фиго2 и 3). вычитаемого вычитателя 2 соединяется че{зез коммутатор 3 либо с выходом второго разряда регистра 4, либо с выходом тог-о разряда регистра 4, номер - которого, увеличенный на П- , кратен че-TbtpSM. Выход этого разряда обозначает си символом -OQ . Выход следующего и старшинству разряда регистра 4, либо вькод нулевого разряда регистра 4 (еспи симвО(Лом УО обоз1шчеп вькод третьего разряда регистра 4) обозначается снмво-jioM -ot , Аналогично выходы следугоUU X по старшинству разрядов регистра 4 обозначаются и -oj о Вход третьего разряда регистра 4 соединяется через коммутатор 3 либо с выходом вычитате- ля 2, либо с выходом нулевого разряда jjerncTpa 4, Блок 6 управления состоит (фиг. 4) из 7, имеющего не менее йцп состояний, дешифратора 8 1эеидамов, элемента запрета тактов н элемента ИЛИ. Он обеалепивает по тактово Серии импульсов на шине 9 и сигналу Выдать цифру на шине 10 наличие nyiotaHx управляющих тгнаагав: режим вы«итспеиия остатка (выход 11-) на время одсчета счетчиком 7 первых 11 + 4 таковых импульсов рбмдам .вычисления ч& тиого (выход 12) на время подсчета четчиком спедутацих ti тактовых имупьсов н режим- Цифра выдана (выод 13) после подсче-та стет шком0(,ч-4 актовых импупьсов до прихода сигнала Выдать цифру. Вып татель 2 состоит из комб1широатюго одноразрядного блока вычитания тактирующего триггера задержки. Не- шифратор 5 помимо комбинационной части содержит триггер запомрша1дая значения нулевого разряда регистра 1. Входной код поступает на .преобразователь по ишне 14, а двоишо-десяти шьй код результата вырабатывается на шине 15. предлагйэмого преобразователя осуществляется путем деления исходного двоичного числа на десять с образованием остатка, который и представляет собой цифру из экс1шалентной десятичной посла-довательности и частного, являющегося иоходным двоишым ч ислом для вычисления следующей цифры десятичного эквивалента. Определение результата деления происходит в два этана. На нервом производится вычисление двоичного числа, которое будучи умноженным на пять, совпадает в своих младших разрядах со значенийми разрядов с первого по ) делимого, а во всех более старш -1х разрядах имеет нулевое значение. Это достигается вычитанием из исходного числа, сдвинутого на один разряд вправо двоичного числа значегшя нулевого и первого разрядов которого равны нулю, значение второго разряда равно зиачеш Ю нулевого разряда образующейся разности, значение третьего разряда равно значению первого разряда образующейся разности и т„д, Результатогу вычитания будет число, имегоитее вид )(5 -R) 4/ f & Лпи. - Анч Itl.) - результат вы .итагаш; ьастное oi деления исходного числа на десять; остаток от пэпения на пять уменьшеннопл .вдвое исходного числа; | целое число, удовлетворяющее условию i К -П. представление двоичного числа может быть получено путем преобразования выро дашм R(a )н RCmod Р; при Р -проопэм 5 (Д. 119 делетцемся на Р , являющего слеаствием теоремы Форма и свойств сравнений. Второе слагаемое представляет собой периодическую двоичную последовательность, поэтому результат вычитания в своих старших разрядах однозначно опре деляет остаток и код, позволяющий скор ректнровать результат до получения «гаст ного. На втором этапе вычитанием коррек тирующего кода из результата вычислешей первого этапа -формируется овоичное чио™ ло, являющееся частным от деления исходного числа на десять. В исходном состоянии peniCTp 1 обнулен, триггер задержки в вычитателе нахо дится в нулевом состоянии, дешифратор режимов запрещает вьшачу управляющих сигналов из устройства управления. По шине 14 в сдвиговый регистр 1 занесено число, требующее преобразования. По сяг налу на щине 1О Выдать цифру происхо дит занесение нулевого разряда исходного числа в триггер запоминания нулевого раз ряда в дешифраторе 5, сдвиг числа в регистре 2 на один разряд вправо, что равносильно делению числа на два, обнулени регистра 4, обнуление счетчика 7 в блоке управления. Дешифрэтор 8 режимов ус танавливает режим вычисления остатка к через коммутатор 3 происходит следую, щее соединение основных блоков преобразоваггеля (фиг. 2). На каждый тактовый импульс происходит сдвиг вправо содержимого сдвиговых регистров и формирование в них вычитае- МО го и вычитание с помощью вычитателя 2 двоичного числа. По прошествии tl-f 4 тактов в регистре 1 находится tt младших разрядов двоичного числа Att в ре гистре 4 находится двоичное число, опре- деляемое вторым слагаемым в приведенном выражении, В случае если содержимое регистра 4 не равно нул1а триггер задерж ки вычитателя находится в единичном состоянии. Дешифратор режимов 8 устанавли вает режим вычисления частного и через коммутатор 3 происходит соединенне ооновных блоков .преобразователя (фиг. 3).

Регистр 1

Регистр 4 На кахшый тактовый импульс происхоП51Т сгшиг вправо содержимого сдвиговых рагистров и формкровгаше с помощью выЧ1гтатепя 2 s регр5стре 1 значения частного от допения исходного числа на десять. В рэгкстрж 4 сохраняется значение Hasoajnuerocs в нем кода. По прошествии tt тактов Б рэгислре 1 находится частное Aitt в двоичном коде, в регистре 4 - ивоH ifb код, опредалйемый вторым слагае /ы привадегаюго выражения триггер задержки вычитателя находится в нулевом состоянии. Дешифратор режимов устанавли- Бает рехдам Цифра выдана н запрещает прохождение тактовой серии на счетчик 7 в устройстве управления. На выходе деигифратора 5 наход1ггся двоично-десятичный код остатка от деления исходного числа на десять. Значения сигналов на выходах комбинационной части дешифратора (С, С2,, Cj ) связаны со значениями сигналов на входах комбинационной части дешифратора (Ьо, Di.ta.,} ) выражениями: C,,-6o6iV8i6 ; Сз-бой. Преобразователь находится в состоянии ожидания сигнала Выдать цифру на выдачу следующей цифры десятичного эква вилента, После прохождения количества циклов, равного разрядности десятичного числа, регистр 1 имеет нулевое значение и устройство приходит в исходное состояние. Рассмотрим пример преобразования восьмиразрядного числа 110О 1101 (205). Пусть это младшие восемь разрядов некоего больгего двоичного числа, разряды которого начиная с девятого до К() равны нулю. Сдвинув его на оцин разряд вправо, вычитают из него двоичное число, первый и нулевой разряды которого - нули, второй - нулевой разряд образующейся раэности, третий - первый разряд образуюейся разности и т.д.

7429238

Отсюпа , а остаток от пвпения наченпую периощгческую последователь-десять есть: 2R4- (выпелпетси до- ность, иаходпшуюся в .регистре 1. .шифратором).(В дапвом примере вычитатель сохраняНаходнм частное, испачьзуя гюлту,.,ет заегл). FMeiibujaeMoe, .1 О I О i 1 Вычитаемое 1 О О ,1 1 О РазностьО О О 1 О 1 1 Результатом является код 000 :В данном преобразоватепе увеличение разрядности исходньс. двоичных чисел, Требующих преобразования, отражается пп1нь на увеличении количесггва погическлх эпёментов в сдвиговом регистре числа, При использовании известнызс з/стройств увеличение разрядности исходных двоичных чисел отражается в основном на количестве логических элементов в накапливающсгм сумматоре. Количество элементов в осталь iiofi части как в известном, так и в лагсемом преобразователе равноненно и соответствует реализации .десяти разрядов сдвигового 1зегистра. Па анлива1ощнй сум-матор вдвое большего коли.чества логических элемешов, чем сдвиговый регистр той же разрядности. Так как в устройствах автоматики ширткое распростра не гие получает десятичная нндикадия ifa электронно-лучевых трубках, требующаяпоследователыюго вывода десятичных цифр нредлагаемьп-j преобразователь удовлет 5О ряет требованиям по быстродействию. Положительный э(|к}1ект загслючае-тся в уменьшен ИИ количества лог илеских эле менто Экономия кол.ичества логических элеменТОВ составляет 30% для десятиразрядного преобразователя и более для нреобрачоватепей большей разрядности. Формула изобретен и я Преобразователь двоичного кеда в ично-десятичный код, содержащий савиго() (5-) ..-.4--T-,.vii,-:-.-,;:I- - -4i«; 4i « НО (20) вый рег.истр, вычитатепь и блок управле- ння, ВЫ.ХОД icoToporo соединен с управляющими входами регистра сдвига и вычитателя, первый вход вычитателя соединен с выходом сдвигового регистра, о т л и ч аю щ и и с я тем, .что, с целью упрощения преобразователя, он содержит коммутатор, ч:етырехразря.дный сдвиговый регистр и дешифратор, первый вход которого соединен с выходом сдвигового регистра, второй вход дешифратора соединен с выхо- . дом че1 ырехразрядного сдвигового регист ра и первым входом коммутатора, второй вход которого соединен с выходом вычитател.я, первый выход коммутатора соединен с входом четырехразрядного сдвигового регистра, зторЪй выход соединен со входом Сдвигового регистра, а третий выход коммутатора соединен со вторым входом вычитателя, управляющие входы дешифратора четырехразрядного сдвигового рег истра и ксгммутатора соединены с выходом бьЧока управления И СТ1Э чн1жи информ аци, принятые во внимание при экспертизе -1. ABTODC.KC-:-; свидетельство СССР № 437069, к:п, Gr 06 F 5/02, 1972. 2, Авторское свШ.ете;.ъство СССР N 486314, .UU G 06 F 5/02, 1973 (г(р : тотнп)«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования двоичного кода в десятичный | 1976 |

|

SU633013A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU922723A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

д

lo

5

Фмзэ

Авторы

Даты

1980-06-25—Публикация

1978-01-06—Подача