10

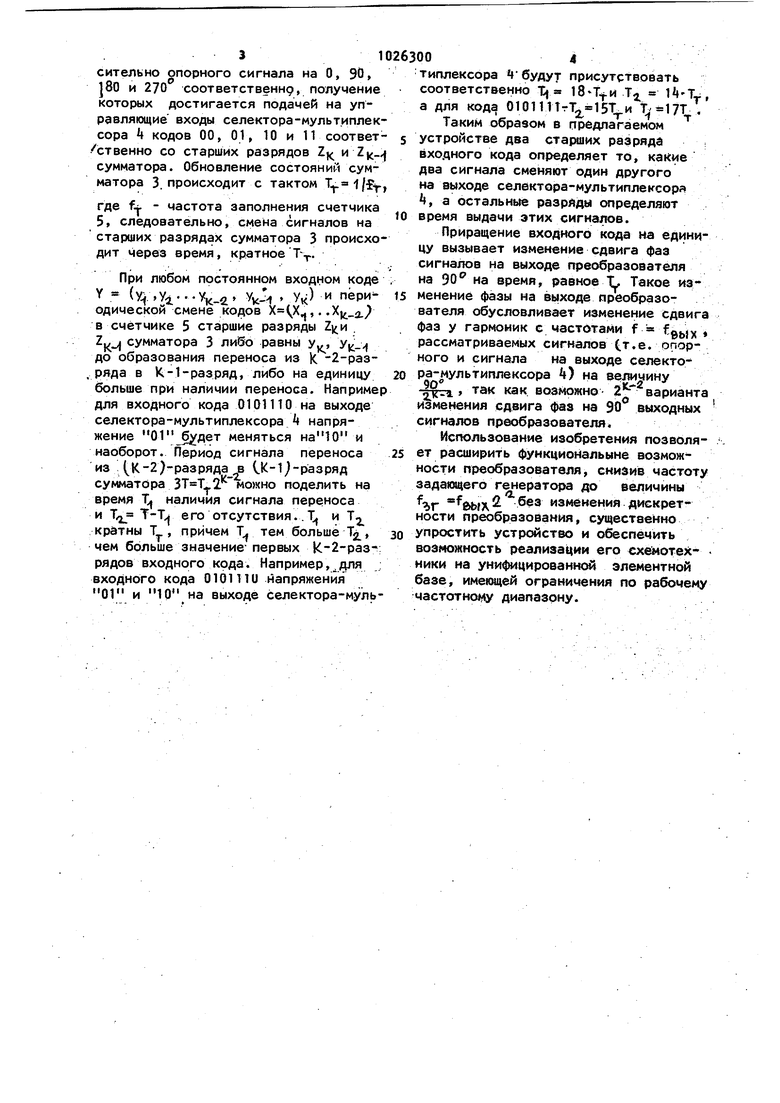

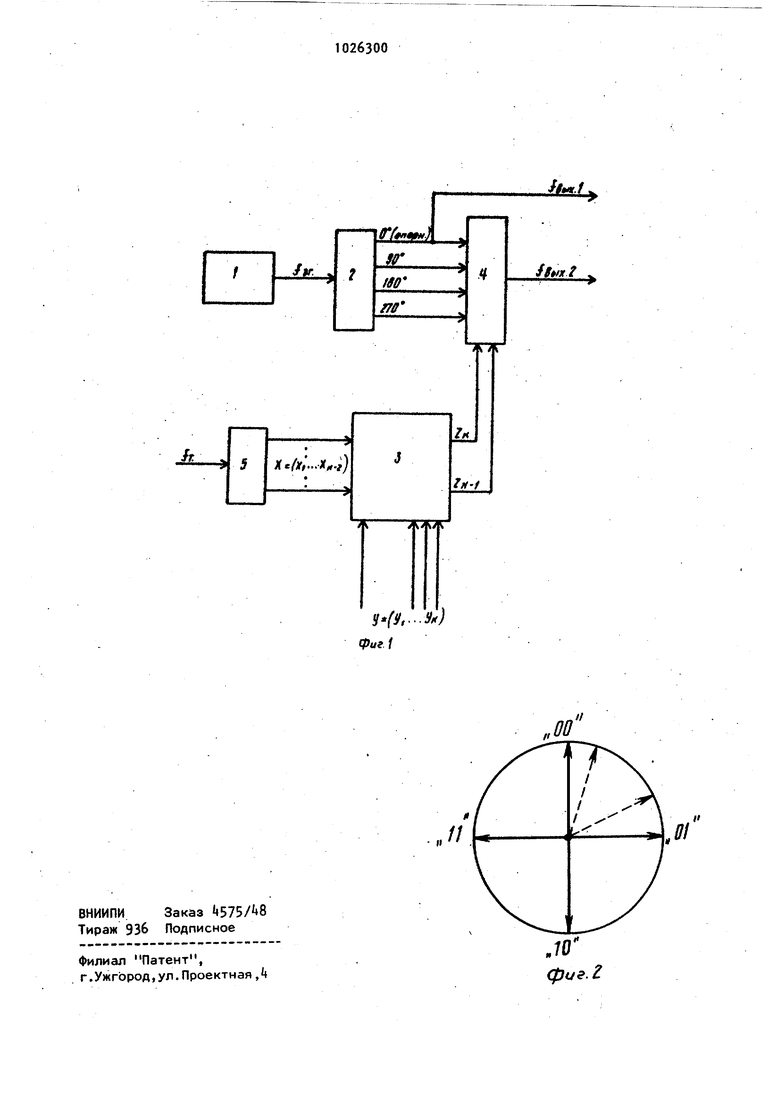

05 ОО 11 Изобретение относится к импульсной технике и может быть использовано в автоматике, измерительных и вычислительных системах. Известно устройство формирования сигнала с дискретно изменяемой фазой содержащее генератор К-разрядный общий делитель, дешифраторы с подключенным к ним блоком управления, узлы уточнения, формирователи и преобразователи сигнала и Уй-ячеек, .каждая из которых содержит последорательно включенные узлм уточнения, формирователь и преобразователь формируемого сигнала, причем между входом узла уточнения каждой из ячеек и об щим делителем включен сбой отдельный дешифратор. Ко всем преобразователям ячеек подключен выход формиоователя гетеродинного напряжения, входы кото рого подключены к задающему генератору и выходу общего делителя fll. Недостатками данного устройства являются сложная настройка и низкая надежность. близким к предлагаемому является цифровое устройство для воспроизведения фазовых сдвигов, содержащее Задающий генератор, связанный с делителем частоты, элемент И, выход Которого соединен с одним тактируемого триг гера, К -разрядный и К-1 разрядный сумматоры, при этом делитель час тоты выИолнен К-1-разрядным, а его выходы соединены с первой группой входов старших (эаарядов К-разрядного сумматора, вторая группа входов которого и младший разряд первой труп пы подключены к К -разрядному входному коду и к первой группе входов )-разрядного сумматора, вторая группа входов которого соединена со старшими разрядами К-разрядного входного кода, а выхода старших разрядов сумматоров подключены к входам элемента И, выход которого соединен с управляющем входом тактируемого триггера . Недостатками устройства являются использование заедающего генератора, обладающего высокой частотой, а также сложность технического решения. Цель изобретения - упрощение устройства и расширение функциональных возможностей путем уменьшения частоты задающего генератора. Поставленнай цель достигается тем что в преобразователь код-Фаза, со0держащий задающий генератор, соединенный с делителем частоты, и К-разрядный сумматор, введены селектормультиплексор и К-2-разрядный двоичный счетчик, при этом делитель частоты соединен с информационными дами селектора-мультиплексора, двумя управляющими входами подключенного к выходам двух старших разрядов -разрядного сумматора, первая группа входов которого подключена к клемме К-разрядного входного кода, а вторая соединена с выходами К-2-разрядного двоичного счетчика. Нафиг. представлена блок-схема устройства; на фиг.2 - векторная диаграмма его работы. Преобразователь содержит задающий генератор 1, связанный с триггерным делителем 2 частоты, К-разрядный сумматор 3,селектор-мультиплексор Ц и К-2-разрядный двоичный счетчик 5Делитель 2 частоты соединен с информационными входами селекторамультиплексора k и двумя управляющими входами подключенного к выходам двух старших разрядов К-разрядного сумматора 3. На первую группу входов К-разрядного сумматора подан К разрядный код, а вторая подключена к выходам К-2-разрядного счетчика 5. Устройство работает следующим образом. Сигнал с задающего генератора 1 поступает на тактовый вход тоиг- . :герного делителя 2 частоты, четыре :выхода (юторого с сигналами частотой сдвинутыми относительно одного из них (принятого за опорный на of 90, 180 и 270( фиг.2, соединены с четырьмя информационными входами селектора-мультиплексора , два управляющих входа которого соединены с выходами двух старших разрядов i и ) К-разрядного сумматора 3. На первую группу входов сумматора 3 подан К -разрядный входной код У Уа---УкЬ iна вторую группу входов поступаетХ-2-(разрядный код X Х , Xj.. .. ) выходов k -2-разрядного двоичного счетчика 5Сигналы с выхода делителя 2 частоты (опорный выход) fgjjjy 1 и селектора-мультиплексора -,х2 являются выходными сигналами преобразователя. На фиг.2 векторами 00, 01, 10 и 11 изображены возможные напряжения на выходе селектора-мультиплексора /т.е. напряжения, сдвинутые отно31сительно опорного сигнала на О, 90, 80 и 270 соответственнр, получение -которых достигается подачей на управляющие входы селектора-мультиплек сора k кодов 00, 01, 10 и 11 соответ ственно со старших разрядов Zj и ZK сумматора. Обновление состояний сумматора 3. происходит с тактом fi. - частота заполнения счетчика где . 5, следовательно, смеНа сигналов на старших разрядах сумматора 3 происхо дит через время, кратноеТ. При любом постоянном входном коде Y (У У4.--YK. УК и периодической смене кодов ,. ../ в счётчике 5 старшие разряды . 2,. сумматора 3 либо равны у., до образования переноса из R -2-раз. ряда в К-1-разряд, либо на единицу больше при наличии переноса. Наприме для входного кода 0101110 на выходе селектора-мультиплексора А напряжение 01 меняться и наоборот. Период сигнала переноса из ДК-2)-разряда,в СК-1 -разряд сумматора .,2 можно поделить на время Т| наличия сигнала переноса и Т -i его отсутствия. L и Т. кратны Т , причем Т тем больше Т2, чем больше значение первых К.-2-разрядов входного кода. Например,для входного кода 010111U напряжения 01 и Ю на выходе селектора-муль 004 типлексора будут присутствовать соответственно Ца (.и Т Tyi а для кода 010111ТгТ 15Т и t, , Таким образом в предлагаемом устройстве два стариих разряда , входного кода определяет то, какие два сигнала сменяют один другого на выходе селектора-мультиплексора , а остальные разряды сэтределяют время выдачи этих сигналов. Приращение входного кода на единицу вызывает изменение сдвига фаз сигналов на выходе преобразователя на 90 на время, равное Ъ Такое изменение фазы на выходе преобразователя обусловливает изменение сдвига фаз у гармоник с частотами f еых рассматриваемых сигналов (.т.е. опорного и сигнала на выходе селектора-мультиплексора ) на величину |.а, так как возможно варианта изменения сдвига фаз на 90 выходных сигналов преобразователя Использование изобретения позволяет расширить функциональыне возможности преобразователя, снизив частоту задающего генератора до величины ЪГ W)fA ® изменения дискретности преобразования, существенно упрсх:тить устройство и обеспечить возможность реализации его схемотех- . НИКИ на унифицированной элементной базе, имеющей ограничения по рабочему частотному диапазону.

//w/

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-фаза | 1978 |

|

SU744973A1 |

| Преобразователь код-частота | 1981 |

|

SU966890A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ | 2000 |

|

RU2173933C1 |

| СПОСОБ ПЕРЕДАЧИ МНОГОМЕРНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ, СПОСОБ СЛОВНОЙ СИНХРОНИЗАЦИИ МАЖОРИТАРНО УПЛОТНЕННЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2004 |

|

RU2262206C1 |

| Устройство для контроля метрологических характеристик средств измерений | 1982 |

|

SU1117592A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Устройство для автоподстройки фазы тактовых импульсов | 1990 |

|

SU1811017A1 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

ПРЕОБРАЗОВАТЕЛЬ.КОД-ФАЗА, содержащий генератор, соединенный . с делителем частоты, и-К-разрядный сумматор, отличающий,ся тем, что, с целью.упрощения устройства и расширения функциональных возможностей путем уменьшения частоты задающего генератора, в него введены селектор-мультиплексор и К-2-разрядный двоичный счетчик, при этом делитель частоты соединен с информационными входами селектора-мультиплексора, двумя управляющими входами соединенного с выходами двух старших разрядов К -разрядного сумматора , первая группа входов которого подключена к клемме К -разрядного входного кода, а вторая соединена с выходами К-2-разрядного счетчика.

h

X.... x.;}

ISL

гч-f

Авторы

Даты

1983-06-30—Публикация

1982-01-04—Подача