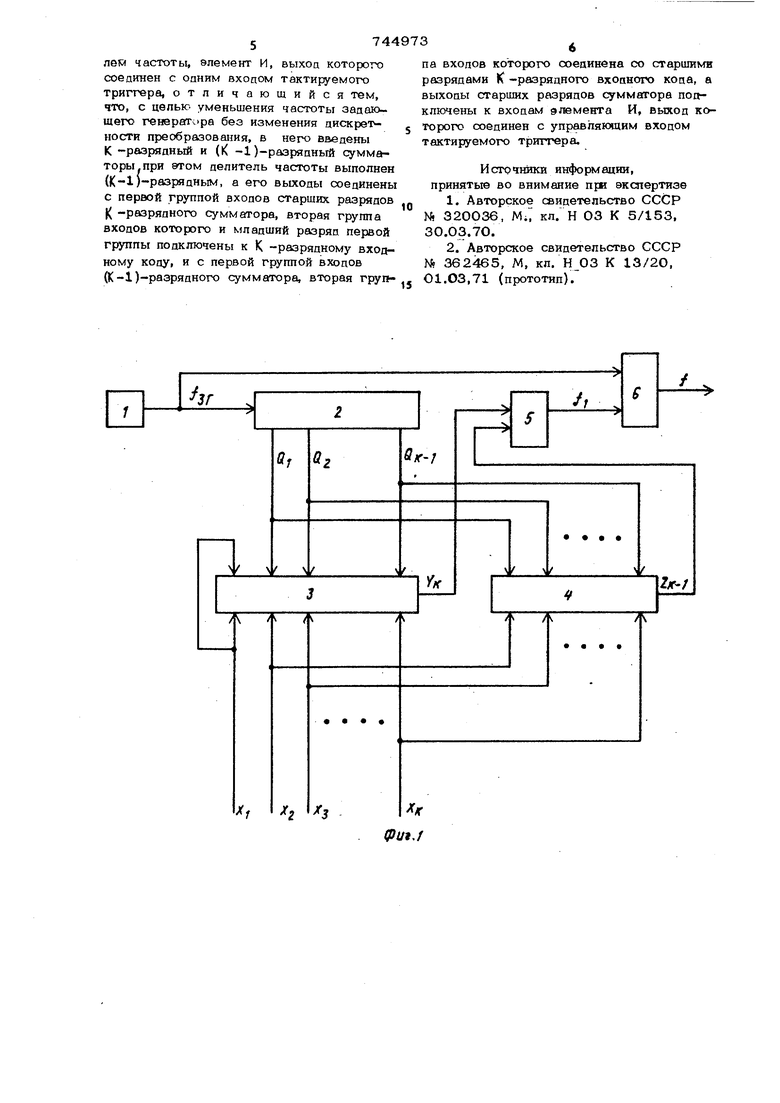

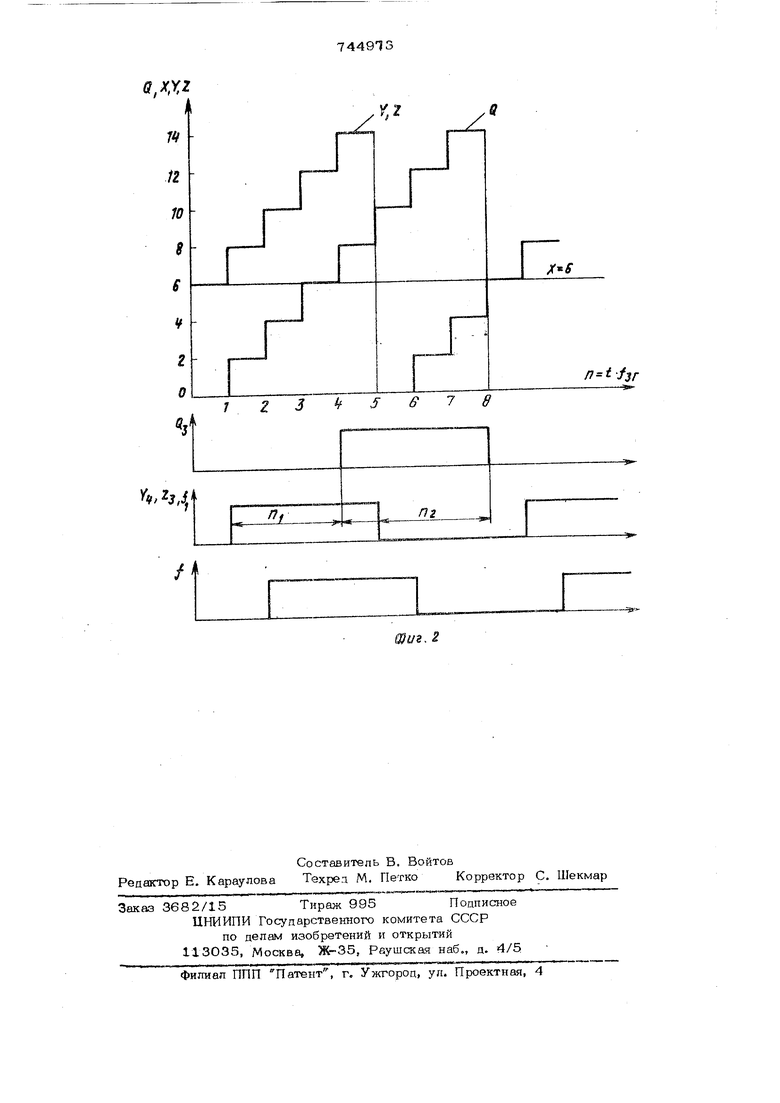

Предлагаемое изобретение относится к .области импульсной техники и может быть использовано в автоматике, измерительных и вычиспительных системах. Известно устройство формирования сиг Н1ала с цискретно измеряемой фазой, содер жащее генератор, К -разрядный, общий делитель, пешифраторы с подключенным к ним блоком управления, узлы уточнения, формирователи и преобразователи сигнала, и mячеек, каждая из которых содержит последовательно включенные узлы уточнения, формирователь и преобразователь фор мируемого сигнала, причем между входом узла уточнения каждой из ячеек и общим делителем включен свой отдельный дешифратор, ко всем преобразователям ячеек пoдkлючeн выход формирователя- гетеродинного напряжения, входы которого подключены к задающему генератору и выходу общего делителя 1 , Схема данного устройства реализуется с использованием большого количества цифровых комбинационных, и аналотх)вых: блоков, требует высокой частоты генератора и имеет сложную настройку, что приводит кувеличению габаритов и снижению надеж|ности выполняемых на ее основе приборов. Известно также цифровое устройство для воспроизведения фазовых сдвигов, содержащее задающий генератор, связанный с делителем частоты, выходы которого соединены с одними входами блока сравнения, другие входы которого подключены к выходам блока установки кода фазовотх) сдвига, счетный триггер, фильтры, схемы совпадиния, схемы однозначности и неоднозначгнооти и триггер с раздельным управлением, причем выход счетного триггера соединен с первыми входак схем однозначности и неоднозначности, вторые входы которых подключены к выходу старшего разряда блока установки кода фазового ;сдвига, а выходы схем однозначности и неоднозначности соединены с Одними входами схем совпадений, другие входы которых подключены к выходу блока сравнения, а выходы схем совпааения соединены с соответствующими входами триггера с раздельным управлением { К недостаткам такотх) преобразов(атепя косгфаза следует отнести высокую тактовую частоту задакяцего генератора, определяемую соотношением -Pjr - -РЬЫХ где Toytf частота выходных сигналов устройства. Требование высокой тактовой часгготы заставляет применять умножение npoi ограничении, сетки тактовых частот, затрудняетпрш ене1дае доступной элементной базы, усложняет устройство. Целью предлагаемого изобретения явля- ется уменьшение частоты задающего генервтора без изменения дискретности преобразования. Поставленная цбль достигается за счет того, что в преобразователь , со держащий задающий генератор, связанный с делителем частоты, эдемент И, выход которого соединен с одним входом такТируемого триггера в ведены К -разрядный и (К-1)-разрядный сумматоры, при этом делитель частоты выполнен (К-1)-разря ным, а его выходы соединены с первой группой входов старших разрядов К-разряд ного сумматора, вторая группа входов которого и младший разряд первой группы подключены к К-разрядному входному коду и с первой группой входов (К 1)разряд ного сумматора, вторая группа входов которого соединена со старшими разрядами К -разрядного входного кода, а выкоды старших разрядов сумматоров подключены к входам элемента И, выход со; единен с управляющим входом тактируемого триггера. На фиг. 1 дана; структурная электриче ская схема устройства; на фиг 2 приведены временные диаграммы, поясняющие работу устройства для случая разрядности К-4 и входного кода Х-6. Преобразователь содермгт задающий генератор I, (К -1)-разряпный делитель частоты 2,К-разрядный суммагтор 3, (К-1)-разряйный сумматор 4, элемент И 5 и. тактируемый триггер 6, Сигнал f,n с запакяцего renepairopa по ступает на тактовый вход триггера 6 и на (К -1)-разрядный делитель часгготы 2, все выходы Q, Qji,... Gy- . которого соединены с первой группой входов старьших разрядов Ki -разрядного сумм.9Тора 3. Вторая группа входов сумматора 3 и младший разряд первой группы со адинены с К -разрядным двоичным входным кодом X ( ...Х((). Кроме того, выходы делителя частоты соединены с первой группой входов (К -1)-разрядного сумivsaTopa 4, вторая группа входов которого соединена со старшими разрядак и К-разрядного входного кода X . Сигналы Y с выхода стекшего разряда сумматора 3 и 2((- с выхода старшего разряда сумматора 4 ПОД61НЫ на входы элемента И 5, выход которого -Р соединен с управляющим входом тактируемого триггера. Выходные сигналы Y, сумматоров Зн4 и сигнал f , с выхода схемы И 5 появляются с некоторыкт присущим цифровым блоком нестабильным запаздьюанием по отношению к тактам п задающего генератора, что могло бы внести фазовую ошибку в преобразование код-фаза при иопользовании сигнала -Р, з качестве выхопного. Привязка сигнала -Р к тактам осуществляется на выходе тактируемого триггера 6. Именно сигнап Р ( -P без учета нестабильности) и сигнап Q на выходе-ст шего (K-l)-ro разряда делителя частоты и являются выходными сигналами преобразователя частотой . видно Р.ы -2 Из фиг. 2 видно, как образуются сдви переднего П и заднего п фронтов f ifj при К, 4 и ( 6. Здесь относительно Q, величины G( 2-I Q-2 У 1 Y 2. Z 2;IZi2 (,К-1л.-2- - raeO-,Yi,Z|X; lo,i}, являются десятичным эквивалентным представлением двоичных кодов соответственно на одном из входов четырехразрядного сзмматора, на выходе 4-разряднотх1 сумматора, на выходе трехразрядного суммшора к иа входе преобразователя. Приргацение входного копа X на единицу вызывает изменение лишь одного из, фронтов сигнала f или fi на величину для К 4 или общем случае. Поскольку сдвиг по фазе между первыми гармониками меандра У(., и сигнала -р или -р определится полусуммой сдвигов переднего и зацнего фронтов, цена младшего разряда составит 360°/2 , что позволяет при достижении прежней дены младшего разряда 36О/2 вдвое снизить тактовую частоту задающего генератора без изменения дискретности преобразования. Формулаизобретения Преобразователь код-фаза, содержащий задающий генерегтор, (жязанный с целитеnew частоты, элемент И, выхоц которотх соединен с опним вхоцом тактируемотх) триггера, отличающийся тем, что, с цепью уменьшения частоты задающего генератора без изменения дискретности преобразования, в него введены К -разрядный и (К -1 )-разряцньгй сумматоры при этом делитель частоты выполнен (К-1)разрядным, а его выходы соединены с первой группой входов старших разрядов К -разрядного сумматора, вторая группа входов которого и младший разряд первой группы подключены к К -разрядному входному коду, и с первой группой входов (К-1)-разрядного сумматора, вторая группа входов которого соединена со старшими разрядами К -разрядного входного кода, а выходы старших разрядов сумматора попкпючены к входам элемента И, выход которого соединен с управляющим входом тактируемого триггера. Исгочн1жи информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 320036, Мл кл. Н 03 К 5/153, 30.03.7О. 2.Авторское свидетельство СССР № 362465, М, кп. Н 03 К 13/2О, О1.ОЗ,71 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-фаза | 1982 |

|

SU1026300A1 |

| Преобразователь код-частота | 1981 |

|

SU966890A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Стохастический преобразователь | 1977 |

|

SU732946A1 |

| Цифровой фазовращатель | 2024 |

|

RU2823429C1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1132289A1 |

| Преобразователь код-частота | 1982 |

|

SU1048572A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Генератор псевдослучайных узкополосныхСигНАлОВ | 1979 |

|

SU840897A1 |

ЗГ

N

f

/ /

h 3

W

lK-1

i 1

l

XK фиг,}

Фи.г

Авторы

Даты

1980-06-30—Публикация

1978-03-20—Подача