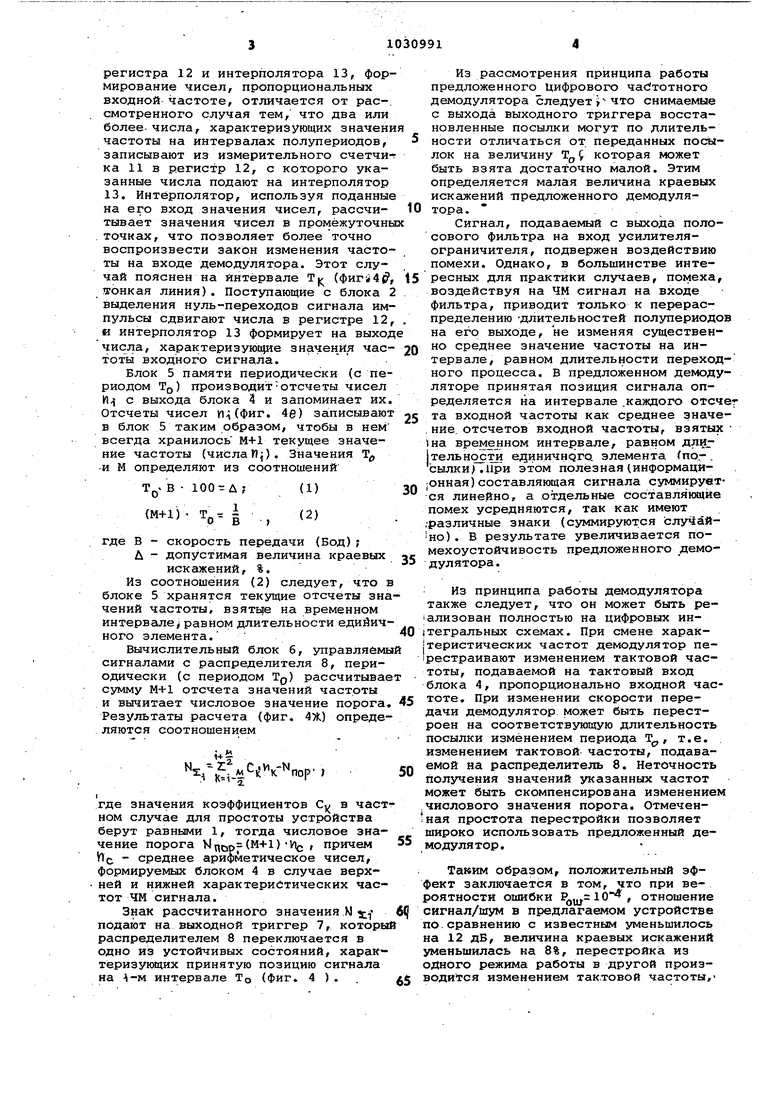

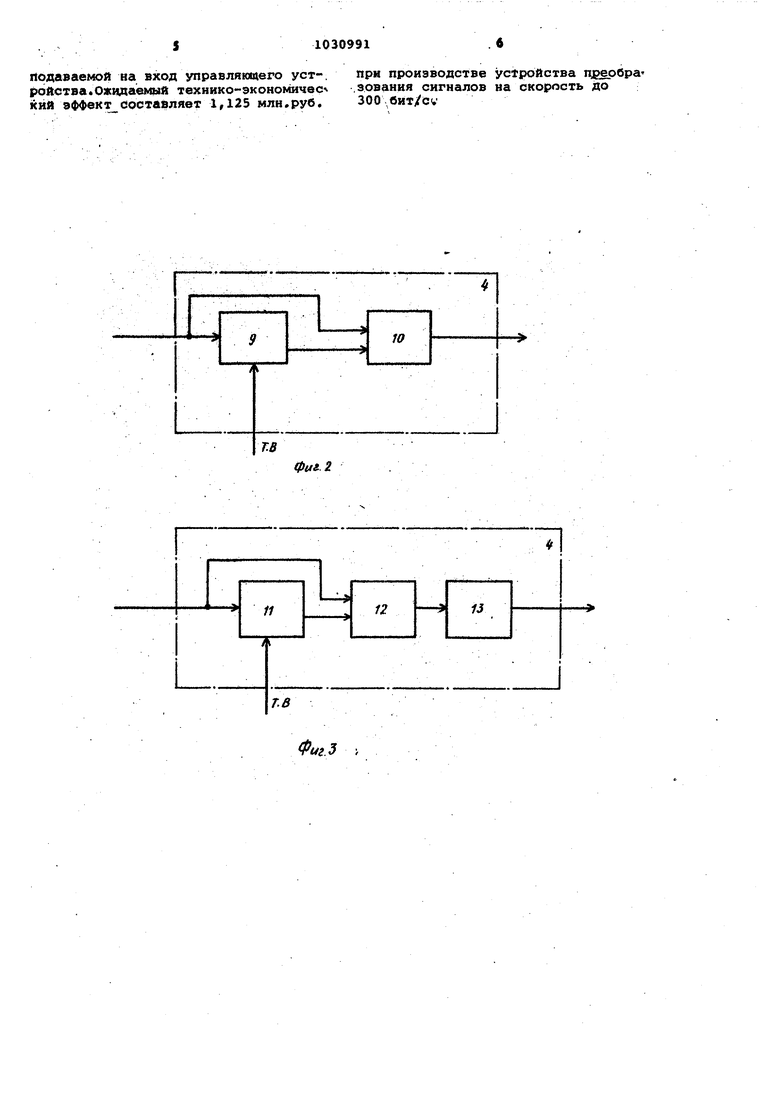

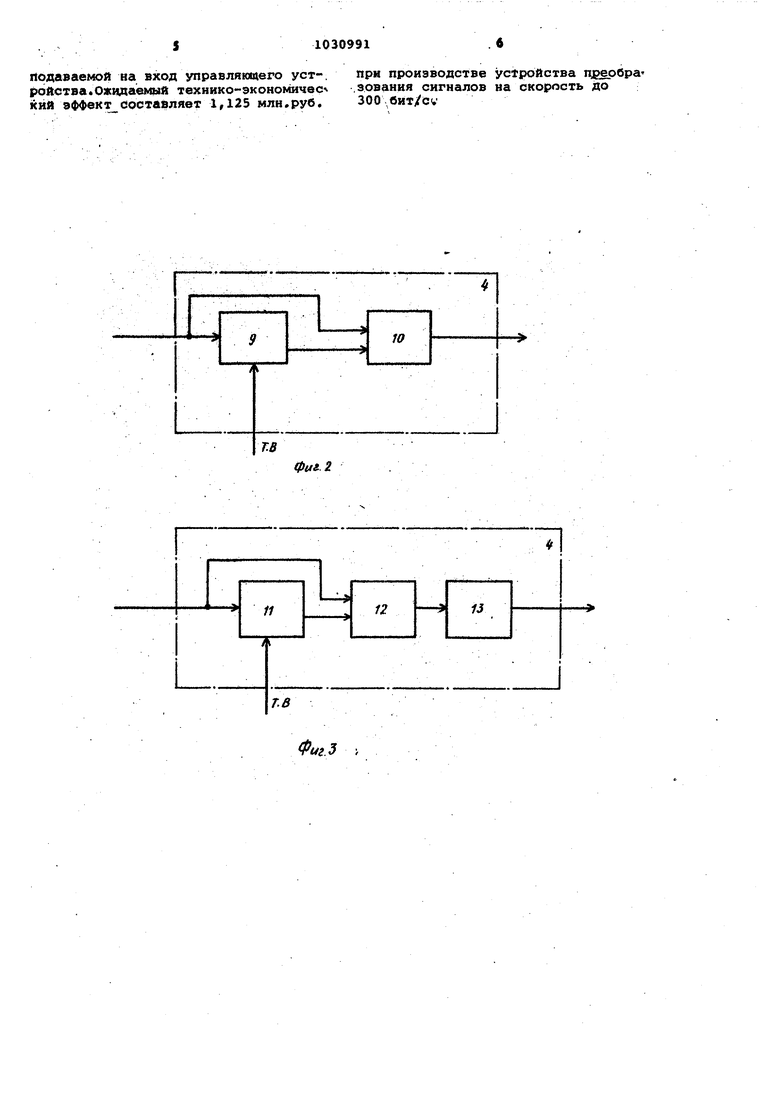

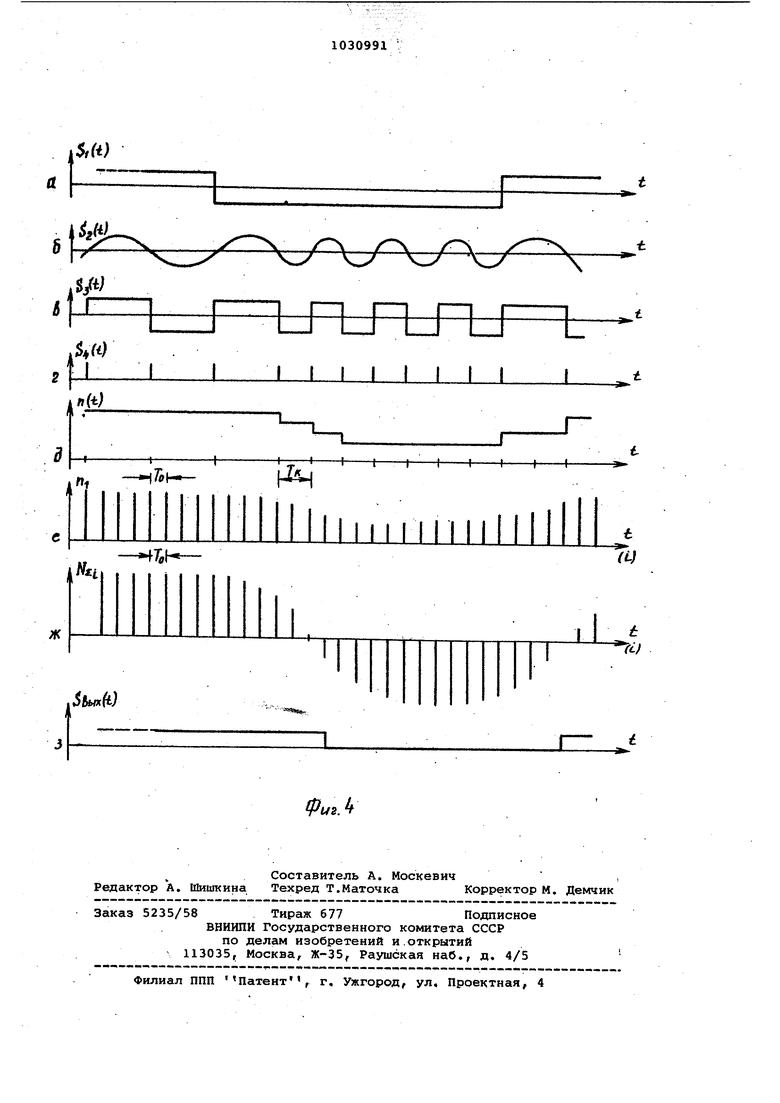

Изобретение относится к техникепередачи данных и может использовать ся в устройствах преобразования сигналов с частотной модуляцией. Известен частотный демодулятор, конструктивно выполненный в виде из мерительного счетчика, входы которо го соединены с блоком выделения нул 4переходов частотно-модулированного (ЧМ) сигнала и задающим . генератором а выходы соединены с блоками, последующей обработки и классификации Cll Однако частотный демодулятор имее недостаточную помехоустойчивость вследствие малой величины разности длительностей полупериодов характёристических частот. Наиболее близким техническим решением к изобретению является цифровой частотный демодулятор, содержащий выходной триггер и последователь но соединенные усилитель-ограничител и блок выделения нуль-переходов сигнала, к второму входу которого подключен выход формирователя тактовых импульсов 2 }. Однако известный цифровой частотный демодулятор имеет низкую помехоустойчивость . Цель изобретения - повышение помехоустойчивости. Для этого в цифровой частотный де модулятор, содержащий выходной триггер и последовательно соединенные усилитель-ограничитель и блок выделения нуль-переходов сигнала, к второму входу которого подключен выход формирователя тактовых импульсов, введены распределитель импульсов и последовательно соединенные блок формирования цифрового сигнала, блок памяти и вычислительный блок, выход которого подключен к первому входу выходного триггера, при этом дополнительные выходы формирователя тактовых импульсов соединены с первым входом блока формирования цифрового сигнала, второй вход которого соеди нен с выходом блока выделения нульпереходов сигнала и с входом распре..делителя импульсов, выходы которого подключены к вторым входам блока памяти, вычислительного блока и выход ного триггера. При этом блок формирования цифрового сигнала состоит из последовател соединенных измерительного счет чика и элемента буферной памяти, выxojit которого является выходом блока формирования цифрового сигнала, входами которого являются входы измерительного счетчика, один из которых соединен с вторым входом элемента буферной памяти. Причем блок формирования цифрового сигнала состоит из последовательно соединенных измерительного счетика, регистра и интерполятора, выход которого является выходом блока формирования цифрового сигнала, входами которого являются входы измерительного счетчика, один из которых соединен с вторым входом регистра. На фиг. 1 представлена структурная электрическая схема предложенного цифрового частотного демодулятора; на фиг. 2 и 3 - варианты выполнения блока формирования цифрового сигнала; на фиг. 4 - эпюры напряжений, поясняющие работу демодулятора. Цифровой частотый демодулятор содержит усилитель-ограничитель 1, блок 2 выделения нуль-переходов сигнала, формирователь 3 тактовых импульсов, блок 4 формирования цифрового сигнала, блок 5 памяти, вычислительный блок б, выходной триггер 7, распределитель 8 импульсов. Блок формирования цифрового сигнала в первом варианте исполнения (фиг. 2) состоит из измерительного счетчика 9 и элемента 10 буферной памяти. Блок формирования цифрового сигнала ззо втором варианте исполнения (фиг. 3) состоит из измерительного счетчика 11 регистра 12 и интерполятора 13. Цифровой частотный демодулятор работает следующим образом. -Принятый ЧМ-сигнал (фиг. 4б) с выхода полосового фильтра (не показан) поступает на усилитель-ограничитель 1, который преобразует входной сигнал и последовательность прямо угольных импульсов переменной длительности (фиг. 4-6). Блок 2 выделения нуль-переходов сигнала формирует в моменты пересечения входным сигналом нулевого уровня короткие импульсы (фиг. 41) и подает их в блок 4. На фиг. 4б -представлен характер изменения во времени чисел, формируемых на выходе блока 4 в случае, когда он выполнен в виде измерительного счетчика 9, соединенного с элементом 10 буферной памяти (фиг. 2). В этом случае измерительный счетчик подсчетом числа импульсов тактовой частоты на интервале полупериода формирует число, характеризующее зн.ачение частоты на данном полупериоде. Очередной импульс с блока 2 выделения нуль-переходов сигнала записывает полученное число в триггеры элемента 10 буферной памяти и устанавливает измерительный счетчик в исходное состояние. Следующий импульс- нулы перехода изменяет состояние элемента, 10, т.е. число на выходе .блока 4 пропорционально входной частоте, и так с приходом каждого импульса блока 2 выделения нуль-переходов сигнала. В случае, когда блок 4 выполнен в виде последовательно соединенных измерительного счетчика 11 (фиг. 3) регистра 12 и интерполятора 13, формирование чисел, пропорциональных входной- частоте, отличается от рас-. cjMOTpeHHoro случая тем, что два или более-числа, характеризующих значени частоты на интервалах полупериодов, записывают из измерительного счетчи- ка 11 в регистр 12, с которого указанные числа подают на интерполятор 13. Интерполятор, используя поданные на его вход значения чисел, рассчитывает значения чисел в промежуточны . точках, что позволяет более точно воспроизвести закон изменения частоты на входе демодулятора. Этот случай пояснен на интервале Т|/ (, гонкая линия). Поступающие с блока 2 выделения нуль-переходов сигнала импульсы сдвигают числа в регистре 12, и интерполятор 13 формирует на выход числа, характеризую1цие значения частоты входного сигнала. Блок 5 памяти периодически (с периодом TO) производитОтсчеты чисел И с выхода блока 4 и запоминает их. Отсчеты чисел . 4е) записывают г- .. в блок 5 таким образом, чтобы в нем всегда хранилось М+1 текущее значение частоты (числа П|). Значения Т -и М определяют из соотношений 100-Д ; , Т - i где В - скорость передачи (Бод); Д - допустимая величина краевых искажений, %. Из соотношения (2) следует, что в блоке 5 хранятся текущие отсчеты значений частоты, взятые на временном интервале равном длительности едийичного элемента Вычислительный блок 6, управляемы сигналами с распределителя 8, периодически (с периодом TQ) рассчитывае сумму М+1 отсчета значений частоты и вычитает числовое значение порога, Результаты расчета (фиг. 4Ж) определяются соотношением s «CjV nnP 1 I(,i W К К пор ) где значения коэффициентов С в частном случае для простоты устройства берут равными 1, тогда числовое значение порога ()Ир , причем с. среднее арифметическое чисел, формируемых блоком 4 в случае верхней и нижней характеристических частот ЧМ сигнала. Знак рассчитанного значения М подают на выходной триггер 7, который распределителем 8 переключается в одно из устойчивых состояний, характеризующих принятую позицию сигнала на интервале TO (фиг. 4 ) . Из рассмотрения принципа работы предложенного Цифрового частотного демодулятора следует г что снимаемые с выхода выходного триггера восстановленные посылки могут по длительности отличаться от переданных посылок на величину Т, { которая может быть взята достаточно малой. Этим определяется малая величина краевых искажений -предложенного демодулятора. . . Сигнал, подаваемый с выхода полосового фильтра на вход усилителяограничителя, подвержен воздействию помехи. Однако, в большинстве интересных для практики случаев, помеха, воздействуя на ЧМ сигнал на входе фильтра, приводит только к перераспределению-длительностей полупериодов на его выходе, не изменяя существен ° среднее значение частоты на интервале, равном длительности переход-ного процесса. В предложенном демодуляторе принятая позиция сигнала определяется на интервале .каждого отсчет та входной частоты как среднее эначение. отсчетов входной частоты, взятых )на временном интервале, равном дли 1тельности еданичндго. элемента (по-. сылки.11ри этом полезная (информацй;онная)составляющая сигнала суммируется линейно, а отдельные составляняцие помех усредняются, так как имеют /различные знаки (суммируются слу«1айно). В результате увеличивается помехоустойчивость предложенного демодулятора. Из принципа работы демодулятора также следует, что он может быть ре ализован полностью на цифровых ин(тегральных схемах. При смене харак|теристических частот демодулятор перестраивают изменением тактовой частоты, подаваемой на тактовый вход блока 4, пропорционально входной част - При изменении скорости пере демодулятор может быть перестроен на соответствующую длительность посылки изменением периода Т.,, т.е. . изменением тактовой частоты, подаваемой на распределитель 8. Неточность получения значений указанных частот может быть скомпенсирована изменением числового значения порога. Отмеченная простота перестройки позволяет широко использовать предложенный демодулятор. Таким образом, положительный эффект заключается в том, что при вероятности ошибки , отношение сигнал/шум в предлагаемом устройстве по. сравнению с известнЕЛМ уменьшилось на 12 дБ, величина краевых искажений 1лченьшилась на 8%, перестройка из одного режима работы в другой производятся изменением тактовой частоты,S1030991.

йодаваемой на вход управляющего уст-. при производстве устройства деербра ройства.Ожидаемый технико-экономичес- .зования сигналов на скорость до кий эффект составляет 1,125 млн.руб. 300 бит/cv

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| Устройство для демодуляции частотно-манипулированных сигналов | 1987 |

|

SU1450127A1 |

| Цифровое устройство измерения частоты | 1988 |

|

SU1677653A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| Цифровой когерентный частотно-фазовый демодулятор | 1979 |

|

SU873453A1 |

| Способ демодуляции синхронного двоичного частотно-манипулированного сигнала | 1980 |

|

SU999174A1 |

| Способ тактовой синхронизации приемника двоичного частотно-модулированного сигнала и устройство для его осуществления | 1980 |

|

SU1361727A1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| Синтезатор частотно-модулированных сигналов | 1984 |

|

SU1239833A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

1. ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕМОДУЛЯТОР, содержащий выходной триггер и последовательно соединенные усилите ль -6 граничите ль и блок вЁаделения нуль-переходов сигнала, к второму входу которого подключен выход формирователя Тактовых импульсов, о тл ичающийся тем, что, с целью повышения помехоустойчивости, в негчэ введены распределитель импульсов и последовательно соединенные блок формирования цифрового сигнала, блок памяти и вы 1ислительный блок, выход которого подключен к первому входу выходного триггера, при этом дополнительные выходы формирователя тактовых импульсов соединены с пе1рвым входом блока формирования цифрового сигнала, второй вход которого соеди- ней с выходом блока выделения нульпереходов сигнала и с входом распре:делителя импульсов, выходы которого подключены к вторьм входгкм блока паг мяти, вычислительного блока- и выходного триггера. . 2.Устройство по п. 1, о т л и чающееся, тем, что.блок формирования цифрового сигнала состоит из последовательно соединенных измерительногчэ счетчика и элемента бу:фернОЙ памяти, выход которого является выходом блока формирования цифрового сигнала, входами которого являются входы измерительного счетчика один из которых соединен с вторалм входом элемента буферной памяти. 3,Устройство по п. 1, о т л и ч: ai ю щ е ее я тем, что блок формирования цифрового сигнала состоит из последовательно соединенных измерительного, счетчика, регистра к интерполятора, выход которого является выходом блока формирования цифрового О сигнала, входами которого являются входы измерительного счетчика, один 00 о из которых соединен с вторым входом ;регистра.. :О :0

Фиг 5 : я1 ЛЛ S ЬУ f Xfi) Л i I I I I I I f,(t) f-r-I11--t-- |J/H

n liiiinil

,Н-

rt-; / /уI I I I i i 11H

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3908169, кл | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Шляпоберский В.И | |||

| Основы техники передачи дискретных сообщений | |||

| М., Связь, 1973, с | |||

| Кулиса для фотографических трансформаторов и увеличительных аппаратов | 1921 |

|

SU213A1 |

Авторы

Даты

1983-07-23—Публикация

1981-10-21—Подача