«

СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации блочных кодов | 1989 |

|

SU1688434A1 |

| Устройство для исправления ошибок | 1988 |

|

SU1547081A1 |

| Устройство для выбора заданного числа повторений двоичных чисел | 1984 |

|

SU1267402A1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Устройство для сортировки информации | 1986 |

|

SU1386989A2 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Цифровой формирователь манипулированных сигналов | 1982 |

|

SU1019663A1 |

| Процессор матричной вычислительной системы | 1987 |

|

SU1603395A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

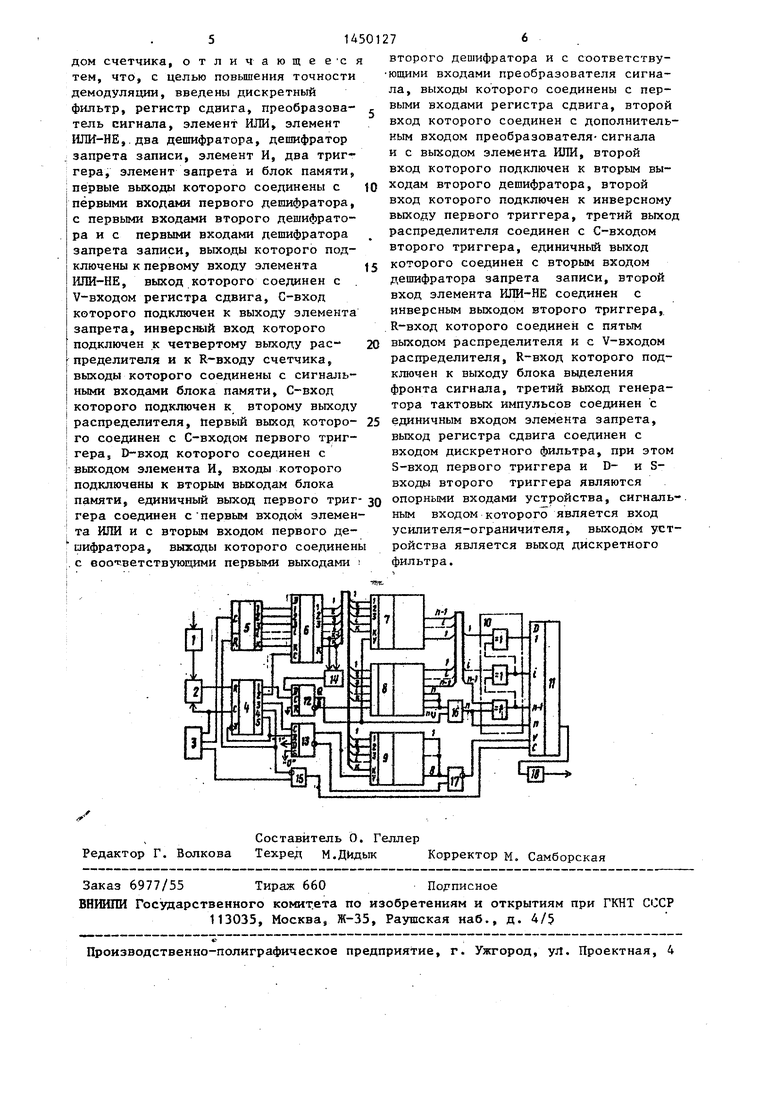

Изобретение относится к радиотехнике. Цель изобретения - повьппение точности демодуляции. Устр-во содержит усилитель-ограничитель 1, блок 2 вьщеления фронта сигнала, г-р 3 тактовых импульсов, распределитель 4, счетчик 5, блок 6 памяти, дешифрато ры 7 и 8, дешифратор 9 запрета записи, преобразователь 10 сигнала, регистр 11 сдвига, триггеры 12 и 13, зл-т И 14, эл-т 15 запрета, эл-т ИЛИ 16, эл-т ИЛИ-НЕ 17 и дискретный фильтр 18. Частотно-манипулированный сигнал, соответствующий передаваемой информации, преобразуется в короткие импульсы, которые распределяются по цепям для осзга1ествления развязки работы во времени эл-тов устр-ва. После четкого определения признака длительности полупериода высокой или низкой частоты входного сигнала осуществляется воспроизведение передаваемой информации. 1 ил. с 9 (Л

IND

Изобретение относится к радиотехнике и может быть использовано в системах передачи дискретной информации.

Цель изобретения - повышение точ- ности демодуляции.

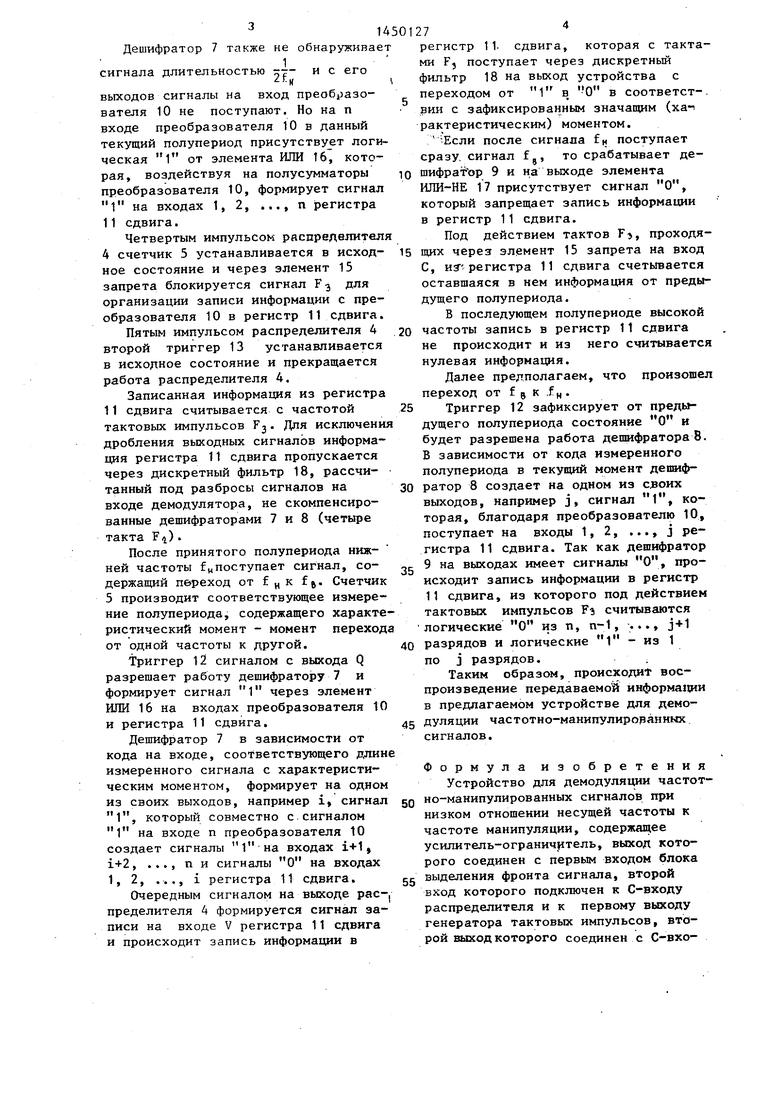

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство для демодуляции частоТ Ю jHo-манипулированных сигналов содержит усилитель-ограничитель 1, блок 2 выделения фронта сигнала, генератор 3 тактовых импульсов, распределитель 4, счетчик 5, блок 6 памяти, первый 7 и 15 второй 8 дешифраторы, дешифратор 9 запрета записи, преобразователь 10 сигнала, регистр 11 двига, первый 12; и второй 13 триггеры, элемент И 14, элемент 15 запрета, элемент ИЛИ 16, 20 элемент ИЛИ-НЕ 17 и дискретный

ФИЛЬТР 18.

Устройство работает следующим

образом.

Частотно-манийулированный (ЧМ) 25 сигнал, соответствующий передаваемой информации, принятый из канала связи и ограниченный по спектру полосовьм фильтром (не показан) поступает на вход усилителя-ограничителя 1, кото- 30 рый преобразует напряжение синусоидальной формы в импульсы по форме близкие к прямоугольным. Блок 2 выделения фронта сигнала вырабатывает при поступлении сигнала от усилите- 35 ля-ограничителя 1 короткие импульсы в момент перехода ЧМ-сигналов через нулевой уровень. Генератор 3 тактовых импульсов подает высокую частоту F, на вход блока 2 выделения фронта 40 сигнала и вход С распределителя 4, который удерживается в исходном сое- стоянии сигналом на входе V. Распределитель 4 с приходом импульса от блока 2 вьщеления фронта сигнала на 45 вход R устанавливается в исходное состояние и осуществляет.распределение коротких имйульсов по цепям, подключенным к входам 1, 2, ..., 5, и производит таким образом развязку Q работы по времени элементов устройства. Импульсом с первого выхода распределителя 4 производится запись в первый триггер 12 значения признака сигнала предыдущего полупериода, пос-д тупающего из блока 6 пямяти через элемент И 14. Входы элемента И 14 подключены к блоку 6 памяти таким образом, чтобы четко определялся признак длительности полупериода высокой или низкой частоты входного сигнала. Например, при построении устройства частотно-манипулированных сигналов частотами f н 1300 Гц, f 8 210СГц, соответствующие логическим 1 и О передаваемой информации, при использовании генератора тактовых частот с F, 307,2 кГц; ,6 кГц; РЗ 38,4 кГц счетчик 5 имеет шесть разрядов, определенных из выражения

„ - Рг

К L,g,.

Следовательно пятый и шестой разряды счетчика 5 несут информацию о признаке длительности,полупериода. Если пятый разряд равен О , а шестой разряд равен 1, то регистрируется сигнал с длительностью полупериода верхней частоты fe 2100 Гц, а если пятый и шестой разряды равны 1, то регистрируется сигнал нижней частоты fw - 1300 Гц.

Первым сигналом с первого выхода распределителя 4 информация признака предыдущего сигнала из блока 6 памяти черй элемент И 14 записывается в триггер 12.

Предположим, что на вход устройства поступшот сигналы нижней частот fц, тогда в триггер 12 первым сигналом с распределителя 4 записана 1 и с выхода Q триггера 12 поступает сигнал на вход V дешифратора 7, разрешая ему работу, и на вход элемента ИЛИ 16. Импульсом, поступающим со второго выхода распределителя 4 на С-вход блока 6 памяти, производится перенос со счетчика 5 результата измерения полупериода входного сигнала в блок 6 памяти. I

Импульсом с третьего выхода распределителя 4 второй триггер 13 переключается в состояние 1 и сигналом с выхода Q разрешается работа дешифратора 9 запрета записи. Если в блок 6 памяти было записано текущее значение полупериода нижней частоты ц, то на выходах дешифратора 9 сигналы отсутствуют.

Элемент ИЛИ-НЕ 17 имеет на входах сигналы логического О, а на выходе - 1, которая, поступая на вход V регистра 11 сдвига, разрешает запись информации в него.

Дешифратор 7 также не обнаруживает

сигнала длительностью :;т- и с его

-н

выходов сигналы на вход преобразо- вателя 10 не поступают. Но на п входе преобразователя 10 в данный текущий полупериод присутствует логическая 1 от элемента ИЛИ 16, которая, воздействуя на полусумматоры преобразователя 10, формирует сигнал 1 на входах 1, 2, .... п регистра 11 сдвига.

Четвертым импульсом распределителя

4счетчик 5 устанавливается в исход- нее состояние и через элемент 15 запрета блокируется сигнал F-j для организации записи информации с преобразователя 10 в регистр 11 сдвига.

Пятым импульсом распределителя 4 второй триггер 13 устанавливается в исходное состояние и прекращается работа распределителя 4.

Записанная информация из регистра 11 сдвига считывается с частотой тактовых импульсов Fj. Для исключения дробления вькодных сигналов информация регистра 11 сдвига пропускается через дискретный фильтр 18, рассчитанный под разбросы сигналов на входе демодулятора, не скомпенсированные дешифраторами 7 и 8 (четыре такта F).

После принятого полупериода нижней частоты „поступает сигнал, со- держащий переход от f „к f. Счетчик

5производит соответствукицее измере- ние полупериода, содержащего характеристический момент - момент переход от одной частоты к другой.

Триггер 12 сигналом с выхода Q разрешает работу дешифратору 7 и формирует сигнал 1 через элемент ИЛИ 16 на входах преобразователя 10 и регистра 11 сдвига.

Дешифратор 7 в зависимости от кода на входе, соответствующего длин измеренного сигнала с характеристическим моментом, формирует на одном из своих выходов, например i сигнал 1, который совместно с.сигналом 1 на входе п преобразователя 10 создает сигналы 1 на входах i+1, i+2, ..., пи сигналы О на входах 1, 2, ..., i регистра 11 сдвига.

Очередным сигналом на выходе pacпределителя 4 формируется сигнал записи на входе V регистра 11 сдвига и происходит запись информации в

27

регистр 11. сдвига, которая с тактами F, поступает через дискретный фильтр 18 на выход устройства с

переходом от

Ч в О в соответстВИИ с зафиксированным значащим (xa-i рактеристическим) моментом.

-Если после сигнала и поступает сразу, сигнал fj, то срабатывает де- шифрат ор 9 и на выходе элемента ИЛИ-НЕ 17 присутствует сигнал О, который запрещает запись информации в регистр 11 сдвига.

Под действием тактов F, проходящих через элемент 15 запрета на вход С, и регистра 11 сдвига счетывается оставшаяся в нем информация от предыдущего полупериода.

В последующем полупериоде высокой частоты запись в регистр 11 сдвига не происходит и из него считывается нулевая информация.

Далее предполагаем, что произошел переход от f к .f.

Триггер 12 зафиксирует от предыдущего полупериода состояние О и будет разрешена работа дешифратора 8.

8зависимости от кода измеренного полупериода в текувщй момент дешифратор 8 создает на одном из сзоих выходов, например j, сигнал 1, которая, благодаря преобразователю 10, поступает на входы 1, 2, ... j регистра 11 сдвига. Так как дешифратор

9на выходах имеет сигналы О, происходит запись информации в регистр 11 сдвига, из которого под действием тактовых импульсов э считываются логические О из и, п-1, ... J+1 разрядов и логические 1 - из 1

по j разрядов.

Таким образом, происходит воспроизведение передаваемой информации в предлагаемом устройстве для демодуляции частотно-манипулироранных сигналов.

Формула изобретения

Устройство для демодулявдш частот но-манипулированных сигналов при низком отношении несущей частоты к частоте манипуляции, содержащее усилитель-ограничитель, выход которого соединен с первым входом блока выделения фронта сигнала, второй вход которого подключен к С-входу распределителя и к первому выходу генератора тактовых импульсов, второй выход которого соединен с С-вхочш-

| Шляпоберский В.И | |||

| Основы техники передачи дискретных сообщений | |||

| - М.: Связь, 1973, с | |||

| Кулиса для фотографических трансформаторов и увеличительных аппаратов | 1921 |

|

SU213A1 |

Авторы

Даты

1989-01-07—Публикация

1987-04-06—Подача