. 1

Изобретеиме относится к радиотехнике и может быть использовано., для синтеза частотно-моду.пированных (ЧМ) сигналов.

Целью из.обретения является уменьг шение шага сеткн частот и увеличение скорости изменения частоты.

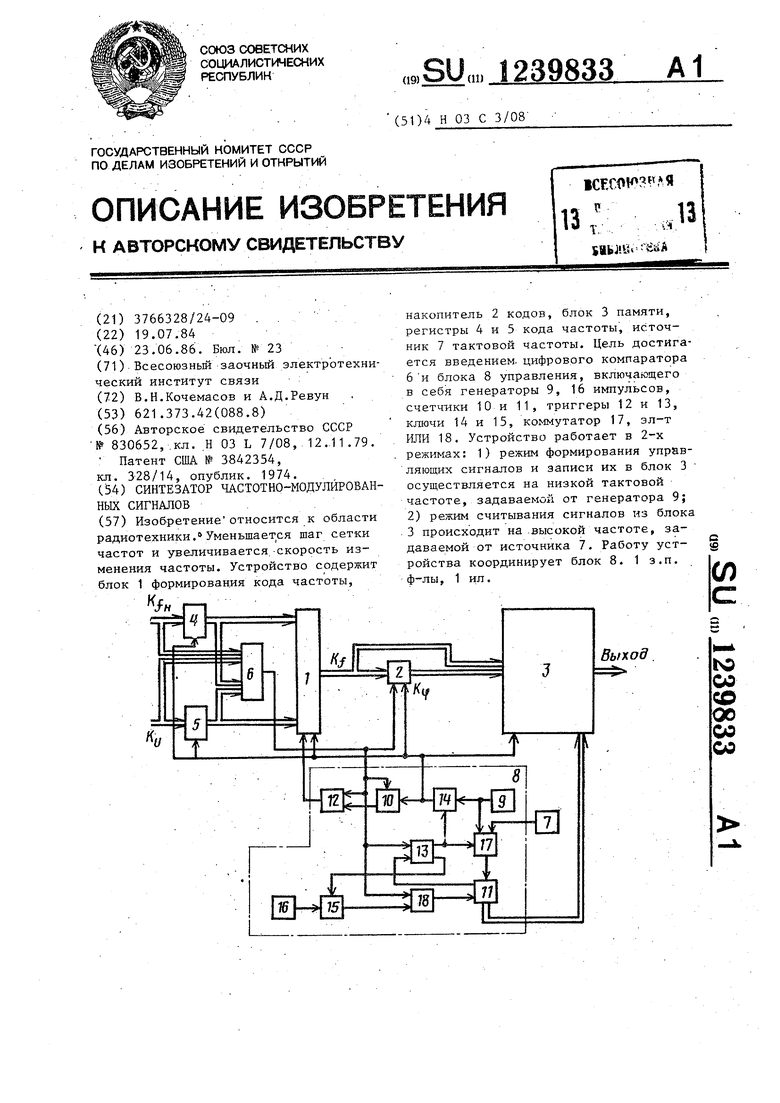

На чертеже представлена структурная электрическая схема синтезатора частотно-модулированных сигналов.

Схема содержит блок 1 формирования кода частоты, накопитель 2 кодов блок 3 памяти, первый регистр 4 кода частоты, второй регистр 5 кода частоты, цифровой компаратор 6, источник 7 тактовой частоты, блок 8 управления При этом блок 8 управле ния включает в себя первьш генератор 9 импульсов, первый Ю и второй 11 счетчики, первый 12 и второй 13 триггеры, первый 14 и второй 15 ключи, второй генератор 16 импульсов, коммутатор 17 и элемент ИЛИ 18,

Синтезатор ЧМ сигналов работает следующим образом. .

Синтезатор ЧМ сигналов предназначен для формирования ЧМ сигналов с начальной частотой f, скоростью изменения частоты V и длительностью, определяемой импульсами, поступающи- и от второго генератора 16 импульсов. Непосредственному формированию ЧМ сигналов при предложенном выполнении блока 8 управления предшествует время , где N, - коэффициент счета первого счетчика 11, f. - частота источника тактовой частоты 7, в течение которого коды, формируемые синтезатором частотно-модулированных сигналов, соответствуют сигна лу фиксированной частоты f,., Такой участок обычно требуется исходя из условий обработки, а также для того чтобы свести к минимуму переходные процессы в момент начала формирования собственно ЧМ сигнала. Это обстоятельство в значительной степени и определяет структуру блока 8 управления ,

Синтезатор ЧМ сигналов работает в двух режимах режиме формирования управЛяюгцих сигналов и записи их в блок 3 памяти и режиме считывания управляющих сигналов из блока 3 памяти .

Формирование и запись управляющих сигналов в блок 3 памяти осуществляется на низкой тактовой частоте, за39ВЗЗ ..2

даваемой от первог-о генератора 9 импульсов. Считывание управляющих сигна.пов из б.пока 3 памяти происходит на высокой частоте, задав.аемой от источника 7, при постуллентш импульса от второго генератора 16 импульсов, определяющего длитель}гость формируемых ЧМ сигналов. Работу синтезатора сигналов в двух режимах 0 координирует блок 8 управления.

В момент изменения кода начальной частоты V. f в первом регистре 4 или кода скорости ЧМ К во втором регистре 5 в гщфровом компараторе 6 форми- 5 руется командный импульс, который

переводит устройство в режим формирования yпpaвляюm x сигналов и записи их в блок 3 .памяти. По этому импульсу осуществляется установка нуля на- 0 копителя 2 кодов первого счетчика 10 через элемент ИЛИ 18 второго счетчика 1 1 и через первый триггер 12, блок 1 формирования кода частоты, на выходе которого при этом присутству- 5 ет код начальной частоты Кг , Кроме того, этот импульс изменяет состоя - ние второго триггера 13, в результате чего обеспечивается прохождение тактовых импульсов с выхода первого 30 генератора 9 импульсов на счетные входы первого 10 и второго 11 счетчиков, а также на тактовые входы первого регистра 4, второго регистра 6, блока 1 формирования, накопителя 2 кодов и на вход разрешения записи

35

блока 3 памяти„

С приходом этих тактовых импульсов на первый 10 и второй 11 счетчики их содержимое начинает увеличиваться и в блоке 3 памяти по адресу, формируемому во втором счетчике 11, записывается по информационному входу код текущей частоты- .К j. К j. и код фазы К с выхода накопителя 2 кодов. При поступлении импульса на вход первого счетчика 10 происходит его переполнение, первый триггер. 12 меняет свое состояние и с блока 1 формирования снимается команда

установки нуля,. При этом на выходе блока 1 формирования начинает формироваться код Кг К + i- 1, 2, 3...;, , , Емкость N второго счетчика 11 и совпадающее с

ней число адресов блока 3 памяти выбирается такой,, чтобы обеспечить формирование линейных ЧМ сигналов максимально необходимой длитепьности

Т.„КС (Na Ч).ц Общая мак- симальная длительность сигнала с учетом времени, в течение которого в

блок 3 памяти записываются коды К

t.

и К, формируемые на участке с фиксированной частотой, равна

.макс.

при переполнении второго счетчика 11, наступающем с приходом от первого генератора 9 импульсов Н,го тактового импульса, второй триггер 13 изменяет свое состояние, в результате чего первый ключ 14 блокирует поступление импульсов на счетный вход первого счетчика ГО, коммутатор 17 подключает счетный вход второгр счетчика 11 к источнику 7, второй ключ 15 открывается, второй счетчик 11 через элемент ИЛИ 18 устанавливается в нулевое состояние, чем обеспечивает перевод устройства в режим считывания управляющих сигна йов из блока 3 памяти.

Считывание управляющих сигналов .из блока 3 памяти осуществляется во время появления стробов длительнос- тью Т,,,; .

При этом содержимое второго счетчика 11 с приходом каждого импульса от источника 7 начинает возрастать, в результате чего из блока 3 памяти последовательно извлекаются записанные в него коды управления К и К,. По окончании стробов второй счетчик 11 каждый раз устанавливается в нуле JBoe состояние. Работа устройства, в . этом режиме продолжается до тех пор, пока не изменится хотя бы один из входных кодов К. или К;,.

Цифровой компаратор 6 предназначен для формирования командного импульса, переводящего синтезатор в режим формирования, управляющих кодов и их записи в блок 3 памяти. Перевод в этот режим осуществляется каждьй раз, когда происходит изменение одного из кодов K и/или К. Цифровой компаратор 6 имеет два входа, на один из которых по параллельным шинам подаются коды К и К с входа синтезатора сигналовJ на другой - эти же коды, но после задержки их -на такт в первом 4 и втором 5 регистрах Командный импульс в цифровом компараторе 6 формируется каждый раз, когда хотя бы один из разрядов кодов Kj или Ку претерпевает изменение. Технически такой цифровой компаратор

может быть реализован на типовых мик росхемах, причем число анализируемых разрядов может наращиваться.

Второй генератор 16 импульсов - 5 это обычный генератор импульсов,

длительность которого определяет длительность формируемых ЧМ сигналов. Выход предлагаемого синтезатора сигналов може.т быть использован для 10 обращения к постоянному запоминающему устройству (ПЗУ), в котором записана таблица значений синусоидальной функции для управления фазовращателем яли для управления работой дроб- 15 ного делителя с переменным коэффициентом деления (на чертеже не показано) .

Применение предлагаемого устройст- 2Q ва позволяет формировать ограниченные во времени сигналы с высоким разрешением по частоте и скорости частотной модуляции.

25 Фор мула изобретения

1 . Синтезатор частотно-модулиро-.i ванньгх сигналов, содержащий последовательно соединенные первый ре- 2„ гистр кода частоты, блок формирования кода частоты и накопитель кодов, кодовый в ыход которого соединен с первой группой информационных входов блока памяти, второй регистр кода частоты, выход которого подключен к второму кодовому входу блока формирования кода частоты, и источник тактовой частоты, отличающий- с я тем, что, с целью уменьщения шага сетки частот и увеличения скорости изменения частоты, в него введены цифровой компаратор и блок управления, при этом входы первого и второго регистров кода частоты под- . кгаочены к п.ервому входу цифрового 5 компаратора, к второму входу которого подключены выходы первого и второго регистров кода частоты, вход установки нуля накопителя кодов объединен с входом установки нуля блока 50 управления и подключен к выходу цифрового компаратора, выход источника тактовой частоты соединен с тактовым входом блока управления, первый выход которого соединен с входом уста- 55 новки нуля блока формирования кода частоты, тактовые входы первого и второго регистров кода частоты, бло- ка формирования кода частоты, накопи35

40

теля кодов и -блока памяти объединены и подключены к второму выходу блока управления, кодовый выход которого соединен с адресным входом блока па- мяти, вторая группа информационных входов которого подключена к выходу блока формирования кода частоты.

.2. Синтезатор по.п. 1, отличающийся тем, что блок управ- ления содержит последовательно соединенные первый генератор импульсов, первый ключ , первый счетчик и пер- . вьм триггер, выход которого является первым выходом блока управления, по- следовательно соединенные второй генератор импульсов, второй ключ, элемент ИЛИ, второй счетчик, второй триггер и коммутатор, при. этом yQTa- новочный вход первого счетчика, вто- Редактор А.Шандор Заказ 3407/55

Составитель Ю.Ковалев- .

Техред О.Сопко Корректор- Е. Сирохман

ЗГираж 816 .Подписное

ВНИЖШ Государственного комитета СССР .

по делам из обретений и- открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4.

рой вход первого триггера, второй вход второго триггера и второй вход элемента И.ПИ объединены и являются входом установки нуля блока управления, второй вход первого ключа сое- . динен с первым выходом второго триггера, второй выход которого подключен к второму входу второго ключа, выход первого генератора импульсов соединен также с первым сигнальным входом коммутатора, второй сигнальный вход которого .является тактовым входом блока управления, выход коммутатора соединен со счетным входом второго счетчика, поразрядные выходы которого являются кодовым выходом, блока управления, а выход первого .ключа - вторым выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Цифровой синтезатор частот с высокой линейностью закона изменения частоты | 2016 |

|

RU2635278C1 |

| ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1992 |

|

RU2033685C1 |

| Цифровой синтезатор с М-образным законом изменения частоты | 2017 |

|

RU2682847C1 |

| Цифровой вычислительный синтезатор двухчастотных сигналов | 2019 |

|

RU2710280C1 |

| ИЗМЕРИТЕЛЬНЫЙ ГЕНЕРАТОР ПАРНЫХ ИМПУЛЬСОВ | 2022 |

|

RU2788980C1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Цифровой синтезатор сигналов | 1988 |

|

SU1525694A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

Изобретение относится к области радиотехники.Уменьшается шаг сетки частот и увеличивается.-скорость изменения частоты. Устройство содержит блок 1 формирования кода частоты, накопитель 2 кодов, блок 3 памяти, регистры 4 и 5 кода частоты, ник 7 тактовой частоты. Цель достигается введением, цифрового компаратора 6 и блока 8 управления, включающего в себя генераторы 9, 16 импульсов, счетчики 10 и 11, триггеры 12 и 13, ключи 14 и 15, коммутатор 17, эл-т ИЛИ 18. Устройство работает в 2-х режимах: 1) режим формирования управляющих сигналов и записи их в блок 3 осуществляется на низкой тактовой частоте, задаваемой от генератора 9; 2) режим считывания сигналов из блока 3 происходит на высокой частоте, задаваемой от источника 7. Работу устройства координирует блок 8. 1 з.п. ф-лы, 1 ил. с « (Л Вьтод tc со со 00 со со

| Синтезатор частот | 1979 |

|

SU830652A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3842354, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1986-06-23—Публикация

1984-07-19—Подача