Изобретение относится к устройствам автоматики и вычислительной технике и может быть использовано Б системах контроля и управления различными промышленными объектами допускающими импульсное регулирование параметров, в системах автоматизированного управления научными экспериментами, а также в гибридных вычислительных -системах, Бк;лючающих универсальные ЭЦВМ.

Известен преобразователь кодов во временной интервал большой и средней длительности, содержащий генератор импульсов, вентиль, счетчик, дешифратор, линию задержки и управляющий триггер. При этом преобразуемое число вводится в счетчик устройства в обратном коде, а затем складывается с импульсами генератора до получения импульса переполнения на старшем разряде счетчика Cll.

К недостаткам: данного преобразователя следует отнести значительные погрешности, обусловленные нестабильностью частоты опорного генератора импульсов, рассогласованием фаз импульсов опорного генератора и старт-импульса и задержкой в тракте формирования конца временного интервала, а также ограниченные функциональные возможности преобразования, связанные, в частности с ограниченными возможностями масштабирования временного интервала, в силу использования генератора фиксированной частоты, с невозможностью менять характер преобразования числа в- силу фиксированной структуры устройства и определенного кода исходного числа. Кроме того техническая реализация преобразователя относительно сложна.

Известен также преобразователь чисел в длительность межимпульсных интервалов, содержащий генератор импульсов, счетчики, триггер управления, логические элементы и управляющий коммутатор, входы которого соединены соответственно с выходами дополнительного счетчика и выходами источника информации, а выход - с разрешающим .входом триггера управления и с первым входом второго элемента И, второй вход которого подключен к шине запуска и входу установки нуля дополнительного счетчика импульсов, а выход к первому входу элемента ИЛИ, второ вход которого соединен с инверсным выходом триггера управления, а выход - с вторым входом первого элемента И и с выходом устройства, выход счетчика импульсов подключен к его входу записи и единичному входу триггера управления, счетный вход которого соединен с выходом

генератора импульсов, а прямой выход - с входом дополнительного счет-1 чика импульсов, установочные входы счетчика импульсов подключены к выходам источника информации С 2. 5 Недостатками указанного преобразователя являются ограниченные возможности масштабирования временного интервала между импульсами на его выходе и сложность технической реализации в силу значительного числа составляющих его компонентов. Цель изобретения - расширение функциональных возможностей.

Поставленная цель достигается

5 тем, что в преобразователь чисел в длительность межимпульсных интервалов, содержащий счетчик импульсов, первый дешифратор, выход которого подключен к единичному входу управляющего триггера, единичный выход которого соединен с входом первого формирователя импульсов, выход которого подключен к выходной |шине, введены регистр адреса оперативного запоминающего устройства,

5 сумматор, второй дешифратор и второй формирователь импульсов, при этом входы сумматора соединены с соответствующими входными шинами, а выходы соответственно подключены к первому входу п ервого дешифратора и первому входу регистра оперативного запоминающего устройства, выход которого подключен к второму входу первого дешифратора,

5 выход которого соединен со счетным .входом счетчика импульсов, вход ус1тановки нуля которого соединен с I нулевым выходом.управляющего триггера, а выход - с входом второго де-;

,, шифратора, выход которого через второй формирователь импульсов подключен к нулевому входу управляющего .триггера, шине сброса и входам установки нуля счетчийа импульсов, : сумматора и регистра адреса оперативного запоминающего устройства.

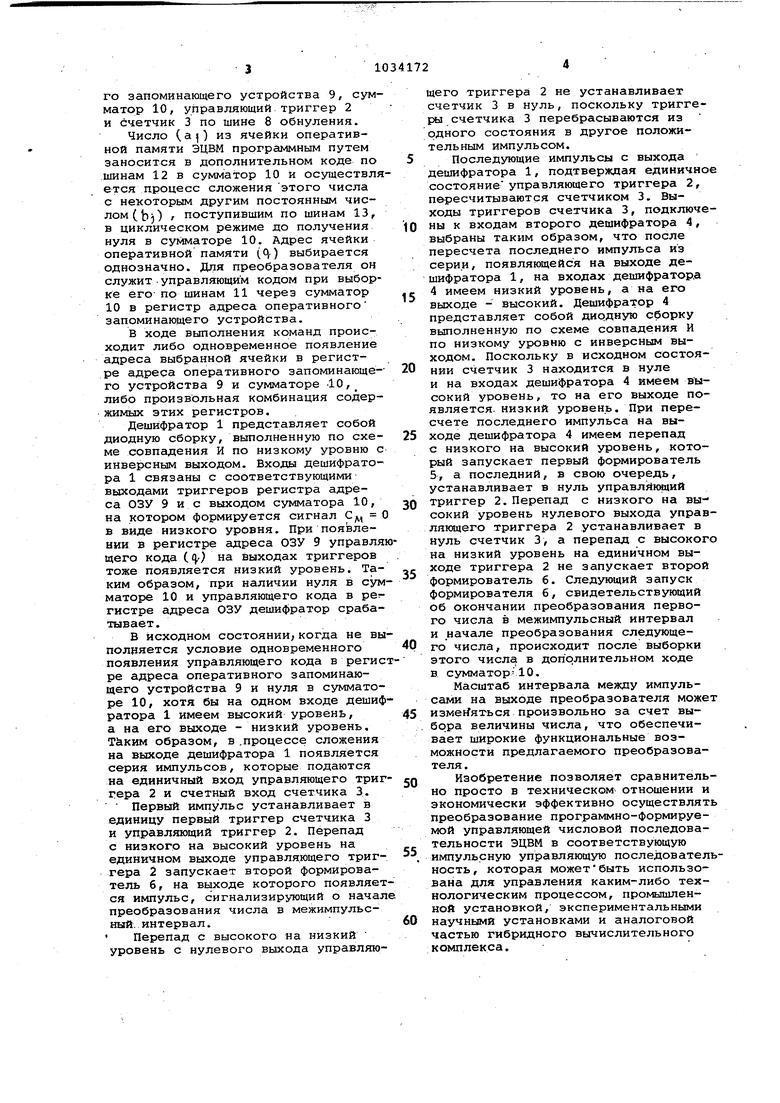

На чертеже показана структурная электрическая схема предлагаемого преобразователя.

Q Преобразователь содержит дешифратор 1, управляющий триггер 2, счетки 3, второй дэпифратор 4, формирователь 5 и 6 импульсов, выходную шину 7,- шину 8; регистр адреса oneijaтивного запоминающего устройства (.ОЗУ) 9, сумматор (СМ 10 и входные шины 11 - 13.

Устройство 9, сумматор 10 и шины 8, 11, 12 и 13, обведенные штриховой линией, могут входить в сое0 тав стандартной ЭЦВМ.

Преобразователь работает сле дукяцим образом.

Из ЭЦВМ предварительно выдаются сигналы, устанавливающие в нулевое 5 состояние .регистр адреса оперативно-.

го запоминающего устройства 9, сумматор 10, управляющий триггер 2 и счетчик 3 по шине 8 обнуления.

Число (а() из ячейки оперативной памяти ЭЦВМ программным путем заносится в дополнительном коде по шинам 12 в сумматор 10 и осуществляется процесс сложения этого числа с некоторым другим постоянным числом (Ь) поступившим по шинам 13, в циклическом режиме до получения нуля в сумматоре 10. Адрес ячейки оперативной памяти (С).) выбирается однозначно. Для преобразователя он служит управляющим кодом при выборке его по шинам 11 через сумматор 10 в регистр адреса оперативного запоминающего устройства.

В ходе выполнения команд происходит либо одновременное появление адреса выбранной ячейки в регистре адреса оперативного запоминающего устройства 9 и сумматоре -10, либо произвольная комбинация содержимых этих регистров.

Дешифратор 1 представляет собой диодную сборку, выполненную по схеме совпадения И по низкому уровню с инверкзным выходом. Входы дешифратора 1 связаны с соответствующими выходами триггеров регистра адреса ОЗУ 9 и с выходом сумматора 10, на котором формируется сигнал Сд, в виде низкого уровня. При появлении в регистре адреса ОЗУ 9 управлящего кода (ф} на выходах триггеров тоже появляется низкий уровень. Таким образом, при наличии нуля в сумматоре 10 и управляющего кода в ре гистре адреса ОЗУ дешифратор срабатывает.

В исходном СОСТОЯНИИ;когда не выполняется условие одновременного появления управляющего кода в регисре адреса оперативного запоминающего устройства 9 и нуля в сумматоре 10, хотя бы на одном входе дешифратора 1 имеем высокий уровень, а на его выходе - низкий уровень. Т&ким образом, в .процессе сложения на выходе дешифратора 1 появляется серия импульсов, которые подаются на единичный вход управляющего триггера 2 и счетный вход счетчика 3. Первый импульс устанавливает в единицу первый триггер счетчика 3 и управляющий триггер 2. Перепад с низкого на высокий уровень на единичном выходе управляющего триггера 2 запускает второй формирователь б, на вь1ходе которого появляется импульс, сигнализирующий о начал преобразования числа в межимпульсный, интервал.

Перепад с высокого на низкий уровень с нулевого выхода управляющего триггера 2 не устанавливает счетчик 3 в нуль, поскольку триггеры счетчика 3 перебрасываются из одного состояния в другое положительным импульсом.

Последующие импульсы с выхода дешифратора 1, подтверждая единичное состояние управляющего триггера 2, пересчитываются счетчиком 3. Выходы триггеров счетчика 3, подключены к входам второго дешифратора 4,

10 выбраны таким образом, что после пересчета последнего импульса из серии, появляющейся на выходе дешифратора 1, на входах дешифратора 4 имеем низкий уровень, а на его

5 выходе - высокий. Дешифратор 4 представляет собой дио.дную сборку выполненную по схеме совпадения И по низкому уровню с инверсным выходом. Поскольку в исходном состоя0нии счетчик 3 находится в нуле и на входах дешифратора 4 имеем высокий уровень, то на его выходе появляется, низкий уровень. При пересчете последнего импульса на вы5ходе дешифратора 4 имеем перепад с низкого на высокий уровень, который запускает первый формирователь 5, а последний, в свою очередь, устанавливает в нуль управляющий триггер 2. Перепад с низкого на вы0сокий уровень нулевого выхода управляющего триггера 2 устанавливает в нуль счетчик 3, а перепад с высокого на низкий уровень на единичном выходе триггера 2 не запускает второй

5 формирователь 6. Следующий запуск формирователя б, свидетельствующий об окончании преобразования первого числа в межимпульсный интервал и начале преобразования следующе0го числа, происходит после выборки этого числа в дополнительном ходе в сумматор-МО.

Масштаб интервала между импульсами на выходе преобразователя может измerfятьcя произвольно за счет вы5бора величины числа, что обеспечивает широкие функциональные возможности предлагаемого преобразователя.

Изобретение позволяет сравнитель0но просто в техническом отношении и экономически эффективно осуществлять преобразование программно-формируемой управляющей числовой последовательности ЭЦВМ в соответствующую

5 импульсную управляющую последовательность, которая можетбыть использована для управления каким-либо технологическим процессом, промьлшленной установкой, экспериментальными

0 научными установками и аналоговой частью гибридного вычислительного комплекса.

vr

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Устройство для автоматического измерения времени распространения ультразвука | 1988 |

|

SU1523924A1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов при исследовании сердечно-сосудистой системы | 1982 |

|

SU1157547A1 |

| Устройство для анализа формы огибающей частотного сигнала | 1987 |

|

SU1524013A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

| Формирователь сложной функции | 1985 |

|

SU1287135A1 |

| Формирователь сложной функции | 1982 |

|

SU1075400A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

ПРЕОБРАЗОВАТЕЛЬ ЧИСЕЛ В ДЛИТЕЛЬНОСТЬ МЕЖИМПУЛЬСНЫХ ИНТЕРВАЛОВ, содержащий счетчик импульсов, первый дешифратор, выход которого подключен к единичному входу управляюЫего триггера, единичный выход которого соединен с входом первого формирователя импульсов, выход которого подключен к выходной шине, о т л и ч а ю щ и и с я тем, что, с целью расширения функциональных возможностей, в него введены регистр адреса оперативного запоминающего устройства, сумматор, второй дешифратор и второй формирователь импульсов, при этом входы сумматора соединены с соответствующими входными шинами, а выходы соответственно подключены к первому входу первого дешифратора и первому входу регистра адреса оперативного запоминакяцего устройства, выход которого подключен к второму входу первого дешифратора, выход которо- го соединен со счетным входом счетчика импульсов, вход установки ;нуля которого соединен с нулевым выходом управляющего триггера, а выход - с входом второго дешифратора, выход которого через второй формирователь импульсов,подключен к нулевому входу управляющего триг.Гера, шине сброса и входам установки нуля счетчика импульсов, сумматора и регист15а адреса оперативного запоминающего устройства.

T e

JL

JL

.at

13

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И | |||

| Преобразователи информации для электронных цифро.вых вычислительных устройств | |||

| М., | |||

| Энергия, 1970, с | |||

| Крутильный аппарат | 1922 |

|

SU234A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР | |||

| Преобразователь кода во временнойиНТЕРВАл | 1978 |

|

SU809557A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| .; | |||

Авторы

Даты

1983-08-07—Публикация

1982-03-23—Подача