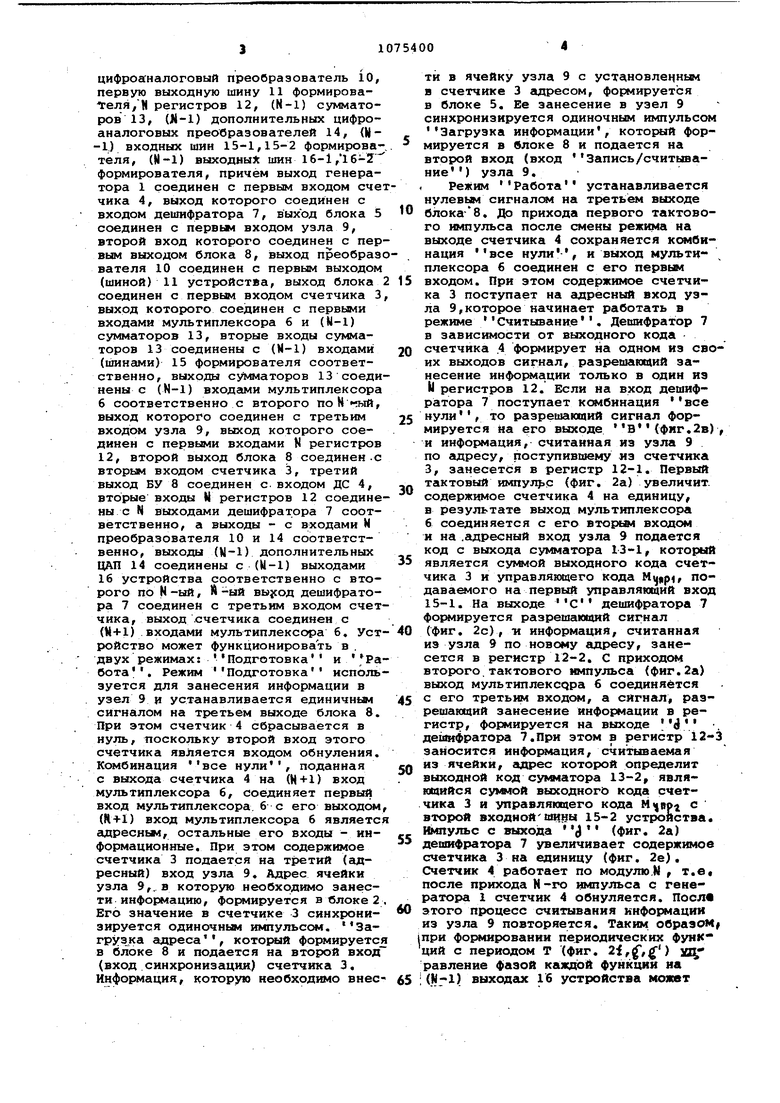

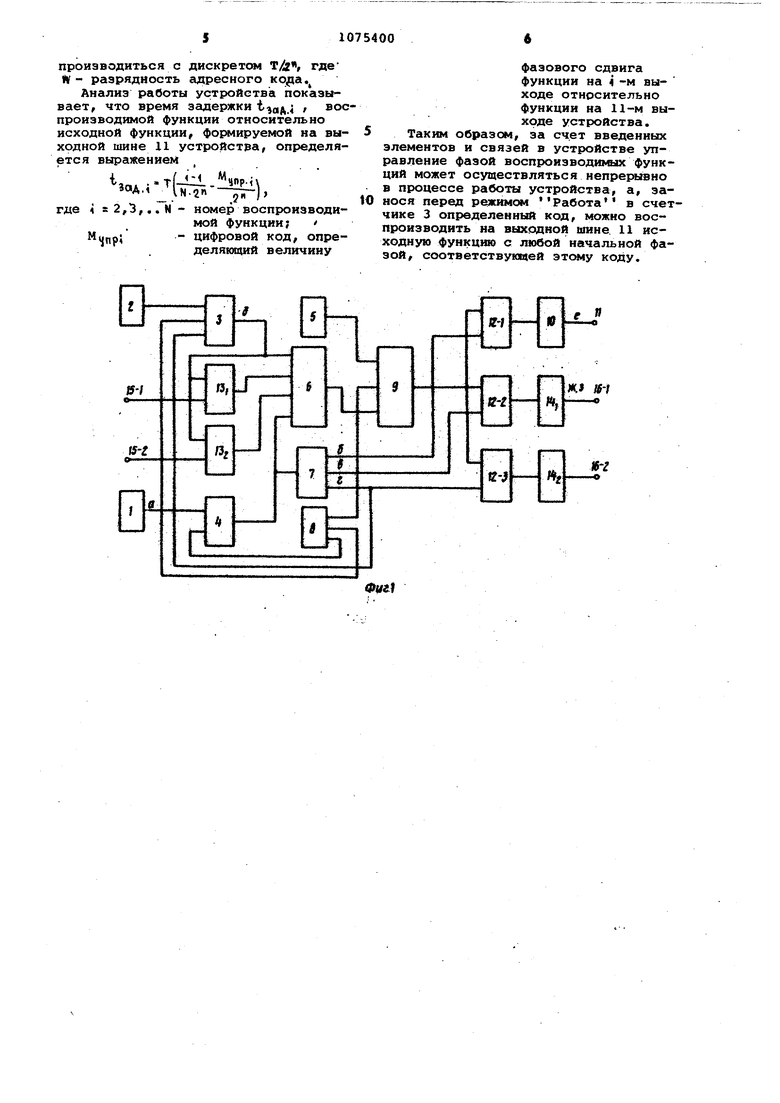

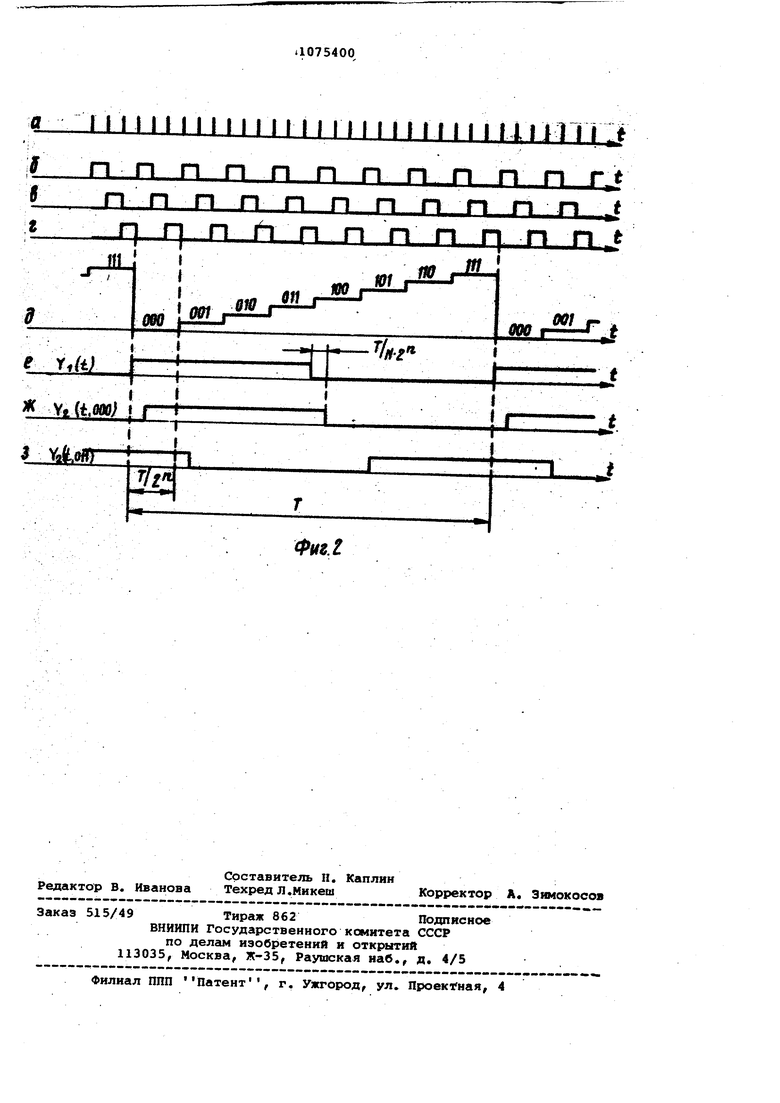

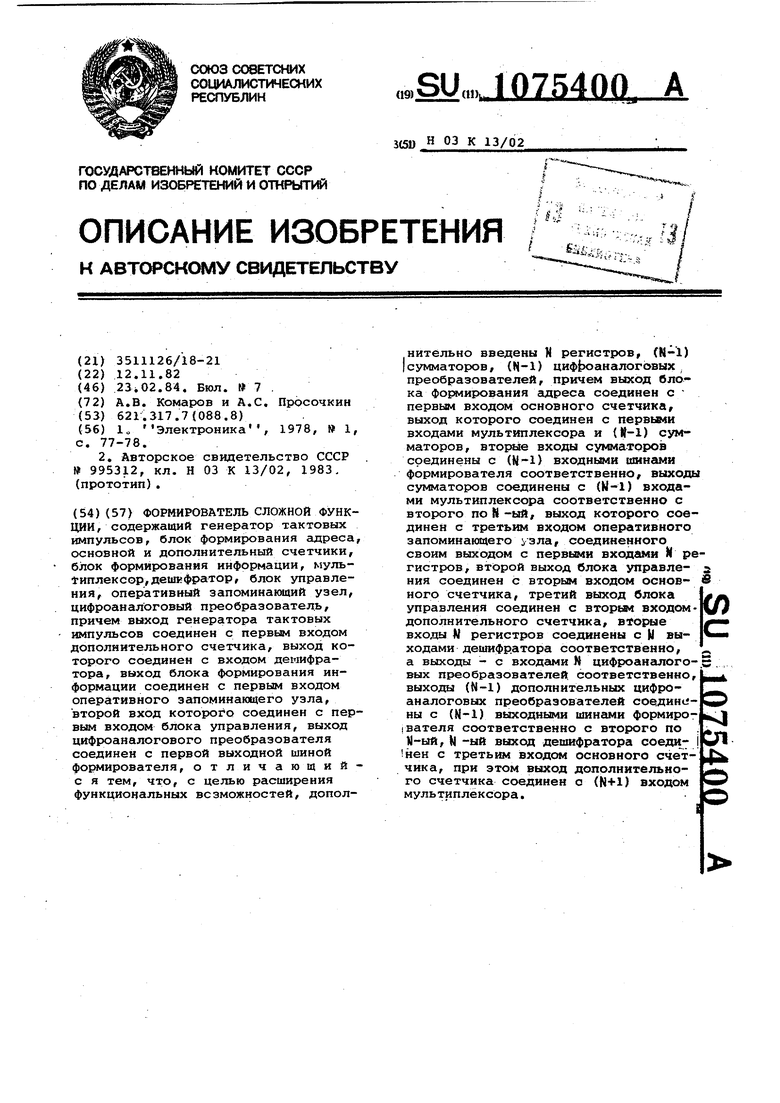

Изовретение относится к аналогоцифровой вычислительной технике и может быть использовано в аналогоцифровьвс вычислительных комплексах, устройствах автоматики и измерительной техники. . Известен формирователь сложных функций, содержащий генератор тактовых импульсов, триггер, элемент И, елок формирования адреса, цифроаналоговые преобразователи, блок управления, блок формирования информации, оперативное запоминакицее устройство l . Недостатком формирователя сложных функций является невозможность реали зации режима преобразования код фаза. Наиболее близким к изобретению является формирователь сложной функции, содержащий генератор тактовых импульсов, блок формирования адреса, основной и дополнительный счетчики, блок формирования информации, мульти плексор (к нему отнесены первый блок элементов И, второй блок элемзнтов И, блок Элементов ИЛИ), дешифратор, блок управления (к нему отнесен блок управления, триггер, элемент И-НЕ), оперативный запоминающий узел цйфроаналоговый преобразователь, блок установки начального адреса, элемент ИЛИ, Генератор импульсов подключен через блок задержки и элемент И к первому входу основного счетчика, выход которого соединен с первым входом запоминаюсоего узла, выход которого подключен через преобразователь к выходу устройства, блок установки начального адреса через дополнительный счетчик и дешифратор - к дискриминатору и через блоки элементов ИЛИ - к второму входу, а блок формиров ния сщреса через второй блок элементов ИЛИ соединен с вторым входом основного счетчика {2 , Недостатком известного устройства является ограниченные функциональные возможности, заключающиеся в том что воспроизводимая функция сдчигает ся относительно импульса дискриминатора, а не относительно себя самой. Целью изобретения является расширеаие функциональных возможностей. Поставленная цель достигается тем что в формирователь сложной функции, содержгиций генератор тактовых импуль сов, блок формирования адреса, основ ной и дополнительный счетчики, блок формирования информации, мультиплексор, дешифратор, блок управления, оперативный запсж инающий узел, цйфроаналоговый преобразователь, причем выход генератора тактовых импульсов соединен с первым входом дополннтельного счетчика, выход которого соединен с входом дешифратора, выход блока формирования информации соеди-. нен с первым входом оперативного запоминающего узла, второй вход которого соединен с первым входом блока управления, выход циф15оаналогового преобразователя соединен с первой . выходной шиной формирователя, введены и регистров, (N-1) сумматоров, (N-1) цифроаналоговых преобразователей, причем выход блока формирования адреса соединен с первым входом основного счетчика, выход которого соединен с первыми входами мультиплексора и (N-1) сумматоров, вторые входы сумматоров соединены с (N-1) входными шинами устройства соответственно, выходы сумматоров соединены с (И-) входами мультиплексора соответственно с второго по М-ый, выход которого гоединен с третьим входом оперативного запоминающего узла, выход которого соединен с пер-: ,выми входами Н регистров, второй выход блока управления соединен с вторым входом основного счетчика., третий выход блока управления соединен с вторьм входом дополнительного счетчика, вторые входы N регистров соединены с N выходами дешифратора соответственно, а выходы - с входами N гу фроаналоговых преобразователей соответственно, выходы (N-1) дополнительных цифроаналоговых преобразователей соединены с .(N-1) выходными шинами устройства соответственно с второго по N-ый, N -ый дешифратора соединен с третьт1м входЬм основного счетчика, выход дополнительного счетчика соединен с (N+1) входом мультиплексора. i -На фиг, 1 показана функциональная схема предлагаемого устройства при N3 (строчными латинскими буквами на. ней обозначены проводники и шины, сигналы в которых используются в дальнейших фигурах) на фиг. 2 - эпюры напряжений, поясняющие принцип действия предлагаемого устройства, в режиме Работа при формировании прямоугольных функций УН а) - на первом и У (t М ripi ) - на втором выходах устройства (при It 3) , где i - текущее время, цифровой код, подаваемый на первый вход устройства и определякяций величину сдвига по фазе функции У (i) относительно функции У4(1), для двух значений Mijnp, 4-000 и Мцир, 011. Латинскими строчными буквами обозначены сигналы, которые действуют в соответствующих проводниках. Формирователь содержит генератор 1 тактовых импульсов, блок 2 формирования адреса, основной и дополнительный счетчики 3 и 4, блок 5 формирования информации, мультиплексор 6, дешифратор 7, блок 8 управления, оперативный замопинающий узел 9,

цифроаналоговый преобразователь 10, первую выходную шину 11 формирователя/Ц регистров 12, (N-1) сумматоров 13, (Л-1) дополнительных цифроаналоговых преобразователей 14, Ш-1) входньк шии 15-1,15-2 формирователя, (N-1) выходны шин 16-1,16-2 формирователя, причём выход генератора 1 соединен с первым входом счетчика 4, выход которого соединен с входом дешифратора 7, выход блока 5 соединен с первым входом узла 9, второй вход которого соединен с первым выходом блока 8, выход преобразователя 10 соединен с первым выходом (шиной) 11 устройства, выход блока 2 соединен с первым входом счетчика 3, выход которого соединен с первыми входами мультиплексора 6 и (N-1) сумматоров 13, вторые входы сумматоров 13 соединены с (М-1) входами (шинс№1и) 15 формирователя соответственно, выходы сумматоров 13 соединены с (N-1) входами мультиплексора 6 соответственно с второго поНгый, выход которого соединен с третьим входом узла 9, выход которого соединен с первыми входами N регистров 12, второй выход блока 8 соединен-с вторым входом счетчика 3, третий выход БУ 8 соединен с. входом ДС 4, вторые входы N регистров 12 соединены с N выходами дешифратора 7 соответственно, а выходы - с входами N преобразователя 10 и 14 соответственно, выходы (N-1) дополнительных ЦАП 14 соединены с (M-l) выходами 16 устройства соответственно с второго по S-ый вы{сод дешифратора 7 соединен с третьим входом счетчика, выход .счетчика соединен с (ti+1) входами мультиплексора 6, Устройство может функционировать в .

и РаПодготовка

двух режимах:

бота Подготовка

Режим испольэуется для занесения информации в узел 9 и устанавливается единичн Л1 сигналом на третьем выходе блока 8. При этом счетчик4 сбрасывается в нуль, поскольку второй вход этого счетчика является входом обнуления. К ялбинация все нули, поданная с выхода счетчика 4 на (N+1) вход мультиплексора 6, соединяет первый вход мультиплексора. 6с его выходом, (Н+1) вход мультиплексора 6 является адресном, остальные его входы - информационные. При этом содержимое счетчика 3 подается на третий (адресный) вход узла 9. Адрес ячейки узла 9,. в которую необходимо занести инфоЕжацию, формируется в блоке 2, Его значение в счетчике 3 синхронизируется одиночным импульсом. Загруз ка адреса, который формируется в блоке 8 и подается на второй вход (вход синхронизации) счетчика 3. Информация, которую необходимо внестй в ячейку узла 9 с установленным в счетчике 3 гшресом, формируется в блоке 5. Бе занесение в узел 9 синхронизируется одиночным импульсом Загрузка информации, который фор мируется в блоке 8 и подается на второй вход (вход Запись/считывание ) узла 9,

1 Режим Работа устанавливается нулевым сигналом на третьем выходе

О блока-8, До прихода первого тактового импульса после смены реж1та на выходе счетчика 4 сохраняется комбинация все нули-, и выход мульти плексора 6 соединен с его первым

5 входом. При этом содержимое счетчика 3 поступает на адресный вход узла 9,которое начинает работать в режиме Считывание . Дешифратор 7 в зависимости от выходного кода

0 счетчика .4 фо| 1ирует на одном из своих выходов сигнал, разрешающий занесение информации только в один иэ U регистров 12. Бели на вход дешифратора 7 поступает комбинация все

5 нули, то разрешающий сигнал формируется на его выходе (фиг.2в) и информация, считанная из узла 9 по ащресу, поступившему из счетчика 3, занесется в регистр 12-1. Первый тактовый импул|1С (фиг. 2а) увеличит,

0 содержимое счетчика 4 на единицу, в результате выход мультиплексора 6 соединяется с его вторым входом и на .адресный вход узла 9 подается код с выхода сумматора 13-1, который

5 является выходного кода счетчика 3 и управлякяцего кода Mijup, подаваемого на первый управляющий вход 15-1. На выходе С дешифратора 7 формируется разрешающий сигнал

0 (фиг. 2с), и информация, считанная из узла 9 по новому адресу, занесется в регистр 12-2. С приходом второго тактового импульса (фнг.2а) выход мультиплексс}ра б соединяется

5 с его третьим входом, а сигнал, разрешающий занесение информации в регистр, формируется на выходе де1йиФратора 7.При этом в регистр 12-3 заносится информация, считываемая

м из ячейки, адрес которой определит выходной код суьматора 13-2 являющийся суммой выходного кода счетчика 3 и управляющего кода с второй входнойшины 15-2 устройства. Иппульс с выхода J (фиг, 2а)

дешифратора 7 увеличивает содержимое счетчика 3 на единицу (фиг. 2е). Счетчик 4 работает по модулю .К т.е. после прихода N-го импульса с генератора 1 счетчик 4 обнуляется. После

0 этого процесс считывания информации из узла 9 повторяется. Таким образом 1при формировании периодических фунК ций с периодом Т (фиг. 2i,,jg) щ равление фазой каждой функции на

5 ; (Nr) выходах 16 устройства может

производиться с дискретом T/i, где № - разрядность адресного .

Анализ работы устройства показывает, что время задержки ,, , воспроизводимой функции относительно исходной функции, формируемой на выходной шине 11 устройства, определяется выражением

-iii.Wynp.iv

W..2 ,5

vN.n -;;),

где i s2,3,..N - номер воспрюизводимой функции;

цифровой код, определякхций величину

i

e-i

фазового сдвига функции на i-м выходе относительно функции на 11-м выходе устройства.

Таким образом, за счет введенных элементов и связей в устройстве управление фазой воспроизводи шх функций может осуществляться непрерывно в процессе работы устройства, а, занося перед режимом Работа в счетчике 3 определенный код, можно воспроизводить на выходной шине. 11 исходную функцию с любой начальной фазой, соответствующей этому коду.

Tkj

Kt

ж tf-jf

Sl

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Формирователь сложной функции | 1985 |

|

SU1287135A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182546A1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Формирователь сложной функции | 1989 |

|

SU1624694A1 |

ФОРМИРОВАТЕЛЬ СЛОЖНОЙ ФУНКЩ И, содержащий генератор тактовых импульсов, блок формирования адреса, основной и дополнительный счетчики, блок формирования информации, мультиплексор, дешифратор, блок управления, оперативный запоминакиций узел, цифроаналоговый преобразователь, причем выход генератора тактовых импульсов соединен с первым входом дополнительного счетчика, выход которого соединен с входом дешифратора, выход блока формирования информации соединен с первым входом оперативного запоминающего узла, второй вход которого соединен с первым входом блока управления, выход цифроаналогового преобразователя соединен с первой выходной шиной формирователя, отличающийс я тем, что, с целью расширения функциональных возможностей, дополнительно введены Ц регистров, CS-1) сумматоров, (N-1) цифix aнaлoгoвыx , преобразователей, причем выход блока формирования адреса соединен с первым входом основного счетчика, выход которого соединен с пврвьв4и входами мультиплексора и (W-1) сумматоров, вторые входы сумматоров соединены с () входными шинами формирователя соответственно, выходы сумматоров соединены с (М-1) входами мультиплексора соответственно с второго по М-ый, выход которого соединен с третьим входом оперативного запоминаквдего узла, соединенного своим выходом с первыми входгмя N регистров, второй выход блока управле: I (Л ния соединен с вторым входом основ ного счетчика, третий выход блока управлелия соединен с BTOptiM входсш дополнительного счетчика, вторые входы W регистров соединены с U выходами дешифратора соответственио, а выходы - с входами N цифроаиалого-5 вых преобразователей, соответственно, выхода (N-1) дополнительных цифроаналоговых преобразователей соединенны с (N-1) выходными шинами формиро j гвателя соответственно с второго по . on 1-ый, Н -ый выход дешифратора соеди- j нен с третыш входом основного счет4 чика, при этом выход дополнительноО О го счетчика соединен о (N+1) входе мультиплексора.

f3f

is-f

-г

%

«9 fl I M MM I И И 1 П П n П П n

Фиг. I III i 111 M I M I M liillTi If П n n n n r t

Авторы

Даты

1984-02-23—Публикация

1982-11-12—Подача