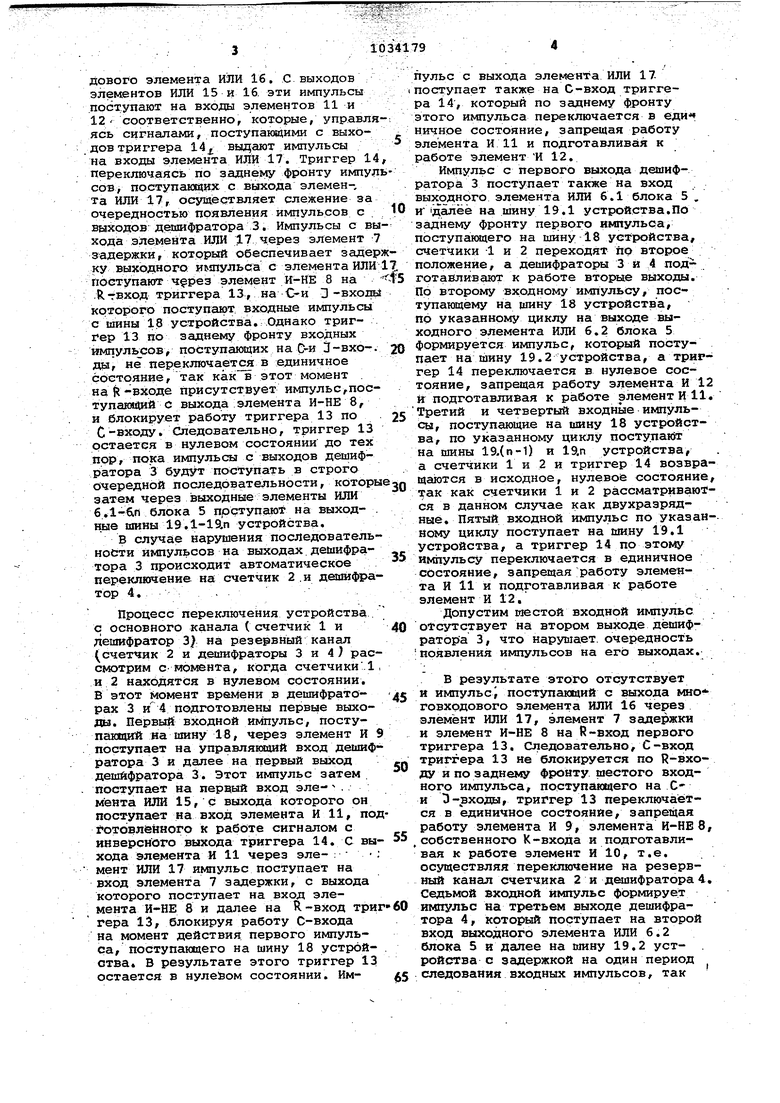

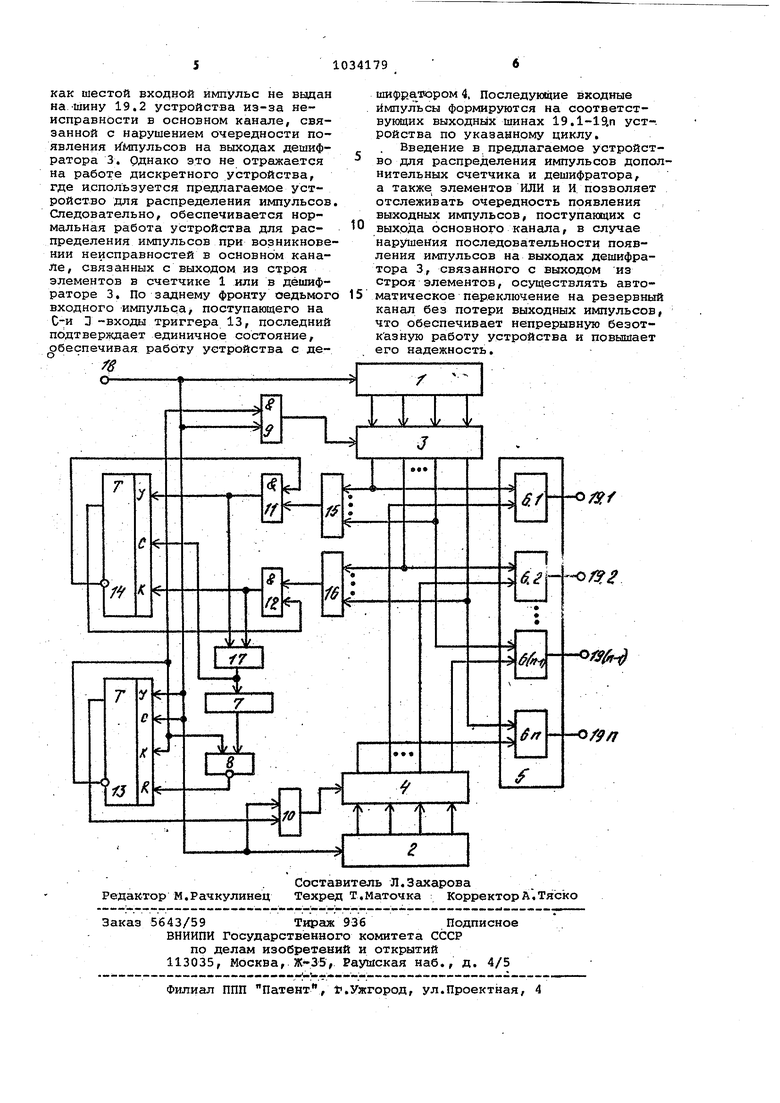

Изобретение относится к вйчисли тельной технике и телемеханике и мо жет быть применено при построении распределителей тактовых импульсов лля дискретных устройств и вычислительных машин. Известен многоканальный распреде тель импульсов,- содержащий в каждом канале триггер и два элемента И СИ Недостатком данного распределите ля является низкая надежность, так как он не обеспечивает его нормальной работы при выходе из строя отдельных элементов. Наиболее близким к- предлагаемому является устройство для распределения импульсов, содержащее первый и второй счетчики, соединенные с дешифраторами, триггер, элементы И, И-НЕ и ИЛИ, блок выходных элементов ИЛИ и элемент задержки С 2. Недостатком издестного устройств является то, что оно не отслеживает очередность появления выходных импульсов, поступакадих с выходов дашифратора, что может привести к выдаче ложной информации на выходе Устройства, от обусловленной выходом из строя элементов в счетчике или дешифраторе, что снижает надежность его работы, Цель изобретения - повышение надежности работы устройства. Указанная цель достигается тем, что в устройство для распределения импульсов, содержащее первый и второй счетчики, выходы которых соединены с входами соответственно перво го и второго дешифратора, блок выходных п элементов ИЛИ, первые вход которых соединены с соответствующим выходами первого дешифратора, вторы входы выходных (п-1) элементов ИЛИ соединены с (2-п) выходами второго дешифратора соответственно, апервы вход второго дешифратора подключен к второму входу выходного п элемента или, выходы всех элементов ИЛИ блока соединены с соответствующими выходными шинами, элемент задержки, выход которого соединен с первым входом элемента И-НЕ, второй вход. которого подключен к X-входу и инверсному выходу первого триггера и первому входу первого элемента И, второй вход которого соединен с вхо ной шиной, с входами первого и второго счетчиков, первым входом второ го элемента И и с Э - и С-входами первого триггера, R-вход которого подключен.к выходу элемента И-НБ, а прямой выход - к второму входу вт рого элемента И, выходы первого и второго элементов И соединены с управляющими входами соответствующих дешифраторов, и первый элемент ИЛИ, введены триггер, второй и третий элементы ИЛИ, третий и четвертый элементы И, причем нечетные и четные выходы первого дешифратора соединены с входами соответственно первого и второго элементов ИЛИ, выходы которых соединены с первыми входа «1 соответственно третьего и четвертого элементов И, вторые входы который подключены соответственно к инверсному и прямому выходам второго триггера, а выходы - соответственно к.Э- и К-входам второго триггера и входам третьего элемента ИЛИ i выход которого соединен с входом элемента задержки и С-входом второго триггера. На чертеже представлена функциональная схема предлагаемого устройства. Устройство для распределения импульсов содержит счетчики 1 и 2, дешифраторы 3 и 4, блок 5 выходных элементов.ИЛИ б.1-6п, элемент 7 задержки, элемент И-НЕ 8, элементы И 9-12, триггеры 13 и 14, элементы ИЛИ 15-17, выходную шину 18 и выходные шины 19.1-19п. Устройство работает следующим образом. Перед началом работы устройство приводится в исходное состояние, в результате чего счетчики 1 и 2 .и триггеры 13 и 14 находятся в исходном, нулевом состоян.ии. После этого устройство готово к работе. Затем на входную шину 18 поступают импульсы, частота следован .1 которых устанавливается исходя яз требуемого быстродействия дискретного устройства или вычислительной машины, для которых на шинах 19.1-19п формируется тактовая сетка, обеспечивающая управление данным дискретным устрой- . ством или вычислительной машиной. Эти сигнсшы поступают на входы счетчиков 1 и 2, которые переключаются по заднему фронту входных импульсов, Счетчики 1 и 2 начинают заполняться и подготавливать к работе выходы дешифраторов 3 и 4, Однако импульсы появляются на выходах только дешифратора 3, так как триггер 13 находится в исходном, нулевом состоянии, и сигнал, поступающий с нулевого выхода триггера 13, подготавливает к работе элемент И-НЕ 8.и элемент И 9, через который на управляющий вход дешифратора 3 поступают импульсы с шины 18 устройства . Эти импульсы, проходя через дешифратор 3, формируются на его выходах и затем поступают на первые входы выходных элементов ИЛИ б.1-бп блока 5. . Импульсы с нечегных выходов дешифратора 3 поступгиот также на входы многовходового элемента ИЛИ 15, а с четных выходов -, на входы многовходового элемента ИЛИ 16. С.выходов элементов ИЛИ 15 и 16. эти импульсы поступают на входы элементов 11 и 12 соответственно, которые, управл ясь сигналами, поступаквдими с выходов триггера 14 выдают импульсы на входы элемента ИЛИ 17. Триггер 1 переключа:ясь по заднему фронту импу сов, поступающих с выхода элемента ИЛИ 17, осуществляет слежение за очередностью появления импульсов с выходов: дешифратора 3. Импульсы с в хода элемента ИЛИ 17 через элемент з адержки, который обеспечивает заде ку выходного импульса с элемента ИЛИ поступают 4fрез элемент И-НЕ 8 на .R-вход триггера 13, на С-и 3-ВХОХЕ KQTOpioro поступают входные импульсы с шины 1.8 устройства. Однако триггер 13 по заднему фронту входных импульсов, поступающих на С-и 3-входы не переключается в единичное состояние, так какв этот момент . на f -входе присутствует импульс,пос тупаюйшй с выхода ; элемента И-НЕ 8, и блокирует работу триггера 13 по С эходу. Следовательно, триггер 13 остается в нулевом состоянии до тех пор, пока импульсы с выходов дешифратора 3 будут поступать в строго очередной последовательности, котор затем через :выходные элементы ИЛИ б,1-€ьп блока 5 поступают на выходные шины 19,l-iain устройства. В случае нарушения последователь ности импульсов на выходах дешифратора 3 происходит автоматическое переключение на счетчик 2.и дешифра тор 4, , . Процесс переключения устройства . с основного канала (счетчик 1 и дешифратор 3) на резервный канал (счетчик 2 и дешифраторы 3 и 4} рас смотрим с момента, когда счетчики1 и 2 находятся в нулевом состоянии. В этот момент времени в дешифратоpax 3 подготовлены первые выходы. Первый входной илгаульс, поступающий иа шину 18, через элемент И поступает на управлякяяий вход дешиф ратора 3 и далее на первый выход дешифратора 3. Этот импульс затем поступает на первый вход эле- . мента ИЛИ 15, с выхода которого он поступает на вход элемента И 11, по готовленного к работе сигналом с инверсного выхода триггера 14. С вы хода элемента И 11 через эле- : мент ИЛИ 17 импульс поступает на вход элемента 7 задержки, с выхода которого поступает на вход элемента И-НЕ 8 и далее на R-вход три гера 13, блокируя работу С-входа на момент действия первого импульса, поступающего на шину 18 устройства. В результате этого триггер 13 остается в нулевом состоянии. Им4пульс с выхода элемента ИЛИ 17 поступает также на С-вход триггера 14, который по заднему фронту этого импульса переключается в еди ничное состояние, запрещая работу элемента И 11 и подготавливая к работе элемент И 12. Импульс с первого выхода дешифратора 3 поступает также на вход выходного элемента ИЛИ 6.1 блока 5 , И далёё на шину 19.1 устройства.По заднему фронту первого импульса, поступакадего на шину 18 устройства, счетчики 1 и 2 переходят по второе положение, а дешифраторы 3 и 4 подготавливают к работе вторые выходы. По второглу входному инотульсу, поступающему на шину 18 устройства, по указанному циклу на выходе выходного элемента ИЛИ 6.2 блока 5 формируется импульс, который поступает на шину 19.2 устройства, а триггер 14 переключается в нулевое состояние, запрещая работу эдеме нта И 12 и подготавливая к работе элемент И 11. Третий и четвертый входные импульсы, поступающие на шину 18 устройства, по указанному циклу поступают на шины 19.(п-1) и 19,п устройства, а счетчики 1 и 2 и триггер 14 возвращакзтся в исходное, нулево а состояние, так как счетчики 1 и 2 рассматриваются в данном случае как двухразрядные. Пятый входной импульс по указанному циклу поступает на шину 19.1 устройства, а триггер 14 по этому импульсу переключается в единичное состояние, запршцая работу элемента И 11 и подготавливая к работе элемент И 12. Допустим шестой входной импульс отсутствует на втором выходе дёшифратора 3, что нарушает, очередность появления импульсов на егО выходах. В результате этого отсутствует и импульсi поступающий с выхода мно говходового элемента ИЛИ 16 через элемент ИЛИ 17, элемент 7 задержки и элемент И-НЕ 8 на R-вход первого триггера 13. Следовательно, С-вход триггера 13 не блокируется по R-BXOду и по заднему фронту шестого входного импульса, поступающего на Си -входы, триггер 13 переключается в единичное состояние, запрещая работу элемента И 9, элемента И-НВ8, собственного К-входа и подготавливая к работе элемент И 10, т.е. осуществляя переключение на резервный канал счетчика 2 и дешифратора 4. Седьмой входной импульс формирует импульс на третьем выходе дешифратора 4, который портупает на второй вход выходного элемента ИЛИ 6.2 блока 5 а далее на шину 19.2 уст- . ройства с задержкой на один период следования входных импульсов, так

как шестой входной импульс не вьщан на -шину 19.2 устройства из-за неисправности в основном канале, связанной с нарушением очередности появления Импульсов на выходах дешифратора 3. Однако это не отражается на работе дискретного устройства, где используется предлагаемое устройство для распределения импульсов Следовательно, обеспечивается нормальная работа устройства для распределения импульсов при возникновении неисправностей в основном канале, связанных с выходом из строя элементов в счетчике 1 или в дешифраторе 3. По заднему фронту седьмог входного импульра, поступающего на С-и 3 -входы триггера 13, последний подтверждает единичное состояние, Обеспечивая работу устройства с дешифр.а тюром 4, Последующие входные импульсы формируются на соответствующих выходных шинах 19.1-19.П уст-, ройства по указайному циклу.

Введение в предлагаемое устройство для распределения импульсов дополнительных счетчика и дешифратора, а также элементов ИЛИ и И. позволяет отслеживать очередность появления выходных импульсов, поступающих с выхода основного канала, в случае нарушения последовательности появления импульсов на выходах дешифратора 3, связанного с выходом из строя элементов, осуществлять автоматическое переключение на резервный канал без потери выходных импульсов, что обеспечивает непрерывную безотказную работу устройства и повышает его надежность.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения импульсов | 1984 |

|

SU1205135A1 |

| Устройство для распределения импульсов | 1980 |

|

SU903846A1 |

| Пересчетное устройство | 1981 |

|

SU974593A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1015443A1 |

| Устройство для переключения каналов | 1982 |

|

SU1019634A1 |

| Распределитель импульсов | 1981 |

|

SU976436A1 |

| Устройство формирования серий импульсов | 1981 |

|

SU962890A1 |

| Счетное устройство | 1985 |

|

SU1256195A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Счетное устройство с переменнымКОэффициЕНТОМ пЕРЕСчЕТА | 1979 |

|

SU801255A1 |

УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ИМПУЛЬСОВ, содержащее первый и второй счетчики, выходы которых соединены с входами соответственно первого и второго дешифраторов,блок выходных п элементов ИЛИ,;первые входы которых соединены с соответствукяцими выходами первого дешифратора, вторые входы выходных (п-1) эле ментов ИЛИ соединены с

-ОХ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| МНОГОКАНАЛЬНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 0 |

|

SU387354A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке 2916543/18, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-08-07—Публикация

1982-03-15—Подача