Изобретение относится к вычислительной технике и электронике и может быть использовано при построени многоканальных вычислительных систем, в ч.айтности для поканального разделения системы, например, в режиме проверки работоспособности каждого канала мажоритарно-резервированной системы.

Известен мажоритарный элемент на комплементарных МДП-транзисторах, содержащий ключевую часть, состоящую из первой ветви, образованной Двумя последовательно включенными транзисторами, и второй, включенной параллельно первой и образованной двумя последовательно включен.ными транзисторами, параллельно одному из которых подключен третий транзистор, а также, нагрузочную .Часть, симметричную ключевой 1.

Недостаток устройства состоит в том, что его нельзя использовать при построении многоканальных систем, работающих в режимах поканального разделения.

Известен также управляемый мажоритарный элемент на комплементарных ВДП-транзисторах, содержащий первую ветвь,( включенную между шиной питания и выходной шиной и состоящую из последовательно включенных первого и второго транзисторов, при этом параллельно первому транзистору подключен третий транзистор, вторую ветвь, включенную между выходной шиной и общей и состоящую из последовательно включенных четвертого и пятого транзистора, параллельно которому подключен шестой транзистор. Третью ветвь , состоящую из последовательно включенных транзисторов седьмого, восьмого и девятого параллельно которому подключен десятый транзистор, и четвертую ветвь состоящую из последовательно вкл1оченых одиннадцатого, двенадцатого , тринадцатого транзисторов и четырнадцатохо транзистора, подключенного параллельно тринадцатому, причем затворы второго, четвертого, десятого и четырнадцатого, транзисторов подключены к первой информационной шине, затворы первого, пятого, десятого и тринадцатого транзисторов - к второй информационной шине, затворы восьмого и двенадцатого к третьей информационной шине, затворы третьего и одиннадцатого к прямому управляющему входу, затво,ры,шестого и седьмого - к инверсному управляющему входу, стоки девятого, десятого, тринадцатого и четырнадцатого транзисторов - к выходной шине, а истоки седьмого и одиннадцатого - соответственно к шине питания и общей шине .

Недостатком элемента является низкое быстродействие, обусловленное большой паразитной емкостью выходной шины, образуемой стоками шести МДП-транзисторов. Цель изобретения - повышение

быстродействия управляемого мажоритарного элемента..

Для достижения поставленной цели в управляемом мажоритарном элементе

0 на комплементарных МДП-транзисторах, содержащем - первую ветвь, включенную между шиной питания и выходной шиной и состоящую из последовательно включенных первого р второго

5 транзисторов, при этом параллельно первому транзистору подключен третий транзистор, вторую :ветвь, вклю-. ченную выходной шиной и общей и состоящую из последовательно ченных четвертого и пятого транзистора, при этом параллельно пятому транзистору подключен шестой транзистор, третью ветвь, состоящую из последовательно включенных транзисторов седьмого, восьмого и девятого, параллельно оторому подключен десятый транзистор, и четвертую ветвь, состоящую из последовательно включенных одиннадцатого, двенадцаj того, тринадцатого транзисторов и четырнадцатоготранзистора, подключенного параллельно тринадцатому, причем затворы второго, четвертого, десятого и четырнадцатого транзисторов подключен1а к первой информационной шине, загворы первого, пятого, девятого, тринадцатого транзисторов - к второй информационной шине, затворы восьмого и две надцатого - к третьей информационной шине, затворы третвего и одиннадцатого - к прямому управляющему входу, а затворы шестого и седьмого к инверсному управляющему входу, истоки девятого и десятого транзисторов подключены к шине питания, тринадцатого и четырнадцатого - к общей шине, а стоки седьмого и одинт надцатого - к выходной шине.

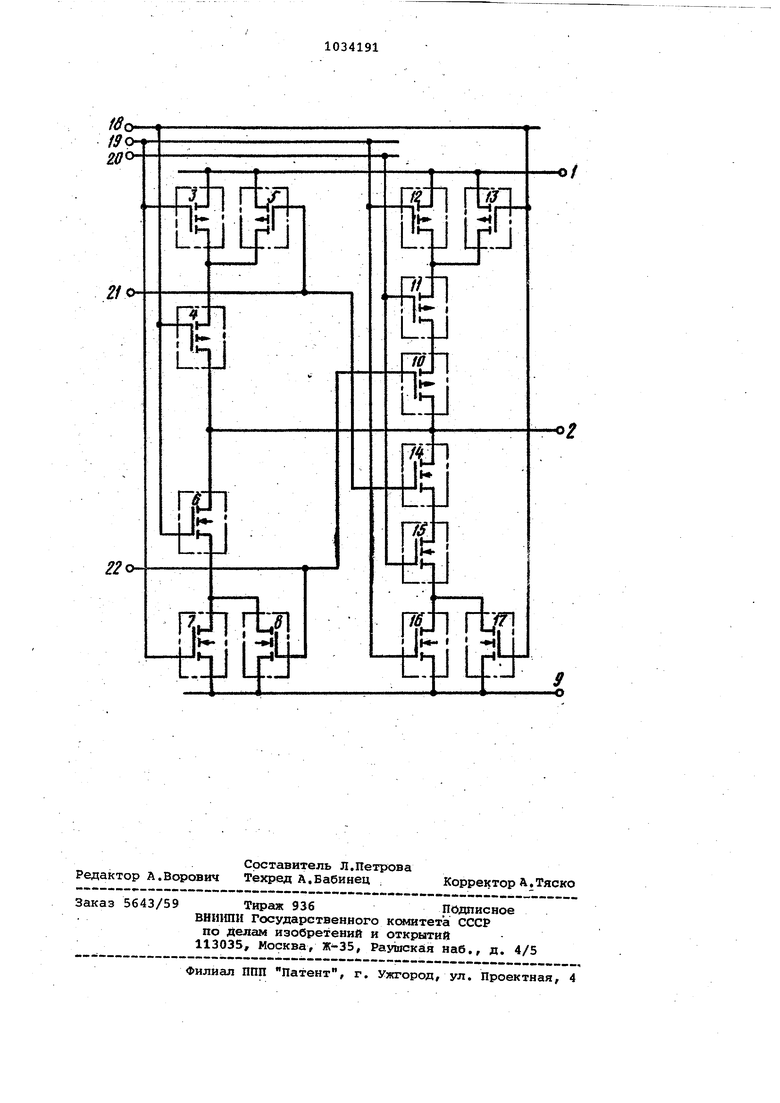

На чертеже представлена электрйческа,т принципиальная схема управляемого мажоритарного элемента на комплементарных МДП-транзисторах, где первая ветвь,, включенная между шиной 1 питания и выходной шиной 2, содержит последовательно включенные

первый и второй р -канальные транзисторы 3 и 4, при этом параллельно транзистору 3 подключен третий р -канальный транзистор 5,

0 Вторая ветвь содержит последовательно включенные V)-канальные четвертый и пятый транзисторы 6 и 7 и шестой h-канапьный транзистор 8, подключенный параллельно пятому

5 транзистору 7, и включена между выходной шиной 2 и общей шиной 9, Третья ветвь содержит последователь но включенные седьмой, восьмой и девятый Р-канальные транзисторы 10-12. Пахэаллельно транзистору 12 подключен десятый Р -канальный тран зистор 13. Истоки транзисторов 12 и- 13 подключены к шине, питания 1, сток транзистора 10 - к выходной шине 2. Четвертая ветвь содержит последовательно включенные одиннадцатый, двенадцатый, тринадцатый р-канальные транзисторы 14-16 и четырнадцатый , VI -канальный транзйсто 17, подключенный параллельно транзистору 16. Истоки транзисторов 16 и 17 подключены.к общей шине 9, а сток .транзистора 14 - к выходной шине 2 . Затворы транзисторов 4, б, 13 и 1.7 подключены к первой информационной шине 18, затворы транзисторов .3,7/12 и 16 - к второй информационной шине. 19, затворы транзисторов 11 и 15 - к третьей информационной шиме 20, затворы транзисторов 5 и Д4 - к прямому управляющему входу 21, а затворы транзисторов 8 и 10 к инверсному.управляющему входу 22. .Управляемый мажоритарный элемент работает следующим образом. При поступлении логической 1 на прямой управляющий вход 21 и логического О на инверсный управлйющйИ вход 22 элемент выполняет функцию мажоритования. Логический , О на первой 18 и второй.19, либо на первой 18 и третьей 20, либо на второй 19 и третьей 20,.либо на всех трех информационных шинах инициирует .заряд йыходной шины 2до уровня логической 1 через открытые мдатранзисторы соответственно 3,4, либо 10,11,13, либо 10, 11, 12, либо через все МДП-транзисторы с кана лами -типа, кроме транзистора 5. Логическая 1 на первой 18 и второй 19, либо на первой 18 и третьей 20, либо на второй 19 и третьей 20, либо на всех трех информационных 1яинах инициирует заряд шины 2 элемента до у ровня логического О через открытые МДП транзисторы соответственно 6,7 либо 14, 15, 17, либо через все МДЩ-транзисторы с каналами Vi-типа, кроме транзистора 8, При поступлении логического О на прямой 21 и логической 1 на инверсный 22 управляющие входы открываются транзисторы 5 и 8 и закрываются транзисторы 10 и 14, в результате чего выходным сигналом является инверсированный сигнал, поступаквдий на первую информационную шину 18. тТоложнтельный эффект при использовании предлагаемого элемента заключается в том, что уменьшение величины паразитной емкости. Образуемой стоками транзисторов, подключенных к выходу элемента, обеспечивает возможность построения быстродействующих многоканальных Мажоритарно-резервированных устройств.. Время заряда паразитной емкости . на. выходе элемента,в общем случае выражено функцией 8 уи T--KU- nCop.| Ntt p+Cov,rN«in, где К - коэффициент пропорциональ. ности; i(y ток заряда выходной емкрс.. ти, элемента; С г удельные емкости диффузион/ ных областей, МДП-транзисторов с каналами р и И -типа соответственно; , , - ширины стоковых областей Р мдп-транзисторов с kaнaлaми р- и и-типа соответственно, подключенных к выходу элемента, - число стоковых областей МДП транзисторов с каналами /t - и fV-типа соответственно, подключенных к выходу элемента. Выходная емкость известного элемента образована тремя стоками транзисторов с каналами | -типа и тремя стоками транзисторов с каналами iVl-типа. У предлагаемого элемента параметры б и VH равны 2, что обеспечивает, сокращение времени заряда выходной емкости на 30%.

/9020

of

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| Формирователь импульсов | 1982 |

|

SU1238230A1 |

| Операционный усилитель | 1988 |

|

SU1536503A1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2012 |

|

RU2496227C1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2013 |

|

RU2541854C1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| МАЛОШУМЯЩИЙ КВАРЦЕВЫЙ ГЕНЕРАТОР С АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКОЙ УСИЛЕНИЯ | 2012 |

|

RU2498498C1 |

УПРАВЛЯЕМЫЙ МАЗКОРИТАРНЫЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ MOT-TPAH-iЭИСТОРАХ, содержащий первую ветвь, включенную Между шиной питания и выходной шиной и состоящую из последовательно включенных первого и второго транзисторов, при этом параллельно первому транэ1нстору (чен. третий, транзистор, вторую ветв, включённую между выходной шиной и общей и состоящую из последовательно включенных четвертого и пятого транзисторов, при этом пятрму транзистору параллельно подключен шестой транзистор, третью ветвь,. состоящую из последовательно включенных транзистордв седьмо гр, восьмого и девятого, параллельно крторсхиу подключен десятый транзистрр, и четвертую , состоящую из последовательно включенных одиннадцатого, двенадцатогоИ т;рит надцатого транзисторов и четырнад цатого транзистора, подключенного па раллельно тринадцатому, причем затворы второго, четвертого, десятого и четырнадцатого транзисторов подключены к п ервой информационной шине, затворы первого, пятрго, девятого, тринадцатого транзисторов 9 к второй информационной шине, затворы восьмого и двенадцатогр - к третьей информсщионнбй шине, затворы третьего и одиннадцатого - к прямому управляющему, входу, а затворы шестого и седьмого - к инверсному утфавляющему входу, р т л и ч а ющ и и с я тем, что, с целью повышения быстрюдействия, истоки девятого и десятого транзисторов подключены к шине питания, тринадцатого и чеоо тьфиадцатого - к общей шине, а 1 стоки седьмого и одиннадцатого - к выходной ишне. со

tilylLf f

| Ядькнаенко Ю.М | |||

| Микрбмосоные цифровые интегральные схемы на основе дополняющих МОП-транзисто&ных структур | |||

| - Обзоры lio электронной техни- ке. | |||

| Сер | |||

| Микроэлектроника, вьт | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-08-07—Публикация

1982-04-15—Подача