транзистора, истоки второго и третьего ключевых транзисторов подключены к шине нулевого потенциала, затвор третьего нагрузочного транзистора подключен к стоку третьего ключевого транзистора, затвор третьего ключевого транзистора подключен к стоку второго ключевого транзистора, затвор пятого ключевого транзистора подключен к стоку девятого ключевого транзистора, затвор шестого ключевого транзистора подключен к стоку второго ключевого транзистора, затвор седьмого ключевого транзистора подключен к стоку первого ключевого транзистора, затвор тринадцатого ключевого транзистора подключен к стоку третьего ключевого транзистора, затвор четвертого нагрузочного транзистора подключен к стоку седьмого ключевого транзистора, затвор восьмого нагрузочного транзистора подключен к стоку девятого ключевого транзистора, исток - к стоку седьмого ключевого транзистора, затвор и исток девятого нагрузочного транзистора подключены к стоку шестнадцатого ключевого транзистора.

2. Буферный усилитель, содержащий клю-. чевые транзисторы с первого по четырнадцатый и нагрузочные транзисторы с первого по седьмой, стоки которых подключены к шине питания, затвор и исток первого нагрузочного транзистора подключены к стоку первого ключевого транзистора и к затвору второго ключевого транзистора, исток первого ключевого транзистора подключен к стхжу четвертого ключевого транзистора, исток Которого подключен к шине нулевого потенциала, затворы первого и четвертого ключевых транзисторов являются соответственно информационным входом и первым управляющим входом усилителя, затвор и исток второго нагрузочного транзистора подключены к стоку второго ключевого транзистора, исток третьего нагрузочного транзистора подключен к стоку третьего ключевого транзистора, исток четвертого нагрузочного транзистора подключен к стоку пятого ключевого транзистора, исток шестого ключевого транзистора подключен к стоку седьмого ключевого транзистора, исток которого подключен к шине нулевого потенциала, исток восьмого ключевого транзистора подключен к стоку девятого ключевого транзистора, исток десятого ключевого транзистора подключен к стоку одиннадцатого ключевого транзистора и является выходом усилителя, затвор и исток одиннадцатого ключевого транзистора подключены соответстйенно к стоку девятого ключевого транзистора и шине нулевого потенциала, сток двенадцатого ключевого транзистора подключен к шине питания, а исток двенадцатого ключевого транзистора подключен к истоку и затвору пятого нагрузочного транзистора и к затвору девятого ключевого транзистора, исток тринадцатого ключевого транзистора

подключен к щине нулевого потенциала, а сток - к истоку двена дцатого ключевого транзистора, затвор которого подключен к затвору и истоку LjecToro нагрузочного тран зистора, сток четырнадцатого ключевого транзистора подключен к истоку шестого нагрузочного транзистора, а затвор четырнадцатого ключевого транзистора подключен к стоку десятого ключевого транзистора, сток шестого ключевого транзистора подключен к щи не питания, сток восьмого ключевого транзистора является вторым управляющим входом устройства, исток и затвор седьмого нагрузочного транзистора подключены соответственно к стоку седьмого ключевого транзистора и к шине питания, исток пятого ключевого транзистора подключен к шине нулевого потенциала, отличающийся тем, что, с целью повышения быстродействия усилителя, в него введены восьмой и девятый нагрузочные транзисторы, стоки которых подключены к шине питания, пятнадцатый ключевой транзистор, затвор и сток которого подключены к истоку четырнадцатого ключевого транзистора, а исток - к шине нулевого потенциала, шестнадцатый ключевой транзистор, затвор которого подключен к стоку седьмого ключевого транзистора, и затвору десятого ключевого транзистора, исток - к шине нулевого потенциала, а сток шестнадцатого ключевого транзистора подключен к затвору восьмого ключевого транзистора, семнадцатый ключевой транзистор, затвор которого подключен к стоку седьмого ключевого транзистора, а исток и сток - к стоку пятого ключевого транзистора восемнадцатый ключевой транзистор, затвор которого подключен к стоку тринадцатого ключевого транзистора, сток - к щине питания, а исток - к стоку десятого ключевого транзистора, истоки второго, третьего и девятого ключевых транзисторов подключены к шине нулевого потенциала, затвор третьего нагрузочного транзистора подключен к стоку третьего ключевого транзистора, затвор третьего ключевого транзистора подключен к стоку второго ключевого транзистора, затвор пятого ключевого транзистора подключен к стоку девятого ключевого транзистора, затвор шестого ключевого транзистора подключен к стоку второго ключевого транзистора, затвор седьмого ключевого транзистора подключен к стоку первого ключевого транзистора, затвор тринадцатого ключевого транзистора подключен к стоку третьего ключевого транзистора, затвор четвертого нагрузочного транзистора подключен к СТОК) седьмого ключевого транзистора, затвор восьмого нагрузочного транзистора подключен к стоку девятого ключевого транзистора, исток - к стоку седьмого ключевого транзистора, затвор и исток девятого нафузочного транзистора подключены к стоку шестнадцатого ключевого транзистора.

Изобретение относится к вычислительной технике и может быть использовано при разработке различных запоминающих устройств цифровых МДП БИС динамического и квазипотенциального типов, особенно встроенных формирователей управляющих и выходных сигналов в виде интегральных схем.

Известен буферный усилитель, содержащий МДП-транзисторы. в том числе нагрузочные с первого по щестой и ключевые с первого по четырнадцатый, входную шину, выходную тину, шины разрешения работы, шину запрета работы, шину питания и шину общего потенциала, причем сток первого нагрузочного транзистора обедненHOio типа подключен к тине питания, его исТок и затвор соединены между собой, со стоком первого ключевого транзистора обогащенного типа, затвор которого подключен к входной информационной шине, сток второго нагрузочного транзистора обедненного типа - к шине питания, его затвор соединен с его истоком и подключен к стоку второго ключевого транзистора обогащенного типа, затвор которого подключен к стоку первого ключевого транзистора или выходу первого инвертора, сток третьего нагрузочного транзистора обедненного типа - к шине питания, его затвор - к затвору второго нагрузочного транзистора, а его исток соединен со стоком третьего ключевого транзистора обогащенного типа, затвор которого подключен к стоку первого ключевого транзистора, истоки первого, второго и третьего ключевых транзисторов соединены между собой и со стоком четвертого ключевого транзистора обогащенного типа, затвор которого подключен к первой тине разрешения выхода, а исток - к и1ине общего потенциала, четвертый нагрузочный транзистор обедненного типа включен между шиной питания и шиной общего потенциала через пятый и шестой ключевые транзисторы обогаиаенного типа, затвор четвертого нагрузочного транзистора соединен с его истоком и стоком пятого ключевого транзистора, а также с затвором пятого нагрузочного транзистора обедненного типа, затвор пятого ключевого транзистора - со стоком третьего ключевого транзистора, с которым соединены также затворы седьмого ключевого транзистора обогащенного типа и шестого нагрузочного транзистора обедненного типа, затвор шестого ключевого транзистора соединен с первой шиной разреи1ения выхода, сток восьмого ключевого транзистора с нулевым пороговым напряжением - с шиной питания, его исток - со стоком пятого нагрузочного транзистора, а затвор - с затвором девятого ключевого транзистора с нулевым пороговым напряжением и подключен к первой шине разрешения выхода, сток девятого клю чевого транзистора -- к шине питания, а его исток соединен со стоком шестого нагрузочного транзистора, испж которого соединен со стоками десятого, одиннадцатого и затвором двенадцатого ключевых транзисторов обогащенного типа, сток тринадцатого ключевого транзистора подключен к стоку седьмого ключевого транзистора, исток которого соединен с обшей шиной, затвор одиннадцатого ключевого транзистора - с затвором тринадцатого ключевого тран.зис

тора обогащенного типа и подключен к второй шине разрещения выхода, сток тринадцатого ключевого транзистора соединен с затвором четырнадцатого ключевого выходного транзистора обогащенного типа и подключен к общей шине, сток четырнадцатою

ключевого транзистора подключен к шине питания, а исток соединен с выходной шиной и стоком двенадцатого ключевого.транзистора, исток которого подключен к шине общего потенциала |1.

Недостатком этого усилителя является

низкое быстродействие.

Наиболее близким техническим решением к изобретению является буферный усилитель, содержащий нагрузочные транзисторы с первого по седьмой, ключевые транзисторы с первого по четырнадцатый, входную и выходную шины, шины управления разрешением выхода, шину питания и общую шину, причем сток первого нагрузочного транзистора подключен к шине питания, затвор и исток - к стоку tiepBoro ключевого транзистора и к затворам второго и третьего ключевых транзисторов соответственно, истоки ключевых транзисторов с первого по третий - к стоку четвертого ключевого транзистора, исток которого подключен к общей

шине, затворы первого и четвертого ключевых транзисторов являются соответственно информационным входом и первой шиной управления разрешением выхода, затворы второго и третьего нагрузочных транзисторов подключены к истоку второго нагрузочного транзистора и к стоку второго ключевого транзистора, исток третьего нагрузочного транзистора - к стоку третьего ключевого транзистора, затвор и исток четвертого нагрузочного транзистора - к стоку пятого ключевого транзистора и к затвору шестого ключевого транзистора с нулевым пороговым напряжением, исток шестого ключевого транзистора - к стоку седьмого ключевого транзистора, исток которого подключен к общей шине, затвор восьмого ключевого транзистора с нулевым пороговым напряжением - к затворам пятого и седьмого ключевых транзисторов и стоку третьего ключевого транзистора, исток восьмого ключевого транзистора - к стоку девятого ключевого транзистора, затвор десятого ключевого т; анзистора - к стоку седьмого ключевого транзистора, исток десятого ключевого транзистора - к стоку одиннадцатого ключевого транзистора и является выходом

устройства, затвор и исток одиннадцатого ключевого транзистора подключены соответственно к стоку девятого ключенюго транзистора и к общей тине, пятый нагрузочный транзистор, исток и затвор которого соединены между собой и подключены к затвору девятого ключевого транзистора, затвор и исток шестого нагрузочного транзистора - к затвору двенадцатого ключев мо транзистора с нулевым пороговым напряжением, сток которого подключен к шине питания, а исток восьмого ключевого транзистора соединен с затвором пятого нагрузочного транзистора и стоком тринадцатого ключевого транзистора, исток которого подключен к общей щи не, а затвор - к стоку третьего ключевого транзистора, затвор и сток седьмого нагрузочного транзистора, а также стоки второго, третьего, четвертого, пятого и шестого нагрузочных и шестого ключевого транзисторов - к тине питания, исток седьмого нагрузочного транзистора соединен со седьмого ключевого транзистора, сток четырнадцатого ключевого транзистора подключен к истоку шестого нагрузочного транзистора, а затвор - к стоку десятого ключевого транзистора и к первому выводу нагрузочного резистора, второй вывод которого подключен к шине питания, исток четырнадцатого ключевого транзистора соединен с общей шиной, сток шестого ключевого транзистора подключен к шине питания, а сток восьмого ключевого транзиртора - к второй шине управления разрешением выхода 2.

Недостатком известного усилителя является низкое быстродействие, связанное с его собственными внутренними задержками и задержками формирования на выходной шине выходного логического перепада на емкостную нагрузку 100 пФ и более.

Целью изобретения является повышение быстродействия усилителя.

Поставленная цель со1чаасно первому варианту достигается тем, что в буферный усилитель, содержащий ключевые транзисторы с первого по четырнадцатый н нагрузочные транзисторы с первого по седьмой, стоки которых подключены к шине питания, затвор и исток первого нагрузочного транзистора - к стоку первого ключевого транзистора и к затвору второго ключевого транзистора, исток первого ключевого транзистора - к стоку четвертого ключевого транзистора, исток которого подключен к шине нулевого потенциала, затворы первого и четвертого ключевых транзисторов являются соответственно информационным входом и первым управляющим входом усилителя, затвор и исток второго нагрузочного тран-. .зистора подключен к стоку второго ключевого транзистора, исток третьего нагрузочного транзистора --- к стоку третьего ютючевого транзистора, исток четвертого нагрузочного

транзистора - к стоку пятого ключевого транзистора, исток шестого ключевого транзистора - к стоку седьмого ключевого транзистора, исток которого подключен к шине 5 нулевого потенциала, исток восьмого ключевого транзистора - к стоку девятого ключевого транзистора, исток десятого ключевого транзистора - к стоку одиннадцатого ключевого транзистора и является вы0 ходом усилителя, затвор и исток одиннадцатого ключевого транзистора подключены соответственно к стоку девятого ключевого транзистора и шине нулевого потенциала, сток двенадцатого ключевого транзистора - к шине питания, а исток - к истоку и зат5вору пятого нагрузочного транзистора и к затвору девятого ключевого транзистора, исток тринадцатого ключевого транзистора - к шине нулевого потенциала, а сток - к истоку двенадцатого ключевого транзистора,

0 затвор которого подключен к затвору и истоку шестого нагрузочного транзистора, сток четырнадцатого ключевого транзистора подключен к истоку шестого нагрузочного транзистора, а затвор четырнадцатого ключевого транзистора --к стоку десятого клю5чевого транзистора, сток десятого ключевого транзистора через нагрузочный резистор - к шине питания, сток шестого ключевого транзистора - к питания, сток восьмого ключевого транзистора является

„ вторым управляющим входом устройства, исток и затвор седьмого нагрузочного транзистора подключены соответственно к стоку седьмого ключевого транзистора и к шине питания, исток пятого ключевого транзистора - к шине нулевого потенциала, введе5 ны восьмой и девятый нагрузочные транзисторы, стоки которых подключены к шине питания, пятнадцатый ключевой транзистор, затвор и сток которого подключены к истоку четырнадцатого ключевого транзистора, а исток - к шине нулевого потенциала,

0 шестнадцатый ключевой транзистор, затвор которого подключен к стоку седьмого и затвору десятого ключевых транзисторов, исток - к шине нулевого потенциала, а сток - к затвору восьмого ключевого транзистора,

5 семнадцатый ютючевой транзистор, затвор которого подключен к стоку седьмого ключевого транзистора, а исток и сток - к стоку пятого ключевого транзистора, исток , третьего и девятого ключевых транзисторов - к шине нулевого потенциала,

затвор третьего нагрузочного транзистора - к стоку третьего ключевого транзистора, затвор третьего ключевого транзистора - к стоку второго ключевого транзистора, затвор пятого ключевого транзистора - к сто ку девятого ключевого транзистора, затвор шестого ключевого транзистора - к стоку второго ключевого транзистора, затвор седьмого ключевого транзистора -- к стоку первого ключевого транзистора, .чатвор тримадцатого ключевого транзистора -- к стоку третьего ключевого транзистора, затвор четвертого нагрузочно1о транзистора - к стоку сел.ьмого ключевого транзистора, затвор восьмого нагрузочного транзистора - к стоку девятого ключевого транзистора, исток - к стоку седьмого ключевого транзистора, затвор и исток девятого нагрузочного транзистора - к стоку шестнадцатого ключевого транзистора.

При этом согласно второму варианту в буферный усилитель, содержащий ключевые транзисторы с нервого по четырнадцатый и нагрузочные транзисторы с первого по седьмой, стоки которых подключены к шине.питания, затвор н исток первого нагрузочного транзистора - к стоку первого ключевого транзистора и к затвору второго ключевого транзистора, исток нервого ключевого транзистора - к стоку четвертого ключевого транзистора, исток которого подключен к шине нулевого потенциала, затворы перво1ои четвертого ключевых транзисторов являются соответственно информационным входом и первым управ тяюшим входом усилителя, затвор и исток второго нагрузочного транзистора подключены к стоку второго ключевого транзистора, исток третьего нагрузочного транзистора - к стоку третьего ключевого транзистора, исток четвертого нагрузочного транзистора - к стоку пятого ключевого транзистора, исток шестого ключевого транзистора - к стоку седьмого ключевого транзистора, исток которого подключен к шине нулевого потенциала, исток восьмого ключевого транзистора - к стоку девятого ключевого транзистора, исток которого подключен к Н1ине нулевого потенциала, сток десятого ключевого транзистора - к стоку одиннадцатого ключевого транзистора и является выходом усилителя, затвор и исток одиннадцатого ключевого транзистора подключены соответственно к стоку девятого ключевого транзистора и шине нулевого потенциала, сток двенадцатого ключевого транзистора - к шине питания, а исток двенадцатого ключевого транзистора - к истоку и затвору пятого нагрузочного транзистора и к затвору девятого ключевого транзистора, исток тринадцатого ключевого транзистора - к шине нулевого потенциала, а сток - к истоку двенадцатого ключевого транзистора, затвор которого подключен к затвору и нстоку шестого нагрузочного транзистора, сток четырнадцатого ключевого транзистора - к истоку шестого нагрузочного транзистора, а затвор четырнадцатого ключевого транзистора - к стоку десятого ключевого транзистора, сток шестого ключевого транзистора - к шине питания, сток восьмого ключево1о транзистор; является вторым управляющим входом устройства, исток и затвор седьмого нагрузочного транзистора подключены соответственно к CTOKV седьмого

ключевого транзистора и к шине питания, исток пятого ключевого транзистора к шине нулевого потенциала, введены восьмой н девятый нагрузочные транзисторы.

стоки которых подключены к шине питания, пятнадцатый ключевой транзистор, затвор и сток которого подключены к истоку четырнадцатого ключевого транзистора, нсток пятнадцатого ключевого транзистора -- к

шине общего потенциала, шестнадцатый ключевой транзистора, затвор которого подключен к стоку седьмого ключевого транзистора, и затвору десятого ключевого транзистора, исток - к шине обн1его потенциала, а сток шестнадцатого ключевого транзис5 тора - к затвору восьмого ключевого транзистора, семнадцатый ключевой транзистор, затвор которого подключен к стоку седьмого ключевого транзистора, а исток и сток - к стоку пятого ключевого транзистора, во- семнадцатый ключевой транзистор, затвор которого подключен к стоку тринадцатого ключевого транзистора, сток - к шине питания, а исток восемнадцатого ключевого транзистора - к стоку десятого ключевого транзистора, истоки второго, третьего и де5 сятого ключевых транзисторов - к шнне общего потенциала, затвор третьего нагрузочного транзистора - к стоку третьего ключевого транзистора, затвор третьего ключевого транзистора - к стоку второго ключевого транзистора, затвор пятого клю0чевого транзистора - к стоку девятого ключевого транзистора, затвор шестого ключевого транзистора - к стоку второго ключево го транзистора, затвор седьмого ключевого транзистора - к стоку первого ключевого транзистора, затвор тринадцатого ключевого транзистора - к стоку третьего ключевого транзистора, затвор четвертого нагрузочного транзистора - к стоку седьмого ключевого транзистора, затвор восьмого нагрузочного транзистора - к стоку девятого

0 ключевого транзистора, исток - к стоку седьмого ключевого транзистора, а затвор и исток девятого нагрузочного транзистора - к стоку шестнадцатого ключевого транзистора.

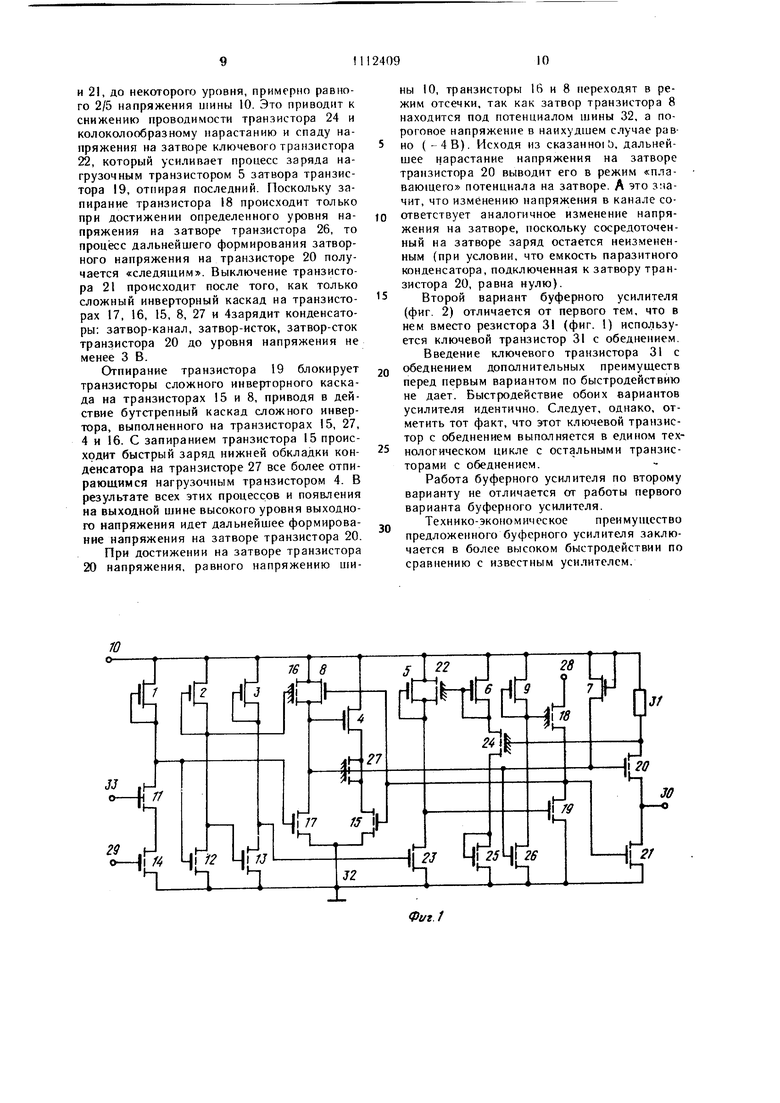

На фиг. 1 изображена принципиальная

электрическая схема первого варианта буферного усилителя; на фиг. 2 - второго варианта.

Буферный усилитель по первому варианту содержит (фиг. 1) нагрузочные транзнс0 торы 1-9 с первого по девятый обедненного типа, шину 10 питания, ключевые транзисторы II-27 с первого по семнадцатый (из них транзисторы 11 - 15, 17, 19-21. 23, 25 и 26 - обогащенного типа, а транзнстЬрм 16, 18, 22, 24 и 27 - с нулевым напряжени55 ем), первую 28 и вторую 29 щины разрешения выхода, выходную шину 30, резистор 31, щи ну 32 нулевого потенциала и входную информационную шину 33.

Работа буферного усилите;1Я разрешается сигналами ра. репгения выхода по шинам 28 и 29, имеюиикми высокий уровень напря;кен11я, равный напряжению шины 10. От экич) нысокого уровня напряжения включается ключевой транзистор 14, соединяя испи транзистора 1 1 с гинной 32. Выходные к.; к чевые транзисторы 20 и 21 из закрытого состояния (высокон.мпедансного) переходят в рабочий режим считывания информации: выходно1Ч) напряжения логического нуля (U аыу) либо выходного напряжения логической единицы (ивых) в зависимости от уровня логического напряжения на информационном входе 33.

Пусть работа буферного усилителя рассматривается с момента, когда входное напряжение на информационном входе 33 соответствует уровню логического нуля. Инверторный каскад на транзисторах 11 и 1 инвертирует этот низкий уровень входного напряжения и открывает ключевые транзисторы 12 и 17, отчего напряжение на стоках этих транзисторов падает до потенциала шины 3.2, разряжая затворы нагрузочного транзистора 2, ключевых транзисторов 16 и 13, переводя их в закрытое состояние. По мере понижения потенциала на стоке транзистора 2 нарастает напряжение на затворе ключевого транзистора 23 и стоке закрытого -paii3HCTOpa 13, которое передается через ;:агрузочный транзистор 3, шунтируя затвор транзистора 19 на шину 32, запирая иосf ел ни и.

Одновременно с закрыт41ем ключевого транзистора 20 запирается транзистор 26, позволяя нагрузочному транзистору 9 зарядить затвор транзистора 18 до напряжения шины 10. Заряд затворов транзисторов 23, 15 и 8 некоторое время удерживается выключением транзистора 19, так как внутренние задержки прохождения входного сигнала до затвора ключевого транзистора 8 с нулевым пороговым напряжением меньше внутрення.х задержек прохождения входного сигнала до затвора транзистора 19. Тем lie менее скорость разряда выходной шины с емкостью нагрузки пФ выходным ключевым транзистором 21 происходит за очень короткое время, так как ключевой TpaH3MCtop 20 запирз-ртся раньше, чем открЬ|Чя.--с« транзистор 21. После запирания транзистора 20 напряжение на стоке данного тра гзистора и затворе ключевого транзистора 24 с нулевым пороговым напряжением повышается до напряжения шины 10 за счет протекания тока через резистор 31.

Потенциал на стоке транзистора 24 и затво}Х ключевого транзистора 22 понижается до определенного уровня, который задается. выбором соотношений ширины канала W к длине канала L транзистора 24 и транзистора 25, включенного диодом, т.е. затвор со стоком соединены вместе. Транзистор 6 является нагрузочным транзистором с обеднением для более резкого нарастания напряжения на затворе транзистора 22 в момент срабатывания обратной связи, которая за5 водится СОстока транзистора 20 на транзисторы 24, 25 и 6. Снижение проводимости транзистора 22 за счет отрицательной обратной связи со стока транзистора 20 на затвор транзистора 24 - нагрузочный транзис0 тор 5 с обеднением выполнен длинноканальным - позволяет более быстро разрядить уз ловой конденсатор; затвор транзистора 1§, диффузионные области - сток транзистора 23, истоки транзисторов 22 и 5. Огкрывание транзистора 15 разряжает до уровня

5 логического нуля нижнюю обкладку МДПконденсатора, выполненного на транзисторе 27 с нулевым пороговым напряжением. Нагрузочный транзистор 4 с обеднением подзапирается низким уровнем логического нуля

0 на затворе, в результате чего ключевой транзистор 15 выполняется с меньшим соотношением W/L, а значит представляет и меньший паразитный конденсатор для предыдуш.его инверторного каскада на транзисторах 19 и 18.

5Теперь допустим, что напряжение на информационном входе 33 возросло до уровня логической единицы и проводимость ключевого транзистора I 1 резко повысилась. Вследствие этого через нагрузочный транзистор I

обедненного типа и транзистор 11 протекает ток, а на выходе транзистора I устанавливается уровень логического нуля, достаточный для запирания ключевых транзисторов 12 и 17 и отпирания транзисторов 16 и 13. Нагрузочный транзистор 2 обедненного типа

выбирается более мощным по сравнению с нагрузочными транзисторами I и 3 по крайней мере в 2 раза. Это обеспечивает более быстрое отпирание ключевого транзистора 16 с нулевым пороговым напряжением, вызывая тем самым протекание тока, который,

суммируясь с током открытого нагрузочного транзистора 8 (W/L 1), обеспечивает быстрый заряд конденсаторов затворов транзисторов 20 и 27 (верхней обкладки МДП-конденсатора). Крутой фонд нарастания напря5 жения на затворе транзистора 20 обусловлен тем, что ключевой транзистор 17 запирается чуть раньше входным инвертором, образованным транзисторами И и I, чем производится формирование напряжения на затворе транзистора 20.

Одновременно с открыванием транзистора 20 открывается и транзистор 26, так как они имеют объединенные затворы, подключенные к одному и тому же выходу сложного инвертора, выполненного на транзис, торах 17. 16, 15, 8, 27 и 4, блокируя прово димость транзистора 18. С нарастанием напряжения на затворе транзистора 20 происходит разряд затвора транзистора 24, вследствие проводимости транзисторов 20

и 21, до некоторого уровня, примерно равного 2/5 напряжения шины 10. Это приводит к снижению проводимости транзистора 24 и колоколообразному нарастанию и спаду напряжения на затворе ключевого транзистора 22, который усиливает процесс заряда нагрузочным транзистором 5 затвора транзистора 19, отпирая последний. Поскольку запирание транзистора 18 происходит только при достижении определенного уровня напряжения на затворе транзистора 26, то процесс дальнейшего формирования затворного напряжения на транзисторе 20 получается «следящим. Выключение транзистора 21 происходит после того, как только сложный инверторный каскад на транзисторах 17, 16, 15, 8, 27 и 4зарядит конденсаторы; затвор-канал, затвор-исток, затвор-сток транзистора 20 до уровня напряжения не менее 3 В.

Отпирание транзистора 19 блокирует транзисторы сложного инверторного каскада на транзисторах 15 и 8, приводя в действие бутстрепный каскад сложного инвертора, выполненного на транзисторах 15, 27, 4 и 16. С запиранием транзистора 15 происходит быстрый заряд нижней обкладки конденсатора на транзисторе 27 все более отпирающимся нагрузочным транзистором 4. В результате всех этих процессов и появ-тения на выходной шине высокого уровня выходного напряжения идет дальнейшее формирование напряжения на затворе транзистора 20.

При достижении на затворе транзистора 20 напряжения, равного напряжению шины 10, транзисторы 16 и 8 переходят в режим отсечки, так как затвор транзистора 8 находится под потенциалом шины 32, а пороговое напряжение в наихудшем случае равно (-4В). Исходя из сказанно1Ь, дальнейшее нарастание напряжения на затворе транзистора 20 выводит его в режим «плавающего потенциала на затворе. А это значит, что изменению напряжения в канале соответствует аналогичное изменение напряжения на затворе, поскольку сосредоточенный на затворе заряд остается неизмененным (при условии, что емкость паразитного конденсатора, подключенная к затвору транзистора 20, равна нулю).

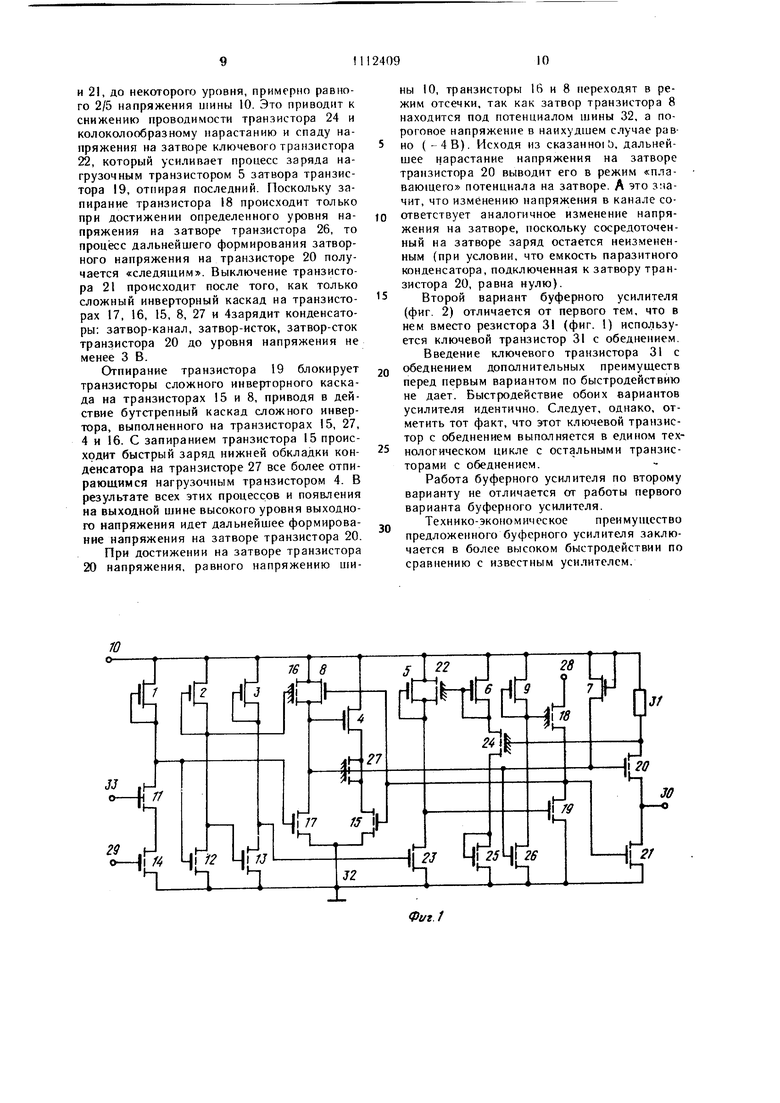

Второй вариант буферного усилителя (фиг. 2) отличается от первого тем, что в нем вместо резистора 31 (фиг. 1) используется ключевой транзистор 31 с обеднением. Введение ключевого транзистора 31 с обеднением дополнительных преимуществ перед первым вариантом по быстродействию не дает. Быстродействие обоих вариантов усилителя идентично. Следует, однако, отметить тот факт, что этот ключевой транзистор с обеднением выпапняется в едином технологическом цикле с остальными транзисторами с обеднением.

Работа буферного усилителя по второму варианту не отличается от работы первого варианта буферного усилителя.

Технико-экономическое преимущество предложенного буферного усилителя заключается в более высоком быстродействии по сравнению с известным усилителем.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Операционный усилитель | 1990 |

|

SU1741255A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Операционный усилитель | 1988 |

|

SU1536503A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

1. Буферный усилитель, содержащий ключевые транзисторы с первого по четырнадцатый и нагрузочные транзисторы с первого по седьмой, стоки которых подключены к шине питания, затвор и исток первого нагрузочного транзистора подключены к стоку первого ключевого транзистора и к затвору второго ключевого транзистора, исток первого ключевого транзистора подключен к стоку четвертого ключевого транзистора, исток которого подключен к шине нулевого потенциала, затворы первого и четвертого ключевых транзисторов являются соответственно информационным входом и первым управляющим входом усилителя, затвор и исток второго нагрузочного транзистора подключены к стоку второго ключевого транзистора, исток третьего нагрузочного транзистора подключен к стоку третьего ключевого транзистора, исток четвертого нагрузочного транзистора подключен к стоку пятого ключевого транзистора, исток шестого ключевого транзистора подключен к стоку седьмого ключевого транзистора, исток кот торого подключен к нжне нулевого потенциала, исток восьмого ключево1о транзистора подключен к стоку девятого ключевого транзистора, исток десятого ключевого транзистора подключен к стоку одинадцатого ключевого транзистора и является выходом усилителя, затвор и исток одиннадцатого ключевого транзистора подключены соответственно к стоку девятого ключевого транзистора и шине нулевого потенциала, сток двенадцатого ключевого транзистора подключен к шине питания, а исток - к истоку и затвору пятого нагрузочного транзистора и к затвору девятого ключевого транзистора, исток тринадцатого ключевого транзистора подключен к шине нулевого потенциала, а сток - к истоку двенадцатого ключевого транзистора, затвор которого подключен к затвору и истоку шестого нагрузочного транзистора, сток четырнадцатого ключевого транзистора подключен к истоку шестого нагрузочного транзистора, а затвор четырнадцатого ключевого транзистора - к стоку десятого ключевого транзистора, сток десятого ключевого транзистора через нагрузочный резистор подключен к шине питания, сток шестого ключевого транзистора подключен к нжне питания, сток восьмого ключевого транзистора является вторым управляющим входом усилителя, исток и зат-. вор седьмого нагрузочного транзистора под ключены соответственно к стоку седьмого ключевого транзистора и шине питания, исток пятого ключевого транзистора подключен к шине нулевого потенциала, отличающийся тем, что, с целью повышения его быстродействия, в него введены восьмой и девятый нагрузочные транзисторы, стоки которых подключены к шине питания, пятСО надцатый ключевой транзистор, затвор и сток которого подключены к истоку четырнадцатого ключевого транзистора, а исток - к шине нулевого потенциала, шестнадцатый ключевой транзистор, затвор которого подключен к стоку седьмого ключевого транзистора, затвор которого подключен к стоку седьмого и затвору десятого ключевых транзисторов, исток - к шине нулевого потенциала, а сток - к затвору восьмого ключевого транзистора, семнадцатый ключевой транзистор, затвор которого подключен к стоку седьмого ключевого транзистора, а исток и сток - к стоку пятого ключевого

| I | |||

| Патент США № 4103189, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| опублик | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-09-07—Публикация

1983-04-20—Подача