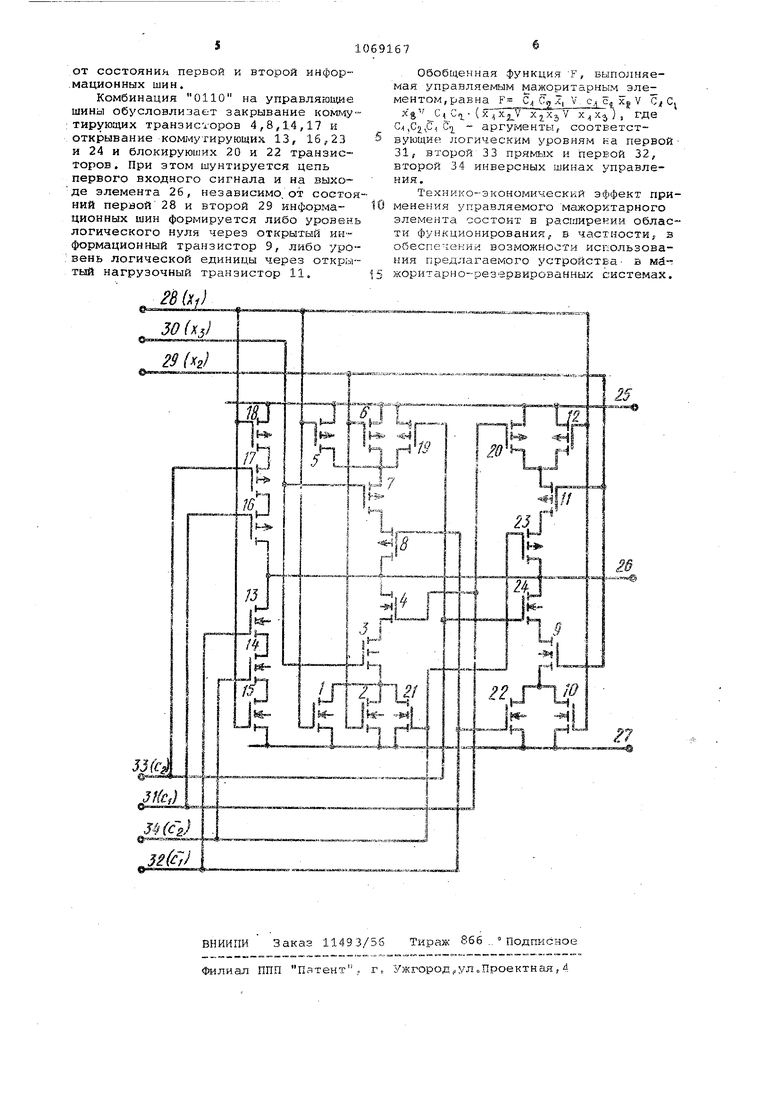

Изобретение относится к вычислительной технике и может быть исполь зовано при построении многоканальных вычислительных систем, в частности, для поканального разделения, а также мультиплексирования каналов Известен мажоритарный элемент на взаимно-дополняющих МДП-транзисторах С1. Использование такого мажоритарно го элемента затруднено при построеНИИ многоканальных систем, работаю(цих в режимах поканального разделе ния. Наиболее близким по технической сущности к изобретению является упр ляемый мажоритарный элемент, содержащий первый, второй, третий, четве тый, пятый, шестой, седьмой МДП-тра зисторы р-типа и восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый МДП-тран зисто |Ы п-типа, причем первый, второй, третий и восьмой,девятый, деся тый транзисторы включены последовательно между выходом элемента и шинами, соответственно Питание и Земля, четвертый и одиннадцатый транзисторы включены параллельно третьему и десятому, соответственно пятый, шестой, двенадцатый, тринадцатый транзисторы включены последов тельно между выходом элемента и шинами, соответственно Питание и Земля, седьмой и четырнадцатый транзисторы включены параллельно пятому и двенадцатому, соответствен но, затворы седьмого и восьмого тра зисторов соединены с прямыми управляющими входами, первого и четырнад .цатого - с инверсным, третьего, шес того, десятого и тринадцатого - с первой информационной шиной, четвер того, пятого, одиннадцатого и двена цатого - с второй, второго и девято го - с третьей С2, Однако использование известного элемента в многоканальных системах не обеспечивает возможности организации режима мультиплексирования каналов, тогда как такая необходимость возникает при проверке функционирования устройства. Целью изобретения является расширение функциональных возможностей управляемого мажоритарного элемента Цель достигается тем, что в упра ляемом мажоритарном элементе, на взаимодополняющих МДП-транзисторах, содержащем первый и второй информадионные транзисторы п-типа, истоки которых подключены к стоку третьего информационного транзистора п-типа, исток которого соединен со стоком первого коммутирующего транзистора п-типа, параллельно включенные первый и второй нагрузочные транзисторы р-типа, истоки которых подключены к стоку третьего нагрузочного транзистора р-типа, исток которого соединен со стоком второго коммутирующего транзистора р-типа, последовательно включенные четвертый и пятый информационные транзисторы п-типа, последовательно включенные четвертый и пятый нагрузочные транзисторы р-типа, шину источника питания, с которой соединены стоки первого, второго пятого нагрузочных транзисторов, выходную шину, к которой подключены HCTOKHJ первого и второго коммутирующих транзисторов, общую шину, соединенную со стоками первого, второго и пятого информационных транзисторов, первую информационную шину, к которой подключены затворы первого, пятого информационных и первого, пятого нагрузочных транзисторов, вторую информационную шину, соединенную с затворами второго, четвертого информационных и второго, четвертого нагрузочных транзисторов, третью информационную шину, к которой Подключены затворы третьего информационного и третьего нагрузочного транзисторов, шины первого прямого и первого инверсного сигналов управления, к которым подключены соответственно затворы первого и второго коммутирующих транзисторов, введены третий, четвертый коммутирующие и шестой информационные тран ясторы п-типа, последовательно включенные между выходной и общей шинами, пятый, шестой коммутирующие и шестой нагрузочные транзисторы р-типа, поел едовательно включенные между выходной шиной и. шиной источника питания, параллельно второму, пятому нагрузочным и второму, пятому информационным транзисторам включены соответственно первый, второй р-типа и третий, четвертый п-типа блокирующие транзисторы, истоки седьмого р-типа и восьмого п-типа коммутирующих транзисторов соединены с выходной шиной, а стоки подключены соответственно к истокам четвертого нагрузочного и четвертого информационного транзисторов, затворы шестого информационного и шестого нагрузочного транзисторов соединены с первой информационной шиной, затворы второго блокирующего и пятого коммутирующего транзисторов соединены с шиной первого прямого сигнала управления, затворы четвертого блок11руюш;егои третьего коммутирующего транзисторов соединены с шиной первого инверсного сигнала управления, затворы первого блокирующего, шестого восьмого, коммутирующих транзисторов соединены с шиной второго прямого сигнала управления, затворы третьего блокирующего, четвертого, седьмого коммутирующих транзисторов соединены с шиной второго инберсного сигнала управления. На чертеже представлена принципиальная схема управляемого мажоритарного элемента на взаимодополняющих МДП-транзисторах. Истоки параллельно включенных первого 1 и второго 2 информационных транзисторов п-типа подключены к сто ку третьего 3 информационного транзистора п-типа, исток которого соеди нен со стоком первого коммутирукядего транзистора 4 п-типа. Истоки параллельно включенных первого 5 и второг б нагрузочных, транзисторов р-типа подключены к стоку третьего 7 нагрузочного транзистора р-типа, исток которого.соединен со стоком второго 8 коммутирующего транзистора р-типа Информационные четвертый 9 и пятый 10 транзисторы п-типа включены после довательно, нагрузочные четвертый 1 и пятый 12 транзисторы р-типа включены последовательно, и третий 13 и четвертыР( 14 коммутирующие и шестой 15 информационные транзисторы р-типа включены последовательно, пятый 16, шестой 17 коммутирующие и шестой 18 нагрузочный транзисторы р-типа включены последовательно. Первый 19, второй 20 р-типа и третий 21, четвертый 22 п-типа бло. кирующие транзисторы включены параллельно соответственно транзисторам 6, 12 и 2, 10. Сток седьмого 23 коммутирующего транзистора р-типа подключен к истоку транзистора 11, сток восьмого 24 ког 1мутирующего транзистора п-типа подключен к истоку транзистора 9. К шине 25 источника питания подключены стоки транзисторов 5,6,12,18,19 и 20, выходная шина 26 элемента соединена с истоками транзисторов 4,8,13,16, 23 и 24, к общей шине 27 подключены стоки транзисторов 1,2,10,15,21 и 22 К первой информационной шине 28 подключены затворы транзисторов 1,5,10, 12,15 и 18, которая информационная шина 29 соединена с затворами транзисторов 2,6,9 и 11, к третьей инфор мационной шине 30 подключены затворы транзисторов 3 и 7. Шины первого пря мого 31 и первого, инверсного 32 сигналов управления соединены соответственно с затворами транзисторов 4, 16, 20 и 8, 13, 22. Затворы транзисторов 17, 19 и 24 соединены с шиной 33 второ.го прямого сигнала управления, а затворы транзисторов 14, 21 и 23 - с шиной 34 второго инверсного сигнала управления. Управляемый мажоритарный элемент работает следующим образом, При наличии логической единицы на первой 31,и второй 33 шинах прямых сигналов управления и логического нуля на первой 32 и второй 34 шинах инверсных сигналов управления открыта коммутирующие транзисторы 4, 8, 23 и 24, а коммутирующие 13, 14, 16, 17 и блокирующие 20, 19, 21 и 22 транзисторы закрыты. При этом наличие логического нуля на первой 28 и второй 29 либо на первой 28 и третьей 30, либо на второй 29 и третьей 30, либо на первой 28, второй 29 и третьей 30 информационных шинах обеспечивает формирование на выходной шине 26 элемента логической единицы через открытые нагрузочные транзисторы соответственно 11, 12 либо 5, 7 либо 6, 7, либо 5, 6, 7, 11 и 12, Уровни логической единицы при указанных выше комбинациях сигналов на информационных шинах обеспечивают формирование логического нуля на шине 26 элемента через открытые информационные транзистоЕЛл соответственно 9, 10 либо 1, 3, либо 2, 3, либо 1,2,3,9 и 10. Таким образом, в этом случае элемент реализует логическую функцию f х xj vxj X:jvjc icj , где - аргументы, соответствующие логическим уровням на первой 28, второй 29 и третьей 30 информационных шинах. При наличии на шинах первого прямого 31, второго прямого 33, первого инверсного 32 и второго инверсного 34 сигналов управления комбинаций югических уровней ООН, 1001 , ОНО функции, вып6.лняемые элементами, соответственно равны f х, f xg, f xj,. Действительно, при комбинации ООН коммутирующие транзисторы 4, 8, 23 и 24 закрыты, а 13,14, 16 и 17 - открыты и на выходной шине 26 формируется уровень логической единицы через открытый нагрузочный транзистор 18 при наличии уровня логического нуля на первой информационной шине 28, либо уровень логического нуля через открытый информационный транзистор 15 при наличии логической единицы на шине 28. При комбинации логических си налрв на управляющих шинах 1001 открыты коммутирующие транзисторы 4,8,14,1Я и закрыты коммутирующие транзисторы 13,16,23 и 24; открытые блокирующие транзисторы 19 и 21 шунтируют цепи первого и второго входных сигналов и на выходе элемента 26 формируется либо уровень логического нуля через открытый информационный транзис±ор 3 либо уровень логической единицы через открытый. нагрузочный транзистор 7, при наличии на третьей информационной шине соответственно либо уровня логической единицы, либо уровня логического нуля, независимо

от состояния первой к второй информационных шин.

Комбинация ОНО на управляюише шины обусловлизает закрывание коммутирующих транзисторов 4,8,1.4,17 к открывание ком мутирующих 13, 16,22 и 24 и блокируюших 20 и 22 транзисторов. При этом шунтируется цепь первого входного сигнала и на выходе элемента 26, независимо, от состояний первой28 и второй 29 информационных шин формируется либо уровень логического нуля через открытый информационный транзистор 9, либо уровень логической единицы через открытый нагрузочный транзистор 11.

Обобщенная функция F, выполняемая управляемым мажоритарным элемент ом, ра в н ,, xj V : Cj

( ) S где Си (CjvC Clj - аргументы, соответствующи€ логическим уровням ка первой 31, второй 33 прямых и первой 32, второй 34 инверсных шинах управления.

Технико-экономический эффект применения управляемого мажоритарного элемента состоит в расширении области функционирования,. Б частностиг в обеспечений возможности использования предлагаемого устройства- в мА-жоритарно-резервированныу. системах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064470A1 |

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064471A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2011 |

|

RU2449469C1 |

| Д-триггер | 1985 |

|

SU1261085A1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 2015 |

|

RU2580080C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

УПРАВЛЯЕМЫЙ МАЖОРИТАРНЫЙ ЭЛЕМЕНТ, На взаимодополняющих МДПтранзисторах, содержащий первый и второй информационные транзисторы п-типа, истоки которых подключены к стоку третьего информационного транзистора п-типа, исток которого соединен со стоком первого коммутирующего транзистора п-типа, паралг лельно включенные первый и второй нагрузочные транзисторы р-типа, истоки которых подключены к стоку третьего нагрузочнозх тра1;зистора р-типа,исток которого соединен со стоком второго коммутирующего транзистора р-типа,последовательно включенные четвертый и пятый информационные транзисторы п-типа,последовательно включенные четвертый и пятый нагрузочные транзисторы р-типа, шину источника питания, с которой соединены стоки первого, второго и пятого нагрузочных транзисторов,выходную шину, к которой подключены истоки первого и второго коьв утирующих транзисторов, общую шину, соединенную со стоками первого, второго и пятого информационных транзисторов, первую информационную шину, к которой подключены затворы первого, пятого информационных и первого, пятого нагрузочных транзисторов, вторую информационнук шину, соединенную с затворами второго, четвертого информационных и второго, четвертого нагрузочных транзисторов, третью информационную шину, к которой подключены затворы третьего информационного и третьего нагрузочного транзисторов, шины первого прямого и первого инверсного сигналов управления, к которым подключе:)ы соответственно затворы первого и второго коммутирующих транзисторов,- отличающийся тем, что, с целью расширения функциональных возможностей элемента, между выходной и общей шиной последовательно включены третий, четвертый коммутирующие и шестой информационные транзисторы п-типа, между выходной шиной и шиной источника питания последовательно включены пятый, шестой коммутирующие и шестой нахрузочный транзисторы р-типа, параллельно W второму, пятому нагрузочным и второму, пятому информационным транс зисторам включены соответственно первый, второй р-типа и третий, четвертый п-типа блокирующие транзисторы, истоки седьмого р-типа и восьмого п-типа коммутирующих транзисторов соединены с выходной шиной, а стоки подключены соответственно к истокам четвертого нагрузочного и четвертого информационного транзисо торов, затворы шестого информационсо ного и шестого нагрузочного транзисторов соединены с первой информационной шиной, затворы второго блокирую-, о J щего и пятого коммутирующего транзисторов соединены с шиной первого прямого, сигнала управления, затворы четвертого бгокируквдего и третьего коммутирукядего транзисторов соединены с шиной первого инверсного сигнала управления, затворы первого блокирующего, шестого, восьмого коммутирующих транзисторов соединены с шиной второго прямого сигнала управления, затворы третьего блокирующего, четвертого, седьмого коммутирующих транзисторов соединены с шиной второго инверсного сигнала управления.

.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3900742, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

Авторы

Даты

1984-01-23—Публикация

1982-10-06—Подача