реноса, выход которого является выходом ошибки выходного переноса устройства, выход ошибки полусуммы устройства соединен с выходом сумматора по модулю два контроля полусуммы, вход и группа входов- которого соединены о выходом узла сложения по модулю два и.группой выходов блока формирования полусуммы соответственно, первая и вторая группы входов блока выработки функций -генерации и передачи переноса соединены с входами первого и второго слагаемого устройства соответственно,

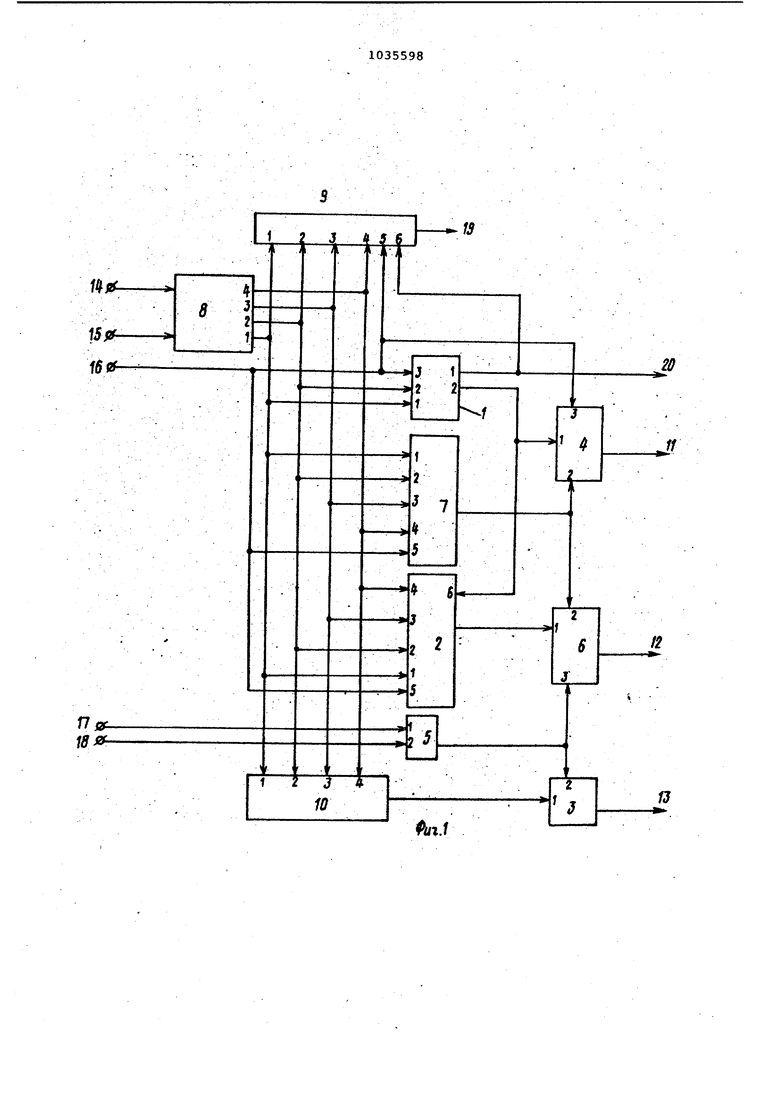

2. Устройство по п. 1, о т, л ичающееся тем, что блок выработки функций генерации и передачи , переноса содержит группу элементов И/ группу элементов И-НЕ, группу элементов ИЛИ, группу элементов ИЛИ-НЕ, причем каждый 1 -и вход (, число разрядов уст ; ройства) первой группы входов блока соединен с первыми входами i -х ментов И, И-НЕ, ИЛИ, ИЛИ-НЕ групп, каждый -) -и вход второй группы входов блока соединен с вторыми входами J(x элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ групп, выходы элементов И группы, выходы элементов ИЛИ группы, выходы элементов И-НЕ группы, выходы элементов ИЛИ-НЕ группы образую соответственно первую, вторую, третью и чет-вертую группы выходов блока.

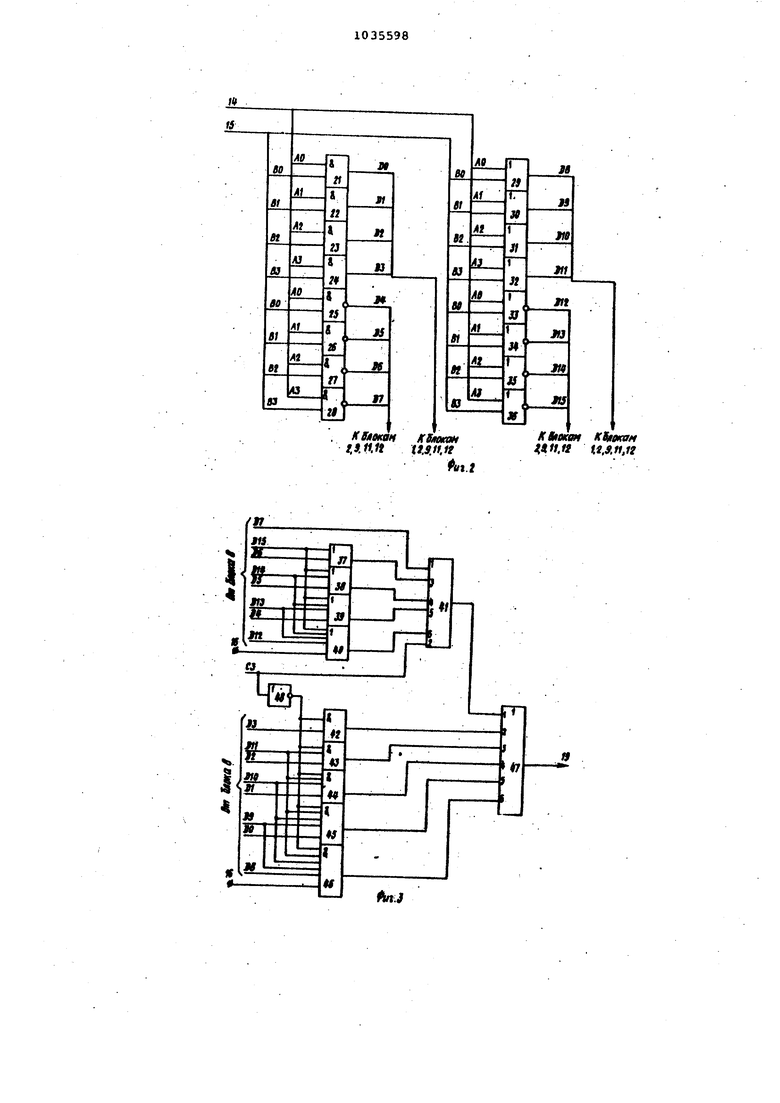

3. Устройство по п. 1, о тл ичающееся тем, что блок контроля выходного переноса содержит группу из Ы элементов ИЛИ, группу из N +1 -элементов И, элемент НЕ, элемент И, элемент ИЛИ, причем каждый 1-и вход первой группы входов блока () соединен с первым входом j-ro элемента И группы, вторые входы всех элементов И группы соединены; с выходом элемента НЕ, каждый i-и : |вход второй группы входов блока соединен с (1+2)-ми входа.ми всех .-х элементов И группы (-i+i J sNT+i), первый вход элемента И и первые входы всех К-х элементов ИЛИ группы (l Ki5V-l) образуют третью группу Входов блока, каждый -й вход четвертой группы входов блока соединен с (i+l)-ми входами всех С-х элементов ИЛИ группы (), вход элемента НЕ И второй вход элемента И соединены с вторым входом блока, первый вход N-ro элемента ИЛИ группы и первый вход (М + 1)-го элемента И группы соединены с. первым входом блока, выходы элементов ИЛИ группы соединены с соответствующими входами элемента И, выходы элементов И группы и вы:ход элемента И соединены с, соответст вующими входами элемента ИЛИ, выход ; которого является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор с контролем по четности | 1983 |

|

SU1124283A1 |

| Параллельный сумматор с контролем по четности | 1982 |

|

SU1121674A1 |

| Устройство для обнаружения и исправления ошибок сумматора | 1982 |

|

SU1038946A1 |

| Параллельный сумматор с контролем по четности | 1984 |

|

SU1187168A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1989 |

|

SU1656526A2 |

| Сумматор с функциональной зависимостью сумм от переносов и с контролем по четности | 1977 |

|

SU767763A1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Параллельный сумматор с контролем по четности | 1977 |

|

SU739535A1 |

| Контролируемый сумматор со сквозным переносом | 1978 |

|

SU767760A1 |

| Устройство для сдвига информации | 1986 |

|

SU1363310A1 |

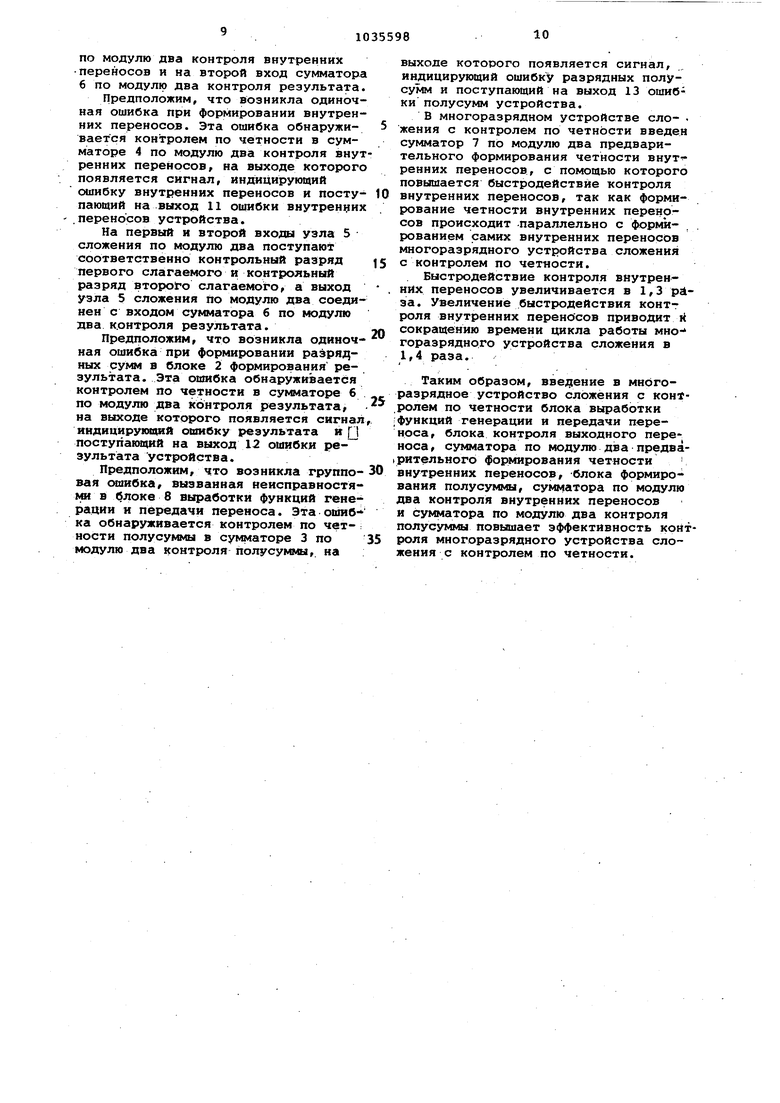

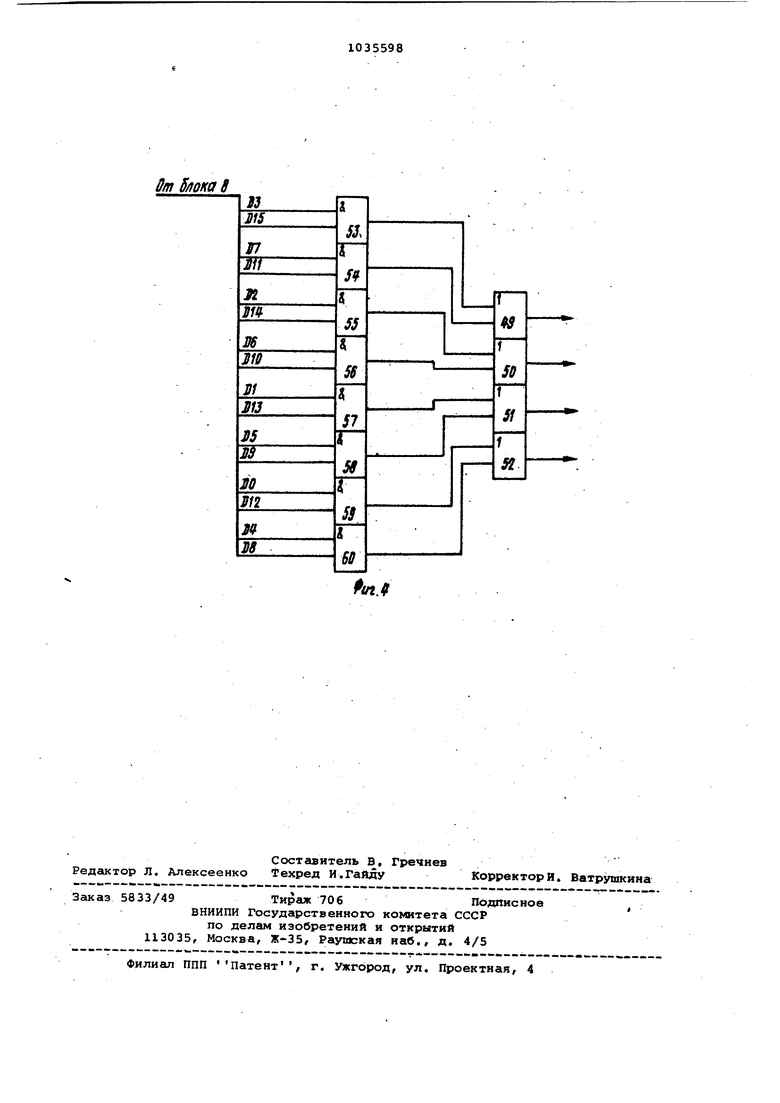

1. МНОГОРАЗРЯДНОЕ УСТРОЙСТ- ВО ДЛЯ СЛОЖЕНИЯ С КОНТРОЛЕМ ПО ЧЕТНОСТИ, содержащее блок предваритель.ного просмотра переноса, блок формирования результата, узел сложения по модулю два, сумматор по модулю два контроля результата, причем входы блока предварительного просмотра пе-г реноса и блока формирования результат та соединены с входом переноса из предыдущего разряда устройства, выход блока предварительного просмотра переноса соединен с выходом переноса, в следующий разряд устройства, группа выходов блока предварительного переноса соединена с первой группой входов блока формирования результата, выходы которого соединены с группой входов сумматора по модулю два контроля результата, первый вход которого соединен с выходом узла сложения по модулю два, первый и второй входы которого соединены соответственно с входами контрольных разрядов первого и второго слагаемых устройства, о тличающееся тем, что, с целью повышения быстродействия устройства к повышения разрешающей способности контроля, в него введены .блок выработки функций генерации и передачи переноса, блок контроля выходного переноса, блок формирования полусумкш, сумматор по модулю два контроля полусуммы, сумматор по модулю два контроля внутренних переносов, сумматор по модулю два предварительного формирования четности внутренних переносов, причем первая и вторая группы выходов блока выработки функций генерации и передачи переноса соединены соответственно с I первыми и вторыми группгми входов блока контроля выходного переноса, блока формирования полусуммы, блока пред|9арительного просмотра переноса и сумматора по модулю два предварительного формирования четности внутренних переносов, третья и Ч€ твертая группы выходов блока выработки функций генерации и передачи переноса соединены соответственно с третьиш и четвертыми группами входов блока . контроля выхоДносчэ переноса,- блока формирования полусуммы и сумматора по модулю два предварительного формирования четности внутренних пере носрв, вторая, третья, четвертая и пятая группы входов блока формирова ния результата соединены с первой,, второй, третьей и четвертой, группамивходов блока формировани.я полусуммы, вход блока предварительного просмот:о сд ел х ра переноса соединен с первыми входа; ми блока контроля выходного переноса сумматора по модулю два контроля . вьутренних переносов и входом сумма-; . тора по модулю два тфедварительногр формирования четности внутренних эо переносов, выход которого соединен с вторыми входами сумматоров по модулю два контроля внутренних-пере носов и контроля результата, выходы которых являются соответственно выходом- ошибки внутреннего переноса и выходом сшибки результата устройства, группа выходов блока предварительного просмотра переноса соединена с группой входов сумматора по модулю два контроля внутренних переносов, выход блока предварительного просмотра-переноса соединен с вторым вхпцом блока контроля выходного пе

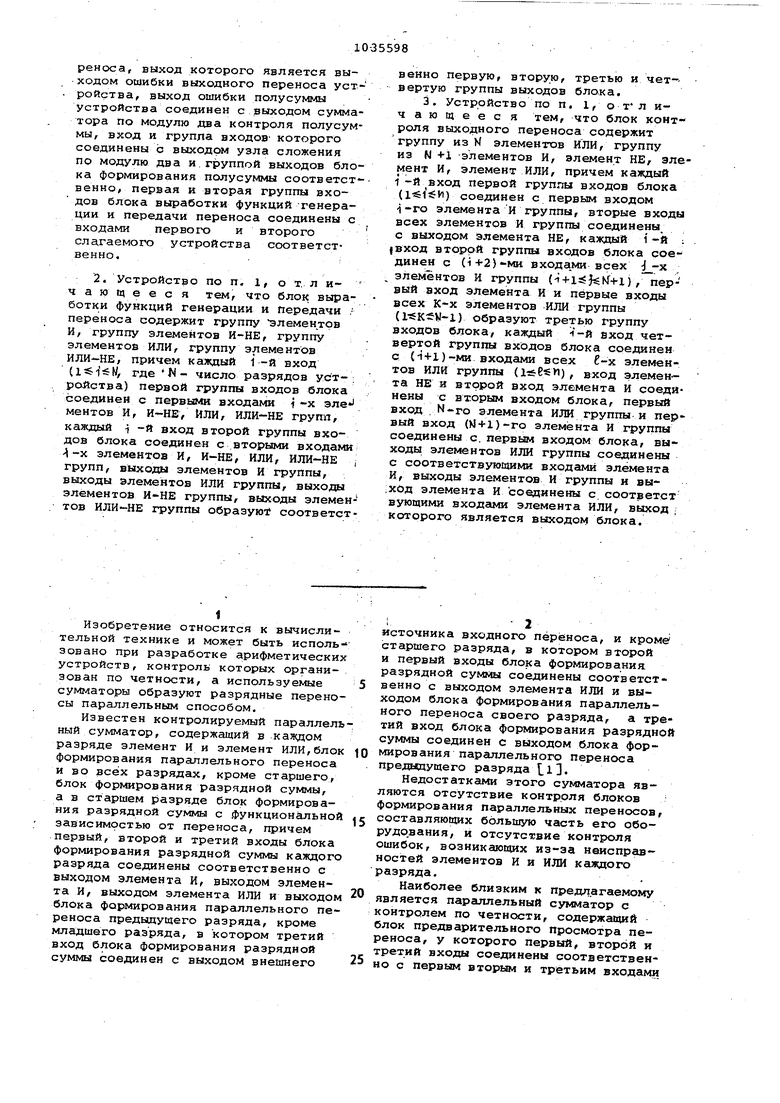

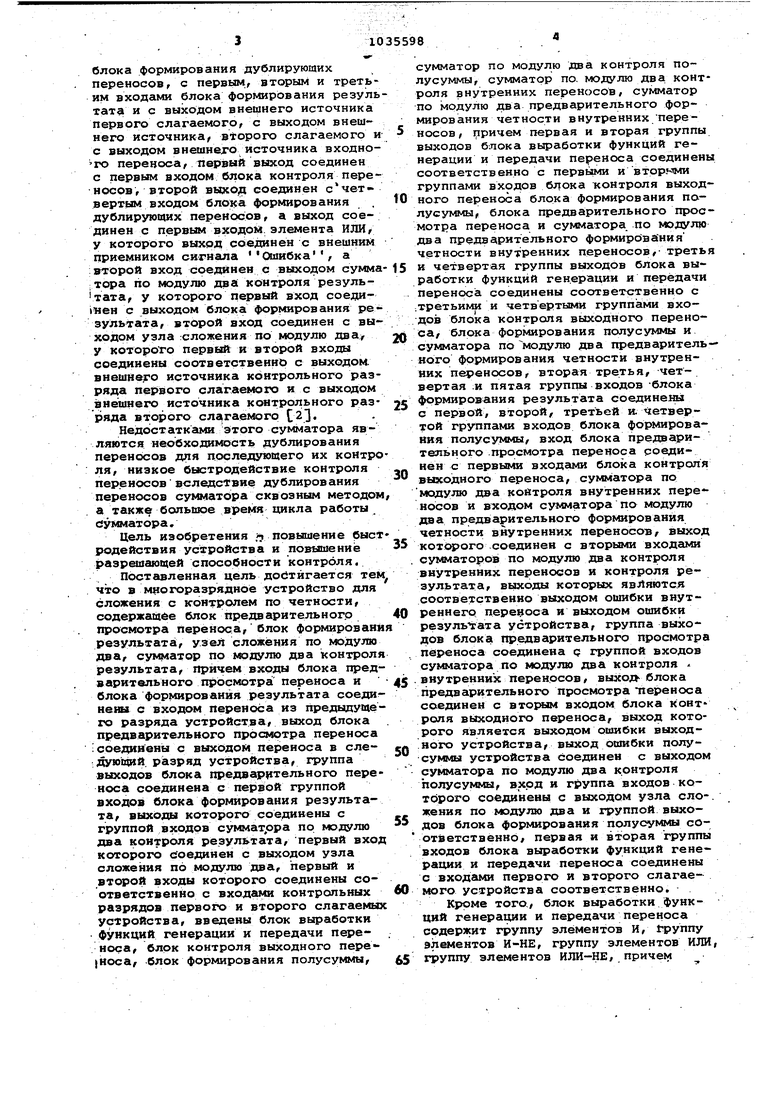

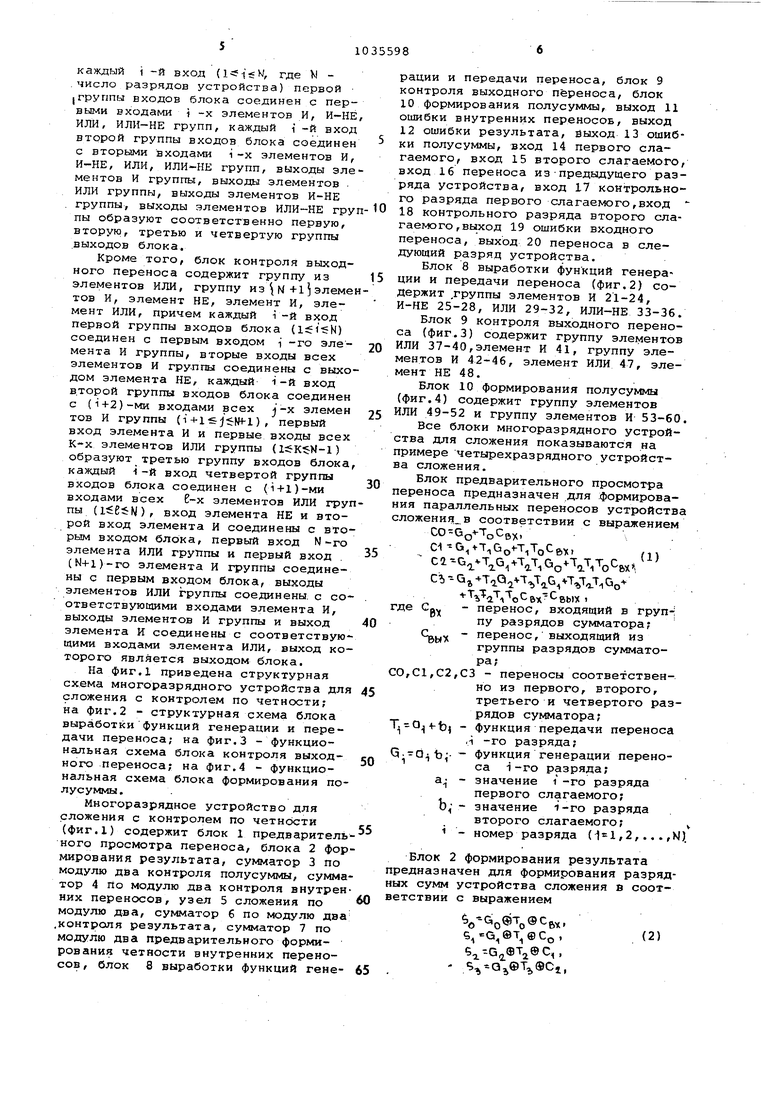

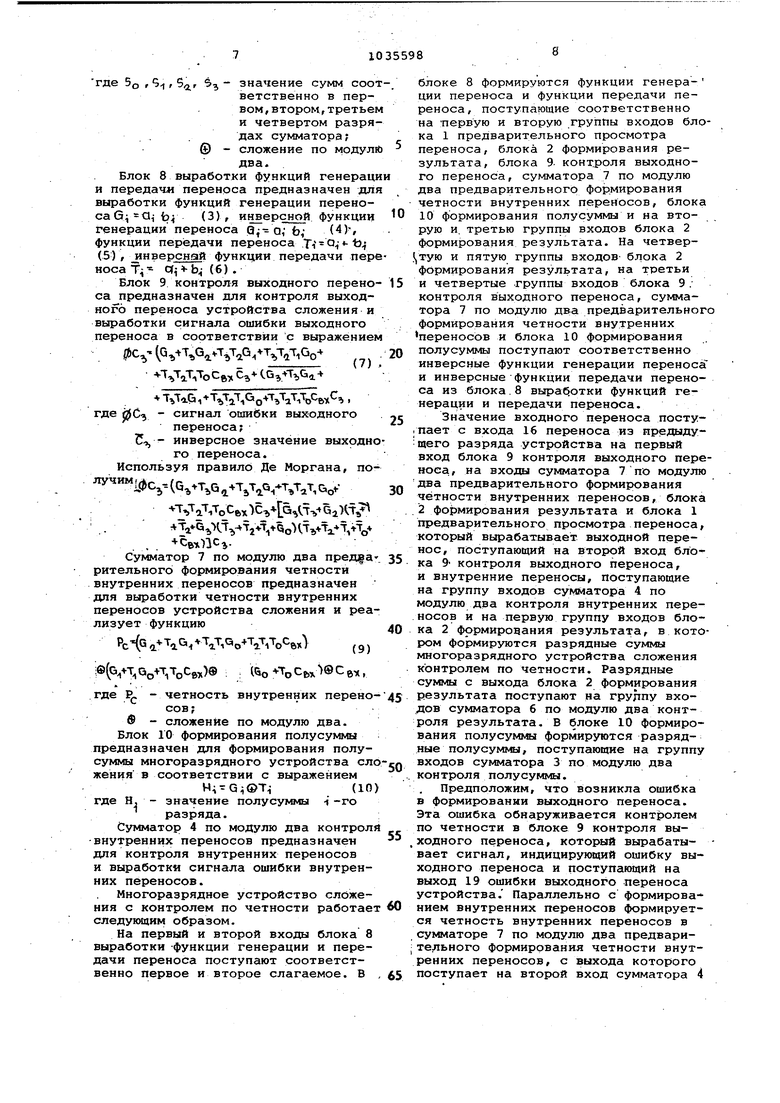

Изобретение относится к вычислительной технике и может быть использовано при разработке арифметических устройств, контроль которых организован по четности, а используемые сумматоры образуют разрядные переносы параллельным способом. Известен контролируемый параллель ный сумматор, содержащий в каждом разряде элемент И и элемент ИЛИ,блок формирования параллельного переноса и во всех разрядах, кроме старшего, блок формирования разрядной суммы, а в старшем разряде блок формирования разрядной суммы с функциональной зависимостью от переноса, причем первый, второй и третий входы блока формирования разрядной суммы каждого разряда соединены соответственно с выходом элемента И, выходом элемента И, выходом элемента ИЛИ и выходом блока формирования параллельного переноса предыдущего разряда, кроме млайшего разряда, в котором третий вход блока формирования разрядной суммы соединен с выходом внешнего источника входного переноса, и кроме старшего разряда, в котором второй и первый входы блока формирования разрядной суммы соединены соответственно с выходом элемента ИЛИ и выходом блока формирования параллельного переноса своего разряда, а третий вход блока формирования разрядной суммы соединен с выходом блока формирования параллельного переноса предыдущего разряда l3. Недостатками этого сумматора являются отсутствие контроля блоков формирования параллельных переносов, составляющих большую часть его оборудования, и отсутствие контроля ошибок, возникающих из-эа неисправностей элементов И и ИЛИ каждого разряда. Наиболее близким к предлагаемому является параллельный сумматор с контролем по четности, содержащий блок предварительного просмотра переноса, у которого первый, второй и третий входы соединены соответственно с первым вторым и третьим входами блока формирования дублирующих переносов, с первым, вторым и треть им входами блока формирования резуль тата и с выходом внешнего источника первого слагаемого, с выходом внешнего источника, второго слагаемого и с выходом внешнего источника входно го переноса/ выход соединен с первым входом блока контроля пере носов, второй выход соединен счетвертым входом блока формирования . дублирующих переносов, а выход соединен с первым входом элемента ИЛИ/ у которого выход соединен с внешним приемником сигнала Ошибка , э второй вход соединен с выходом сумм :тора по модулю два контроля результата, у которого первый вход соедиiDeH с выходом блока формирования ре зультата, второй вход соединен с вы ходом узла гсложения по модулю два/ у которого первый и второй входы соединены соответственно с выходом, внешнего источника контрольного разряда первого слагаемого и с выходом внешнего источника контрольного разряда второго сла гаемого {,2, . Недостатками Этого сумматора яв. ляются необходимость дублирования переносов для доследующего их контро ля/ низкое быстродействие контроля переносов вследс1:вие дублирования переносов сумматора сквозным методом а также большое время цикла работы сумматора. Цель изобретения 7 повышение быст родействия устройства и повышение разрешающей способности контроля. Поставленная цель достигается тем что в многоразрядное устройство для сложения с контролем по четности/ содержащее блок предварительного просмотра переноса/ блок Формировани результата/ узел сложения по модугоо два/ сумматор по юдулю два контроля результата/ причем входы блока щ едварительного просмотра переноса и блока форкшрования результата соеди нены с входом переноса из предыдущего разряда устройства/ выход блока предварительного просмотра переноса :соединены с выходом переноса в еледующий, разряд устройства/ группа выходов блока предварительного пере носа соединена с пергой группой входов блока формирования результата/ выходы которого соединены с группой входов сумматора по модулю два контроля результата/ первый вход которого (Соединен с выходом узла сложения по модулю два, первый и второй входы которого соединены соответственно с входами контрольных разрядов nepBoiTo и второго слагаемых устройства, введены блок выработки функций генерации и передачи пере. носа/ блок контроля выходного пере-|Носа/ блок формирования полусуммы/ сумматор по модулю два контроля полусуммы, сумматор по, юдyлю два контроля внутренних переносов, сумматор по модулю два предварительного формирования четности внутренних переносов, причем первая и вторая группы выходов блока выработки функций генерации и передачи переноса соединены соответственно с первыми и вторыми группами входов блока контроля выходного переноса блока формирования полусуммы, блока предварительного просмотра переноса и сумматора по модулю два предварительного формировании я четности внутренних переносов/- третья и четвертая группы выходов блока выработки функций генерации и передачи перенсзса соединены соответственно с .третьими и четвертыми группами входов блока контроля выходного переноса/ блока формирования полусуммы и сумматора подмодулю два предварительного формирования четности внутренних переносов, вторая третья/ четвертая и пятая группы входов -блока формирования результата соединемл с первой, второй/ третьей и. Четвертой группами входов блока формирования полусуммы/ вход блока предварительного .просмотра переноса соединен с первыми входёши блока контроля выхо)о(ного переноса, сумматора по модулю два контроля внутренних переносов и входом сумматора по модулю два предварительного форкшрованйя четности внутренних переносов/ выход которого -соединен с вторыми входами сумматоров по модулю два контроля внутренних переносов и контроля результата, выходы которых являются соответственно выходом ошибки внутреннего переноса и выходом ошибки резуль ата устройства, группа выходов блока предварительного просмотра Переноса соединена Q группой входов сумматора по модулю два контроля внутренних переносов, выходу блока предварительного просмотра переноса соединен с вторым входом блока конт роля выходного переноса/ выход которого является выходом ошибки выходного устройства/ выход ошибки полусуммы устройства соединен с выходом сумматора по модулю два к.онтроля полусуммы, вход и группа входов которого соединены с выходом узла ело-. жения по модулю два и группой выходов блока формирования полусуммы соответственно/ первая и вторая группы входов блока выработки функций генерации и передачи переноса соединены с входами первого и второго слагаемого устройства соответственно. Кроме того/ блок выработки функций генерации и передачи переноса содержит группу элементов И/ tpynny элементов И-НЕ, группу элементов ИЛИ, группу элементов ИЛИ-НЕ/ причем каждый i -и вход (, где W .число разрядов устройства) первой (Группы входов блока соединен с первыми входами i -X элементов И, И-НЕ ИЛИ, ИЛИ-НЕ групп, каждый i -и вход второй группы входов блока соединен с вторыми входами i-х элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ групп, выходы эле ментов И группы, выходы элементов . ИЛИ группы, выходы элементов И-НЕ . группы, выходы элементов ИЛИ-НЕ гру пы образуют соответственно первую, вторую, третью и четвертую группы .выходов блока. Кроме того, блок контроля выходного переноса содержит группу из элементов ИЛИ, группу из N-И элеме тов И, элемент НЕ, элемент И, элемент ИЛИ, причем каждый i-и вход первой группы входов блока () соединен с первым входом i -го элемента И группы/ вторые входы всех элементов И группы соединены с выхо дом элемента НЕ, каждый 1-й вход в.торой группы входов блока соединен с (1+2)-ми входами всех j-x элемен тов И группы (1+1S ;| -N+-1) , первый вход элемента И и первые входы всех К-х элементов ИЛИ группы {1$К$Ы-1) образуют третью группу входов блока каждый 1 -и вход четвертой группы входов блока соединен с (i+D-MM входами всех Е-х элементов ИЛИ груп пы ()r вход элемента НЕ и второй вход элемента И соединены с вто рым входом блока, первый вход N-го элемента ИЛИ группы и первый вход . (N+i)-ro элемента И группы соединены с первым входом блока, выходы элементов ИЛИ группы соединены, с со ответствующими входами элемента И, выходы элементов И группы и выход элемента И соединены с соответствую щими входами элемента ИЛИ, выход ко торого является выходом блока. На фиг.1 приведена структурная схема многоразрядного устройства дл сложения с контролем по четности; на фиг.2 - структурная схема блока выработки функций генерации и передачи переноса; на фиг.З - функциональная схема блока контроля выходного переноса; на фиг.4 - функциональная схема блока формирования по лусуммы. Многоразрядное устройство для сложения с контролем по четности (фиг.1) содержит блок 1 предваритель ного просмотра переноса, блока 2 фор мирования результата, сумматор 3 по модулю два контроля полусуммы, сумма тор 4 По модулю два контроля внутрен них переносов, узел 5 сложения по модулю два, сумматор б по модулю два .контроля результата, сумматор 7 по модулю два предварительного формирования четности внутренних переносов , блок 8 выработки функций генерации и передачи переноса, блок 9 контроля выходного Переноса, блок 10 формирования полусуммы, выход 11 ошибки внутренних переносов, выход 12 ошибки результата, йыход 13 ошибки полусуммы, вход 14 первого слагаемого, вход 15 второго слагаемого, вход 16 переноса из-предыдущего разряда устройства, вход 17 контрольного разряда первого слагаемого,вход 18 контрольного разряда второго слагаемо го, вьгход 19 ошибки входного переноса, выход 20 переноса в следующий разряд устройства. Блок 8 выработки функций генерации и передачи переноса (фиг.2) содержит .группы элементов И 21-24, И-НЕ 25-28, ИЛИ 29-32, ИЛИ-НЕ 33-36. Блок 9 контроля выходного переноса (фиг.З) содержит группу элементов ИЛИ 37-40,элемент И 41, группу элементов И 42-46, элемент ИЛИ 47, элемент НЕ 48. Блок 10 формирования полусуммы (фиг.4) содержит группу элементов ИЛИ 49-52 и группу элементов И 53-60. Все блоки многоразрядного устройства для сложения показываются на примере четырехразрядного устройства сложения. Блок предварительного просмотра переноса предназначен для .формирования параллельных переносов устройства сложения в соответствии с выражением СО-Оо ТдСеу, . C-l -Ci.tT Go T ToCftx, ,., ca--G - Q,V,, С)--Qj+TaQi T,,TaG,T,,VT,Qo . 1 -перенос, входящий в rpyn-i пу разрядов сумматора; -перенос, выходящий из группы разрядов сумматора;СО,С1,С2,СЗ - переносы соответственно из первого, второго, третьего и четвертого разрядов сумматора; - функция передачи переноса ,-i -го разряда; Q функция генерации перено са i-го разряда; - значение V -го разряда первого слагаемого; - значение 1-го разряда второго слагаемого; у - номер разряда (1 1,2,.. . ,N). Блок 2 формирования результата предназначен для формирования разрядных сумм устройства сложения в соответствии с выражением ,®ri®Co ,, S,,,®Ct, где SQ ,9,5, 3 значение сумм соо ветственно в первом, втором, третье и четвертом разря дах сумматора; © - сложение по модул Блок 8 выработки функций генерац и передачи переноса предназначен дл выработки функций генерации переноса 6 Cli b (3), инверсной функции генерации переноса QJ-Q, Ь,- (4)-, функции передачи переноса Ti (5-) , инверснзй функции передачи пер носа Т (6). Блок 9 контроля выходного перено са предназначен для контроля выходного переноса устройства сложения и выработки сигнала ошибки выходного переноса в соответствии с выражение с,, (Q,,T,Q4a-r,,Q,T ;v4Qo 7) ,,,,T,,T,T,Go4VaV n i . где 0Сз - сигнал ошибки выходного переноса; Coj - инверсное значение выходн го переноса. Используя правило Де Моргана, по (,V,,Q,,C:,oV -цт тдоСвх с-,,о,Тт,е1)т . ... . Сумматор 7 по модулю два предка рительного формирования четности внутренних переносов предназначен для выработки четности внутренних переносов устройства сложения и реа лизует функцию Pc45a fa V-. (9) i®( : , где - четность внутренних перено ® - сложение по модулю два. Блок 10 формирования полусуммы предназначен для формирования полусуммы многоразрядного устройства сл жения в соответствии с выражением (10 где Н, - значение полусуммы i -го разряда. Сумматор 4 по модулю два контрол внутренних переносов предназначен для контроля внутренних переносов и выработки сигнала ошибки внутренних переносов. Многоразрядное устройство сложения с контролем по четности работае следующим образом. На первый и второй входы блока 8 выработки -функции генерации и передачи переноса поступают соответственно первое и второе слагаемое. В блоке 8 формируются функции генерации переноса и функции передачи переноса, поступающие соответственно на первую и вторую группы входов блока 1 предварительного просмотра переноса, блока 2 формирования результата, блока 9 контроля выходного переноса, сумматора 7 по модулю два предварительного формирования четности внутренних переносов, блока 10 формирования полусуммы и на вто- . рую и. третью группы входов блока 2 формирования результата. На четвер|Тую и пятую группы входов- блока 2 формирования результата, на третьи и четвертые группы входов блока 9 ; контроля выходного переноса, сумматора 7 по модулю предварительного формирования четности внутренних переносов и блока 10 формирования полусуммы поступают соответственно инверсные функции генерации переноса и инверсныефункции передачи переноса из блока.8 выработки функций генерации и передачи переноса. Значение входного переноса поступает с входа 16 переноса из предыдущего разряда устройства на первый вход блока 9 контроля выходного переноса, на входил сумматора 7 по модулю два предварительного формирования чётности внутренних переносов, блока 2 формирования результата и блока 1 предварительного просмотра переноса, который вырабатывает выходной перенос, поступающий на второй вход блока 9 контроля выходного переноса, и внутренние переносы, поступающие на группу входов сумматора 4 по модулю два контроля внутренних переносов и на первую группу входов блока 2 формирования результата, в котором формируются разрядные суммы многоразрядного устройства сложения контролем по четности. Разрядные суммы с выхода блока 2 формирования результата поступают на группу входов сумматора 6 по модулю два контроля результата. В блоке 10 формирования полусуммы формируются разрядные полусуммы , поступающие на группу входов сумматора 3 по модулю два контроля полусуммы. Предположим, что возникла ошибка в формировании выходного переноса. Эта ошибка обнаруживается контролем по четности в блоке 9 контроля выходного переноса, который вырабаты- вает сигнал, индицирующий ошибку выходного переноса и поступаниций на выход 19 ошибки выходного переноса устройства. Параллельно с формирова- нием внутренних переносов формируется четность внутренних переносов в сумматоре 7 по модулю два предварительного формирования четности внутренних переносов, с выхода которого поступает на второй вход сумматора 4

по модулю два контроля внутренних переносов и на второй вход сумматора 6 по модулю два контроля результата.

Предположим, что возникла одиночная ошибка при формировании внутренних переносов. Эта ошибка обнаруживается контролем по четности в сумматоре 4 по модулю два контроля внутренних переносов, на выходе которого появляется сигнал, индицирующий ошибку внутренних переносов и поступающий на выход 11 ошибки внутренних .переносов устройства.

На первый и второй входы узла 5 сложения по модулю два поступают соответственно контрольный разряд первого слагаемого и контрольный разряд второго слагаемо1Ро, а выход узла 5 сложения по модулю два соединен с входом сумматора 6 по модулю два контроля результата.

Предположим, что возникла одкночная ошибка при формировании разря;;ных сумм в блоке 2 формирования результата. Эта ошибка обнаруживается контролем по четности в сумматоре 6 по модулю два контроля результата, на выходе которого появляется сигнал иидицирующий ошибку результата и f поступающий на выход 12 ошибки результата устройства.

Предположим, что возникла групповая сшибка, вызванная неисправностяhei в блоке 8 выработки функций генерации и передачи переноса. Эта ошиб- ка обнаруживается контролем по четности полусуммы в сумматоре 3 по модулю два контроля полусуммы, на

выходе которого появляется сигнал, индицирующий ошибку разрядных полусумм и поступающий на выход 13 ошибки полусумм устройства.

В многоразрядном устройстве ело- . жения с контролем по четности введен сумматор 7 по модулю два предварительного формирования четности внут ренних переносов, с помощью которого повышается быстродействие контроля внутренних переносов, так как формирование четности внутренних переносов происходит .параллельно с формированием самих внутренних переносов многоразрядного устройства сложения с контролем по четности.

Быстродействие контроля внутренних переносов увеличивается в 1,3 рА за. Увеличение быстродействия контг роля внутренних переносов приводит и сокращению времени цикла работы многоразрядного устройства сложения в 1,4 раза.

Таким образом, введ{ение в многоразрядное устройство сложения с контролем по четности блока выработки ; функций генерации и передачи переноса, блока контроля выходного переноса, сумматора по модулю д:в а пред в а|рительного формирования четности внутренних переносов, блока формирования полусуммы, сумматора по модулю два контроля внутренних переносов и сумматора по модулю два контроля полусуммы повышает эффективность конроля многоразрядного устройства сложения с контролем по четности.

Вт 5/1 ока 8

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Контролируемый параллельный сумматор | 1977 |

|

SU703817A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| М., Мир, 1972 | |||

| Устройство для разметки подлежащих сортированию и резанию лесных материалов | 1922 |

|

SU123A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1983-08-15—Публикация

1981-09-07—Подача