разрядов второго слагаемого сумматора, выходы элементов И-НЕ группы и элементов ИЛИ-НЕ группы, выход блока формирования функций переноса и вход переноса сумматора соединены с соответствующими входами соответствующих элементов И группы, выходы первого и второго элементов ИЛИ, выход сумматора по модулю два четности слагаемых и выход блока формирования разряных сумм соединены с соответствующими входами сумматора по модулю два контроля результата, выход которого .является выходом опмбки разрядных сумм сумматора, первьй и второй входы сумматора по модулю два четности слагаемых являются соответственно вдами, контрольных разрядов первого и второго слагаемых, выход блока формирования функций переноса соединен с первой группой входов блока сравнения, выход .которого является выходом ошибки функций переноса сумматора, выходы элементов И-НЕ группы и элементов ИЛИ-ИЕ группы соединены с второй группой входов блока сравнения, выходы элементов ИЛИ-НЕ группы соединены с группой входов блока формирования разрядных полусумм.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядное устройство для сложения с контролем по четности | 1981 |

|

SU1035598A1 |

| Параллельный сумматор с контролем по четности | 1982 |

|

SU1121674A1 |

| Параллельный сумматор с контролем по четности | 1984 |

|

SU1187168A1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Сумматор с функциональной зависимостью сумм от переносов и с контролем по четности | 1977 |

|

SU767763A1 |

| Параллельный сумматор с контролем по четности | 1977 |

|

SU739535A1 |

| Устройство для обнаружения и исправления ошибок сумматора | 1982 |

|

SU1038946A1 |

| Контролируемый сумматор с групповым переносом | 1977 |

|

SU684545A1 |

| Устройство для умножения | 1986 |

|

SU1368882A1 |

| Параллельный сумматор с контролем по честности | 1977 |

|

SU691856A1 |

ПАРАЛЛЕЛЬНЫЙ СУММАТОР С КОНТРОДЕМ ПО ЧЕТНОСТИ, содержаний блок формирования функций переноса, блок формирования параллельных переносов, блок формирования разрядных полусумм, блок формирования разрядных сумм, блок формирования дублирующего выходного переноса и сумматор по модулю Два контроля выходного переноса, причем входы первого и второго слагаемых блока формирования функций переноса являются соответственно входами первого и второго слагаемых сумматора, выход блока формирования функций переноса соединен с входом блока формирования разрядных полусумм и первыми входами блока формирования параллельных переносов и блока формирования дублирующего выходного переноса, выход которого соединен с первым входом сумматора по модулю два контроля выходного переноса, выход которого явля,ется выходом ошибки выходного переноса сумматора, вторые входы блока формирования параллельных переносов, блока формирования дублируницего выходного переноса и первый вход блока формирования разрядных сумм объединены и являются входом переноса сумматора, выход переноса старшего разряда блока формирования параллельных переносов соединен с вторым входом сумматора по модулю два контроля выЬсодного переноса и является выходом переноса сзмматора, второй и третий входы блока формирования разрядных сумм соединены соответственно с выходом переносов младших разрядов блока формирования параллельных переН носов и выходом блока формирования рязрядных полусумм, выход блока формирования разрядных сумм является выходом результата сумматора, о т личающийся тем, что, с цельно (Л повышения быстродействия и полноты С контроля, в него введены блок срабнения, сумматор по модулю два четности слагаемых, сумматор по модулю два контроля результата, блок формирования инверсных функций переноса, содержащий группу элементов И-НЕ и группу элементов ИЛИ-НЕ, и блок ; формирования четности переносов, содержащий группу элементов И и два элемента ИПИ, причем выходы элементов И с первого по седьмой группы соединены с входами первого элемента ШШ, выходы элементов И с восьмого по одиннадцатый группы соединены с входами второго элемента ШШ, пер- вые входы одноименных элементов И-НЕ группы и элементов ШШ-НЕ группы объединены и соединены с входами соответствующих разрядов первого слагаемого сумматора, вторые входы одноименных элементов И-НЕ группы и элементов ИЛИ-НЕ группы объединены и соединены с входами соответствующих

Изобретение относится к вычислительной технике и может бьп-ь использовано для построения арифметических устройств, в которых контроль организован по четности, а используемые сумматоры формируют разрядные I переносы параллельным способом.

Известен параллельный сумматор, с -держащий в каждом разряде блок фор1№рования параллельного переноса, блок формирования разрядной суммы с функционадьной зависимостью от переносов, блок формирования дублирующего переноса и блок сравнения, первьш вход которого соединен с выходом блока формирования дублирующего переноса, вход которого соединен с выходом блока формирования параллельного переноса предьщущего разряда и с вторым входом блока формирования разрядной суммы с функциональной зависимостью от переносов, первый вход которого соединен с выходом-блока формирования параллельного переноса данного разряда и со вторым входом блока сравнения, выход которого соединен со входом внешнего приемника сигнала Ошибка

Недостатком данного сумматора является низкое быстродействие вследствие необходимости формирования дублирующих переносов сквозным методом.

Наиболее близким техническим решением к предлагаемому является параллельный сумматор, содержащий блок формирования функций генерации и передачи переноса, блок формирования параллельных переносов, блок формирования разрядньк полусумм, блок формирования разрядных сумм, блок, формирования дублирующего выходного переноса, блок ускоренного формирования четности разрядных сумм, блок формирования четности результата, первый второй и третий сумматоры по модулю два и элемент ИЛИ, выход которого соединен с выходом ошибки сумматора, а первый, второй и третий входы которого соединены с выходами соответствукицих сумматоров по модулю два, первый и второй входы первого сумматора по модулю два соединены соответственно со вторым выходом блока

формирования параллельных переносов и с выходом блока формирования дублирующего вькодного переноса, первый вход второго сумматора по модулю два соединен с выходом блока формирования разрядных полусумм, а второй и третий входы второго сумматора по модулю два соединены соответственно с первым входом блока ускоренного формирования четности разрядных сумм,

выходом внешнего источника четности первого слагаемого и с вторым входом блока ускоренного формирования четности разрядньк сумм и выходом внешнего источника четности второго слагаемого, первый и второй входы третьего сумматорапо модулю два соедийены соответственно с выходом блока формирования четности результата и р выходом блока ускоренного формироЁдния четности разрядных сумм, трети вход которого соединен с вторым входом блока формирования дублирующего вьпсодного переноса, с выходом блока формирования функций генерации и передачи переноса и с первым входом блока форьшрования параллельных nepe носов, а четвертый .вход которого соединен с выходом блока формирования разрядных полусумм, пятый вход блока ускоренного формирования четности разрядных су№1 соединен со. вторым входом блока формирования параллельных переносов, со вторым входом блока формирования разрядных сум с первым входом блока формирования дублирующего выходногр переноса и с выходом внешнего источника входного переноса, первый и второй входы блока формирования функций генерации и передачи переноса соединены соответственно с первым и вторым входаю блока формирования разрядных полусумм, с третьим и четвертым входами блока форми рования разрядных сумм и с входом первого слагаемого сумматора и с входом второго слагаемого сумматора, выход блока формирования разрядных сумм соединен со входом блока формирования четности результата и с выходом результата сумматора 2 3.

Недостатками данного сумматора являются низкое быстродействие блока ускоренного формирования четности разрядных сумм вследствие необходимости формирования разрядных полусум большой временной цикл работы вслея ствие более позднего формирования четности разрядных сумм по сравнению с формированием самих разрядных сумм; недостаточная полнота контроля из-за невозможности обнаружения всех типов опибок, возникакяцих в блоке формирования функций генерации и передачи переноса.

Цель изобретения - повышение быст родействия и полноты контроля.

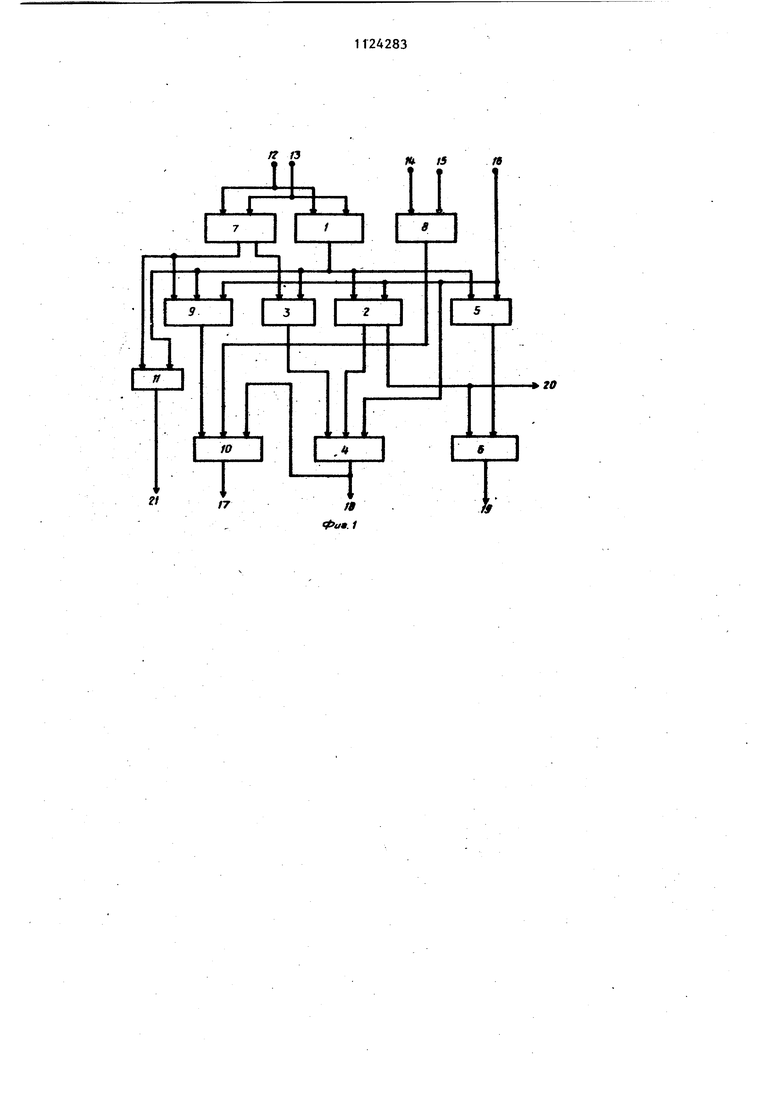

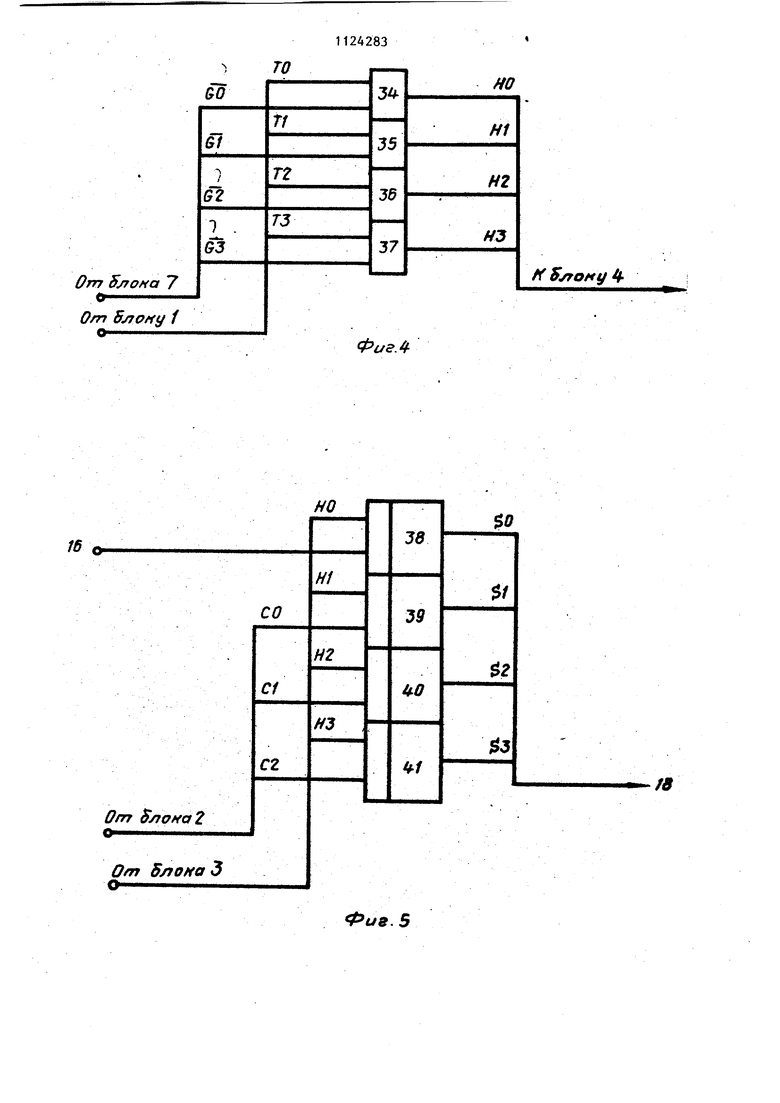

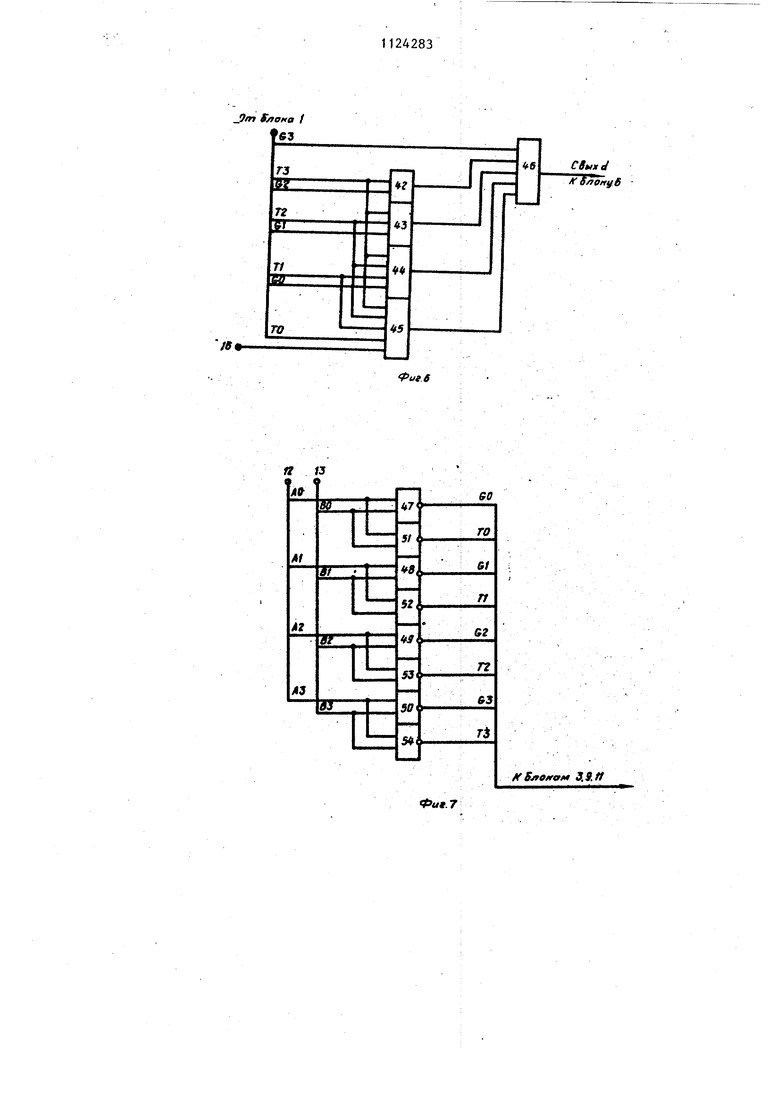

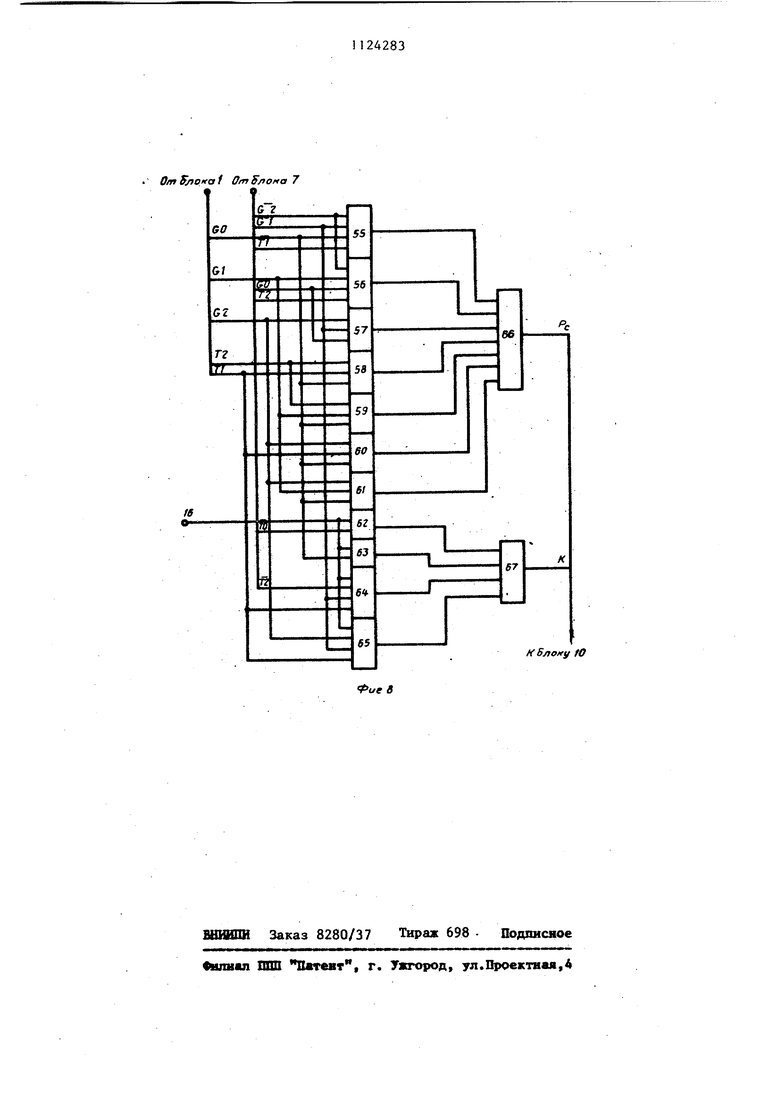

Поставленная цель достигается тем что в параллельный сумматор с контролем по четности, содержащий блок фор1 1ирова1шя функций переноса, блок формирования параллельных переносов, блок формирования разрядных полусумм блок формирования разрядных сумм блок формирования дублирующего выходного переноса и сумматор по модулю два контроля выходного переноса, причем входы первого и второго слагаемых блока формирования функций переноса являются соответственно входами первого и второго слагаемых сумматора, выход блока формирования функций йереноса соединен со входом блока формирования разрядных полусумм и первыми входами блока формирова1шя праллельных переносов и блока формирования дублирующего выходного переноса, выход которого соединен с первым входом сумматора по модулю два контроля выходного переноса, выход которого является выходом ошибки выходного переноса сзгмматора, вторые входы блока формирования параллельных переносов, блока формирования дублирующего выходного переноса и первый вход блока формировани разрядных сумм объединены и являются входом переноса сумматора, выход переноса старшего разряда блока формирования параллельных переносов соединен со вторым входом сумматора по. модулю два контроля выходного переноса и является выходом переноса сут матора, второй и третий входы блока формирования разрядных сумм соединены соответственно с выходом переносов мпадогах разрядов блока формирования параллельных переносов и выходом блока формирования разрядных полусумм, выход блока формирования разрядных сумм является выходом результата сумматора, введены блок сравнения, сумматор по модулю два четности слагаемых, сумматор по мсдулю два контроля результата, блок формирования инверсных функций переноса, содержащий группу элементов И-НЕ и группу элементов ИЛИ-НЕ, и блок фор-i мирования четности переносов, содержа1ций группу элементов И и два элемента ИЛИ,причем выходы элементов И с первого по седьмой группы соединены со входами первого элемента ИЛИ, выходы элементов И с восьмого по одиннадцатый группы соединены со входами второго элемента ИЛИ, первые входы одноименных элементов И-НЕ группы и элементов ИЛИ-НЕ группы объединены и соединены со входами соответствующих разрядов первого слагаемого сзгнматора, вторые входы спнсяменнсАс элементов И-НЕ группы и элементов ИЛИ-НЕ группы 511 объединены и соединены со входами роответствукнцих разрядов второго Слагаемого сумматора, выходы элементов И-НЕ группы и элементов ИЛИ-НЕ Группы, выход блока формирования функций переноса и вход переноса сумkaTopa соединены с соответствующими )входами соответствукщих элементов И группы,выходы первого и второго Элементов ИЛИ, выход сумматора по модулю два четности слагаемых и выход блока формирования разрядных Ьумм соединены с соответствующими вxoдa ш сумматора по модулю два контроля результата, выход которого яв яется выходом ошибки разрядных сумматора, первый и второй входы cyjiii матора по модулю два четности слагаемых являются соответственно входами контрольных разрядов первого и вто рого слагаемых, выход блока формирования функций переноса соединен с первой группой входов блока сравнения, выход которого является выходом ошибки функций переноса сумматора, выход элементов И-НЕ группы и элемен тов ИПИ-НЕ группы соединены со второй группой входов блока сравнения, выходы элементов ИЛИ-НЕ группы соединены с группой входов блока фор мирования разрядных полусумм. На фиг. 1 приведена функциональная схема параллельного сумматора с конт ролем по четности; на фиг. 2 - то же блока формирования функций переноса на фиг. 3 - то же, третьего разряда блока формирования параллельных пеpeHocoBj на фиг. А - то же, блока ф мирования разрядных попусумм} на фиг. 5 - то же, блока формирования разрядных сумм; на фиг. 6 - то же, блока формирования дублирующего вых ного переноса; на фиг. 7 - то же, блока формирования инверсных функци переноса; на фиг. 8 - то же, блока формирования четности переносов. Параллельный сумматор с контроле по четности (фиг. 1) содержит блок 1 формирования функций переноса, блок 2 формирования параллельных переносов, блок 3 формирования разрядных полусумм, блок 4 формировани разрядных сумм, блок 5 формирования дублирукяцего выходного переноса, сумматор 6 по модулю два контроля выходного переноса, блок 7 формирования инверсных функций переноса, сумматор 8 по модулю два четности слагаемых, блок 9 формирования четности переносов, сумматор 10 по модулю, два контроля результата, блок 11 сравнения,входы 12 и 13 первого и второго слагаемых сумматора, входы 14, 15 контрольных разрядов первого и второго слагаемых сумматора, вход 16 переноса сумматора, выход 17 ошибки разрядных сумм сумматора, выход 18 результата-сумматора, выход 19 ошибки выходного переноса сумматора, выход 20 переноса сумматора, вькод 21 ошибки функций переноса сумматора. Блок 1 формирования функций переноса (фиг. 2) содержит элементы И 22-25, выходы которых обозначены соответственно ВО G3, и элементы ИЛИ 26-29, вьсходы которых обозначены соответственно ТО-ТЗ . Блок 2 формирования параллельных ереносов (фиг. 3) содержит в каждом разряде узел формирования переноса, которые аналогичны между собой, и указан на примере узла формирования переноса из третьего разряда, который содержит элементы И 30-32 и элемент ИЛИ 33, выход которого обозначен Со . Блок 3 формирования разрядных полусумм (фиг. 4) содержит элементы И 34-37, выходы которых обозначены соответственно НО-НЗ. Блок 4 формирования разрядных сумм (фиг. 5) содержит двухвходовые сумматоры 38-41 по модулю два, выходы которых обозначены соответственно 50-53.. Блок 5 формирования дублирующего выходного переноса, (фиг. 6) содержит элементы И 42-45 и элемент ИЛИ 46, выход которого обозначен С вых. с . Блок 7 формирования инверсных функций переноса (фиг. 7) содержит группу элементов И-НЕ 47-50, выходы которых обозначены соответственно GO-G3 и группу элементов ИЛИ-НЕ 51-54, выходы которых обозначены соответственно ТО-ТЗ. Блок 9 формирования четности переносов (фиг. 8) содержит группу элементов И 55-65 и элементы ИЛИ 66, 67, выходь которых обозначены соответствённо Pj. и К, Выход сумматора 6 по модулю два контроля выходного переноса соединен с выходом 19 ошибки выходного переноса сумматора, а первый вход сумматора 6 по модулю два контроля выходного переноса соединен с выходом блока 5 формирования дублирующег выходного переноса, второй вход кото рого соединен со входом 16 переноса сумматора, с первьб4 входом блока 4 формирования разрядных сумм, со вторым входом блока 2 формирования параллельных переносов и с третьим входом блока 9 формирования четности переносов, второй вход которого соединен с вторым входом блока 3 фор мирования разрядных полусумм, с вторым входом блока 11 сравнения, с выходом блока 7 формирования инверсных функций переноса, входы первого и второго слагаемых которого соединены соответственно с входами 12, 13 первого и второго слагаемых сз мматора и с соответствующими входами первого и второго cлaгae в к блока 1 формирования функций переноса, выход которого соединен с первыми входами блока 11 сравнения, блока 3 формирования разрядных полусумм, 9 формирования четности переносов, бло ка 5 формирования дублирующего выходного переноса и блока 2 формирова ния параллельных переносов, выход пе LeHoca старшего разряда которого яв; ляется выходом 20 переноса сумматора и соединен со вторым входом сумматора 6 по модулю два контроля выходного переноса, вькод переноса младших разрядов которого соединен с вторым входом блока 4 формирования разрядных сумм, вькод сумматора 10 по модулю два контроля результата яв ляется выходом 17 ошибки разрядных сумм сумматора, а первый вход сумматора 10 по модулю два контроля резул тата соеда нен с выходом блока 9 фор 1« рования четности переносов, второй вход сумматора 10 по модулю два конт роля результата соединен с выходом сумматора 8 по модулю два четности слагаемых,первый и второй входы ко-, торого являются соответственно входами 14, 15 контрольных разрядов первого и второго слагаемых сумматор выход блока 3 формирования разрядных полусумм соединен с третьим входом блока 4 формирования разрядных сумм, выход которого является выходом результата сумматора и соединен с третьим входом сумматора 10 -контрапя по модулю два результата, а выход блока 11 сравнения является выходом 17 ошибки функций переноса сумматора. Параллельный сумматор с контролем по чётности работает следукицим образом. На входа первого и ВТОРОГО спагае мых блока 1 формирования функций переноса и входы элементов И-НЕ и ИЛИ-ЙЕ групп блока 7 формирования инверсных функций переноса поступают первое и второе слагаемые, на первый и второй входы сумматора 8 по модулю два четности слагаемых поступают соответ ственно контрольные разряды первого и второго слагаемых, В указанных выIше блоках формируются соответственно функции генерации и передачи переноса, которые поступают на соответствукнцие входы блока 11 сравнения, блока 2 форьшрования параллельных переносов, блока 3 формирования разряд ных полусумм, блока 5 формирования дублирукяцего выходного переноса и блока 9 формирования четности переносов, инверсные функции генерации и передачи переноса, которые поступают на соответствукицие входы блока 11 сравнения, блока 3 формирования разрядных полусумм и блока 9 формирования разрядных полусумм и блока 9 формирования четности переносов, и суммарная четность слагаеьв 1х, которая поступает на соответствующие входы сумматора 10 по модулю два контроля результата. С приходом переноса С9 входа 16 переноса сумматора на соот ветствующие входы блока 2 формирования параллельных переносов, блока 5 формирования дублирующего выходного переноса и блока 9 формирования четности переносов в указанных блоках формируются соответственно выходной перенос, поступакяцкй на второй в вход сумматора 6 по модулю два контроля выходного переноса и на выход 20 переноса сумматора к параллельные переносы, которые поступают на соответствуюпр1й вход блока 4 формирования разрядных сумм, дублирующий выходной перенос, поступанщий на первый вход сумматора 6 по модулю два контроля выходного переноса, и четность переносов с коррекцией четности переносов, поступаюпр1е на соответствующие входы сумматора 10 по модулю два контроля результата. Параллельно с этим в блоке 3 формировав ния разрядных полусумм формируются разрядные nonycyMNe i, которые постуЬают на соответствующий вход блока 4 форми{ ования разрядных сумм. При Поступлении разрядных полусз мм, вход horo переноса и параллельных переносов на соответствующие входы блока 4 формирования разрядных сумм в последнем формируются разрядные суммы, которые поступают на выход 18 резуль тата сумматора и на соответствующий вход сумматора 10 по модулю два конт роля результата. ; Предполо жим, что произошла ошибка в i -разряде блока 2 формирования параллельных переносов. Тогда эта ошибка вызовет ошибку в (i+1)-M разряде блока 4 формирования разрядйых , что приведет к нечетному Числу ошибок в разрядах суммы. Тогда эта ошибка будет обнаружена контролем по четности в сумматоре 10 по модулю два контроля результата и появится сигнал на выходе 17 ошибки разрядных сумм сумматора. Предположим, что возникла опшбка в формировании переноса старшего раз ряда (выходного переноса) в блоке 2 формирования параллельных переносов. Тогда эта ошибка будет обнаружена контролем по четности в сумматоре 6 по модулю два контроля выходного переноса, который формирует сигнал на выходе 19 ошибки выходного переноса сумматора. Предположим, что возникла ошибка fe -м разряде блрка 3 формирования разрядньи полусумм. Тогда эта ошибка вызовет ошибку в I-M разряде блока 4 формирования разрядных сумм, что приведет к нечетному числу ошибок в разрядах iсуммы. В этом случае указанная ошибка будет обнаружена контролем по четности в сумматоре 10, коЬорый сформирует сигнал на выходе Ш ошибки разрядных сумм сумматора. В случае возникновения ошибки в Л-м разряде непосредственно самого блока 4 формирования разрядных сумм данная ошибка будет обнаружена в сумматоре 10 аналогично. Предположим, что произошла ошибка в блоке 1 формирования функций переноса. Тогда эта ошибка будет обнаружена контролем по четности в блоке 11 сравнения, который сформирует сигнал на вьрсоде 21 ошибки функций генерации и передачи переноса сумматора. В предложенном сумматоре удалось увеличить бьютродействие параллельного сумматора. Полнота контроля в предложенном сумматоре обеспечивается за счет того, что все основные блоки параллельного сумматора (блок формирования функций переноса, блок формирования параллельных переносов, блок формирования разрядных полусумм и блок формирования разрядных сумм) охвачены контролем по четности.

/ /3

г

f7

/9 Фа. 1

т. ts

/j/f

От 5/7 ока 1 Gt

Фиг. 2

тг

G1

Т1

2Г

Фиг.Ъ

ФигЛ

Фиг. 5

/n Каона /

вз

rj

SOL

CltixJ

Its

ff SaontfB

От S/fOta 1 От Б/юна 7

GO

гг

LL

16

О-

66

67

К Влоку Ю

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Параллельный сумматор | 1976 |

|

SU643871A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| М., №ip, 1972, с | |||

| Реверсивный дисковый культиватор для тросовой тяги | 1923 |

|

SU130A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-13—Подача