два, причем первые выходы первого, второго, третьего, четвертого, пятого и шестого элементов И группы объединены и подключены к выходу блока элементов И, первые входы седьмого, восьмого, тринадцатого и четырнадцатого элементов И группы объединены и подключены к выходу; блока элементов И-НЕ, первые входы девятого, десятого, одиннадцатого и двенадцатого элеметов И группы объединены и соединены с выходом блока элементов ИЛИ-НЕ, вторые входы первого, четвертого, девятого и тринадцатого элементов И группы объединены и соединены с выходами блока элементов И-НЕ, вторые входы второго шестого, десятбго, одиннадцатого и двенадцатого элементов И группы объединены и подключены к выходу блока элементов И, вторые входы третьего, пятого и четырнадцатого элементов И группы объединены и подключены к выходу блока элементов ИПИ-НЕ, вторые входы седьмого и восьмого элементов И группы объединены и соединены с выходом блока элементов ИЛИ, третьи входы первого и девятого эле-: ментов И группы объединены и подключены к выходу блока элементов ИЛИ, третьи входы второго, третьего, седь мого, двенадцатого и четырнадцатого элементов И,группы объединены и подключены к выходу блока элементов И, третьи входы четвертого, пятого, десятого и одиннадцатого элементов И группы объединены и подключены к выходу блока элементов И-НЕ, третьи входы шестого,, восьмого и тринадцатого элементов И группы объединены и подключены к выходу блока элементов ИЛИ-НЕ, четвертые входы первого.

второго, четвертого, седьмого, одиннадцатого и четырнадцатого элементов И группы объединены и подключены к выходу блока контроля выходного переноса, четвертые входы третьего, шестого, восьмого, девятого, двенадцатого и тринадцатого элементо И группы объединены и подключены к входу переноса сумматора, четвертые входы пятого и десятого элементов И группы объединены и подключены к выходу блока элементов ИЛИ, выходы элементов И группы соединены с соответствующими входами элементов ИЛИ, выг ход которого соединен с первым входом сумматора по модулю два блока предварительного формирования четности разрядных сумм, второй итретий входы которого являются соответственно входами контрольных разрядов первого и второго слагаемых блока предварительного формирования четности разрядных сумм, выход сумматора по модулю два является выходом блока, первые входы блоков элементов И-НЕ, ИЛИ-НЕ подключены к входу первого слагаемого параллельного сумматора, выход блока элементов И-НЕ соединен с входом генерации переносов блока контроля по,четности выходного переноса, вторые входы блоков элементов И-НЕ и ИЛИ-НЕ подключены к входу второго слагаемого параллельного сумматора, выход блока элементов ШШ-НЕ соединен с входом передачи переносов блока контроля ijo четности выходного переноса, выход инверсного значения выходного переноса которого соединен с четвертым BixorfbM одиннадцатого элемента И группы блока предварительного формирования четности разрядных сумм.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор с контролем по четности | 1983 |

|

SU1124283A1 |

| Параллельный сумматор с контролем по четности | 1982 |

|

SU1121674A1 |

| Многоразрядное устройство для сложения с контролем по четности | 1981 |

|

SU1035598A1 |

| Устройство для обнаружения и исправления ошибок сумматора | 1982 |

|

SU1038946A1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1989 |

|

SU1656526A2 |

| Сумматор с функциональной зависимостью сумм от переносов и с контролем по четности | 1977 |

|

SU767763A1 |

| Устройство для хранения информации с контролем | 1989 |

|

SU1691897A1 |

| Контролируемое устройство для двоично-десятичного суммирования | 1984 |

|

SU1196874A1 |

| Параллельный сумматор с контролем по четности | 1977 |

|

SU739535A1 |

ПАРАЛЛЕЛЬНЫЙ СУММАТОР С КОНТРОЛЕМ ПО ЧЕТНОСТИ, содержащий блок элементов И, блок элементов ИЖ, блок формирования параллельных переносов, блок формирования разрядных сумм, блок контроля по четности выходного переноса, блок предварительного формирования четности разрядных сумм и сумматор по модулю два, причем первые входы блоков элементов И и ИЛИ и блока формирования разрядных . сзгмм объединены и являются входом первого слагаемого параллельного сумматора, вторые входы блоков элементов И и ИЛИ и блока формирования разрядных сумм объединены и являются входом второго слагаемого параллельного сумматора, выходы блоков элементов И и ИЛИ соединены соответственно с входами генерации переноса и передачи переноса блока формирования параллельных переносов и с входами генерации переноса и передачи переноса блока контроля вы ходного переноса, входы переноса блока формирования параллельных переносов, блока формирования разрядных сумм, блсцка контроля по четности выходного переноса и блока предварительного формирования четности разрядных сумм объединены и являются входом переноса параллельного сумматора, выход разрядных переносов блока формирования параллельных переносов соединен с третьим входом блока формирования разрядных сумм, выход переноса из старшего разряда блока формирования параллельных переносов соединен с входом переноса из старшего разряда блока контроля по четности выходного переноса и явля- ется выходом переноса параллельного сумматора, выход блока формирования S разрядных сумм является выходом результата параллельного сумматора (/} и соединен с первым входом сумматора; по модулю два, выход которого является выходом ошибки результата па- раллеш ного сумматора, второй вход Сс: которого соединен с в гходом блока предварительного формирования четности разрядных сумм, входа контроль00 ных разрядов первогоj второго слага емых которого соединёны. с соответствующими входами параллельного 5N 00 сумматора, а выход ошибки выходного переноса блока контроля по четности выходного переноса является выходом ошибки выходного переноса параллельного сумматора, о .тли чающийся тем, что, с целью повьш1ения быстродействия и уменьшения количества оборудования параллельного сумматора, в него введены блок элементов И-НЕ и блок элементов ИЛИ-НЕ, а блок предварительного формирования четности разрядных сумм содержит группу элементов И, элемент ИЛИ и сумматор по модулю

1

Изобретение откосится к вычислительной технике и может быть использовано для построения арифметических устройств, в которых контроль организован по четности, а используемые сумматоры формируют разрядные переносы параллельным способом.

Цель изобретения - повышение быстродействия и уменьшение количества оборудования.

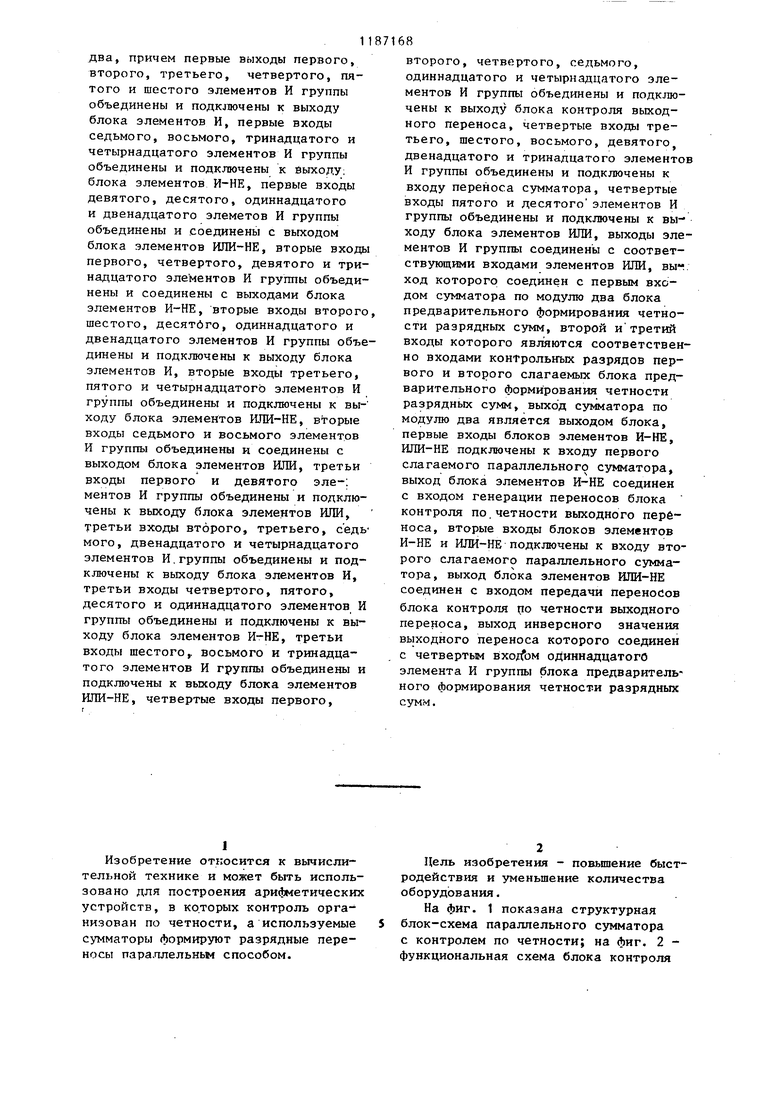

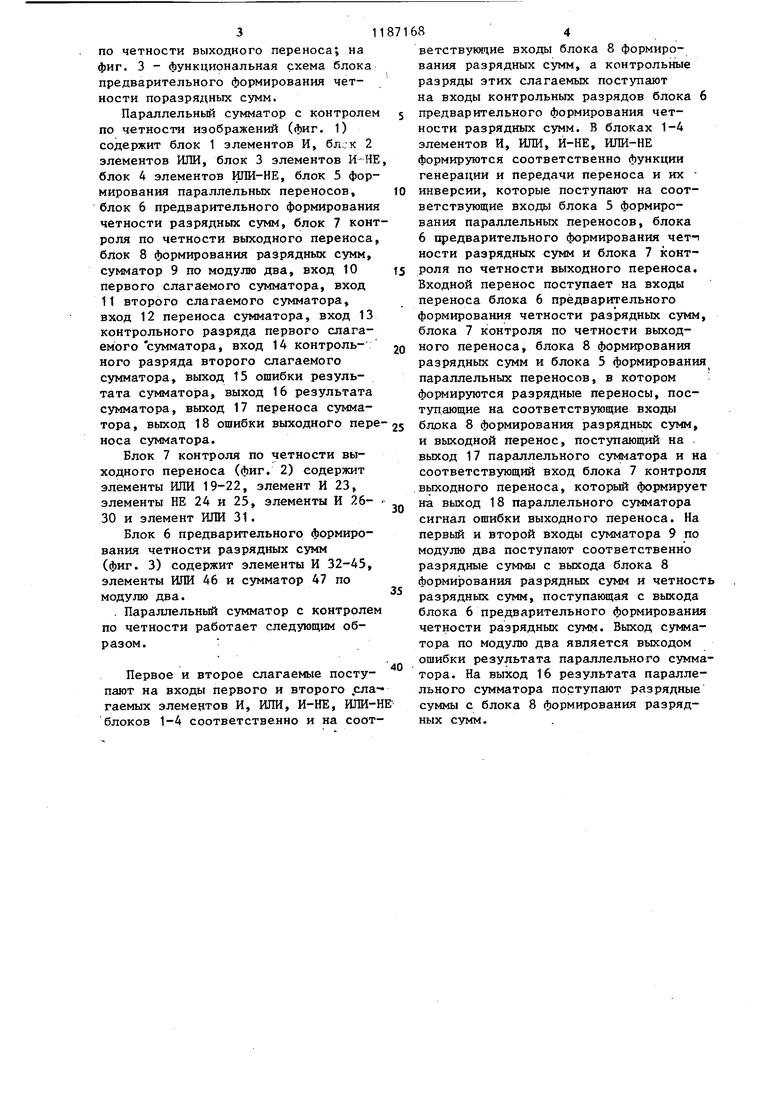

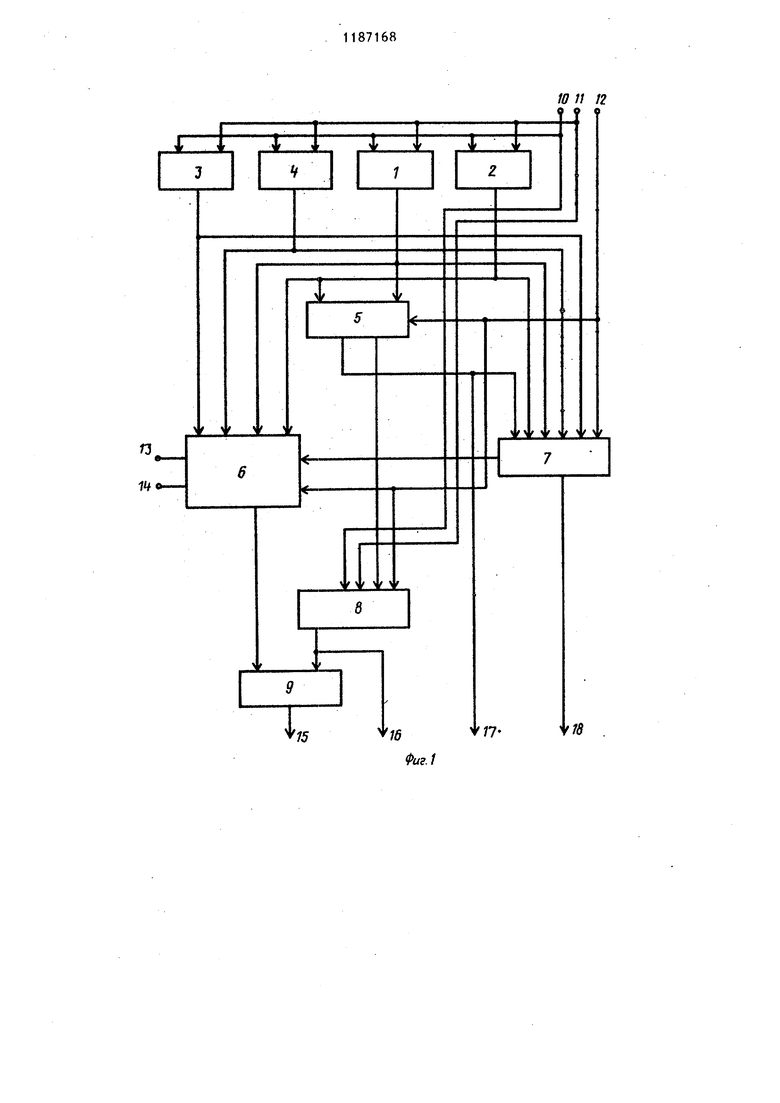

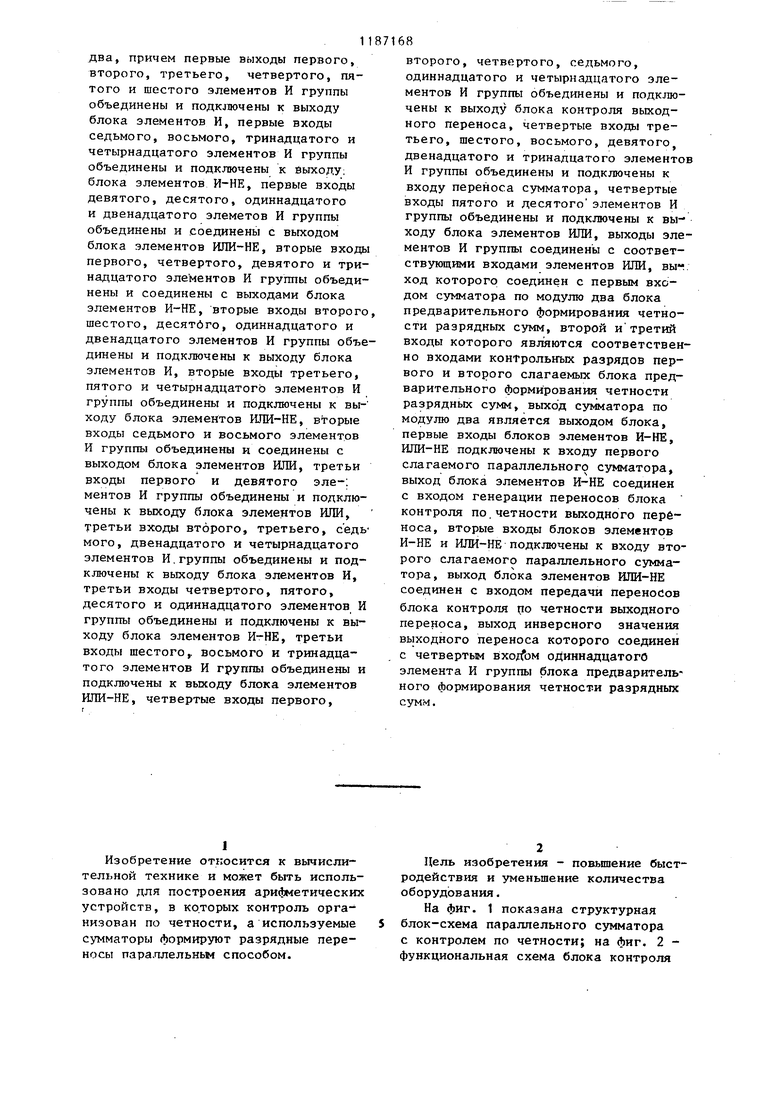

На фиг. 1 показана структурная блок-схема параллельного сумматора с контролем по четности; на фиг. 2 функциональная схема блока контроля 3 по четности выходного переноса; на фиг. 3 - функциональная схема блока предварительного формирования четности поразрядных сумм. Параллельный сумматор с контроле по четности изображений (фиг. 1) содержит блок 1 элементов И, блок 2 элементов ИЛИ, блок 3 элементов И-Н блок 4 элементов ИПИ-НЕ, блок 5 фор мирования параллельных переносов, блок 6 предварительного формировани четности разрядных сумм, блок 7 кон роля по четности выходного переноса блок 8 формирования разрядных сумм, сумматор 9 по модулю два, вход 10 первого слагаемого сумматора, вход 11 второго слагаемого сумматора, вход 12 переноса сумматора, вход 13 контрольного разряда первого слагаемого сумматора, вход 14 контрольного разряда второго слагаемого сумматора, выход 15 ошибки результата сумматора, выход 16 результата сумматора, выход 17 переноса сумматора , выход 18 ошибки выходного пер носа сумматора. Блок 7 контроля по четности выходного переноса (фиг. 2) содержит элементы ИЛИ 19-22, элемент И 23, элементы НЕ 24 и 25, элементы И 2630 и элемент ИЛИ 31. Блок 6 предварительного формирования четности разрядных сумм (фиг. 3) содержит элементы И 32-45, элементы ИЛИ 46 и сумматор 47 по модулю два. . Параллельный сумматор с контролем по четности работает следующим образом. Первое и второе слагаемые поступают на входы первого и второго сла гаемых элементов И, ИЛИ, И-НЕ, ИЛИблоков 1-4 соответственно и на соот 84 ветствую1цие входы блока 8 формирования разрядных сумм, а контролыаге разряды этих слагаемых поступают на входы контрольных разрядов блока 6 предварительного формирования четности разрядных сумм. В блоках 1-4 элементов И, ИЛИ, И-НЕ, ШШ-НЕ формируются соответственно функции генерации и передачи переноса и их инверсии, которые поступают на соответствующие входы блока 5 формирования параллельных переносов, блока 6 предварительного формирования чет-п ности разрядных сумм и блока 7 контроля по четности выходного переноса. Входной перенос поступает на входы переноса блока 6 предварительного формирования четности разрядных сумм, блока 7 контроля по четности выходного переноса, блока 8 формирования разрядных сумм и блока 5 формирования параллельных переносов, в котором формируются разрядные переносы, поступ.ающие на соответствующие входы блока 8 формирования разрядных сумм, и выходной перенос, поступающий на выход 17 параллельного сумматора и на соответствующий вход блока 7 контроля вьжодного переноса, который формирует на выход 18 параллельного сумматора сигнал ошибки выходного переноса. На первый и второй входы сумматора 9 по модулю два поступают соответственно разрядные суммы с выхода блока 8 формирования разрядных сумм и четность разрядных сумм, поступающая с выхода блока 6 предварительного формирования четности разрядных сумм. Выход сумматора по модулю два является выходом ошибки результата параллельного сумматора. На выход 16 результата параллельного сумматора поступают разрядные суммы с блока 8 формирования разрядных сумм.

to // /2

i I

3

f V

,

7V

f t f r

75

L f

/7У 7(9

Нблону9

| Авторское сввдетельство СССР №,739535, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ф.Селлерс | |||

| Методы обнаружения ошибок в работе ЭВМ | |||

| - М.: Мир, 1972, с | |||

| Реверсивный дисковый культиватор для тросовой тяги | 1923 |

|

SU130A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1985-10-23—Публикация

1984-04-16—Подача