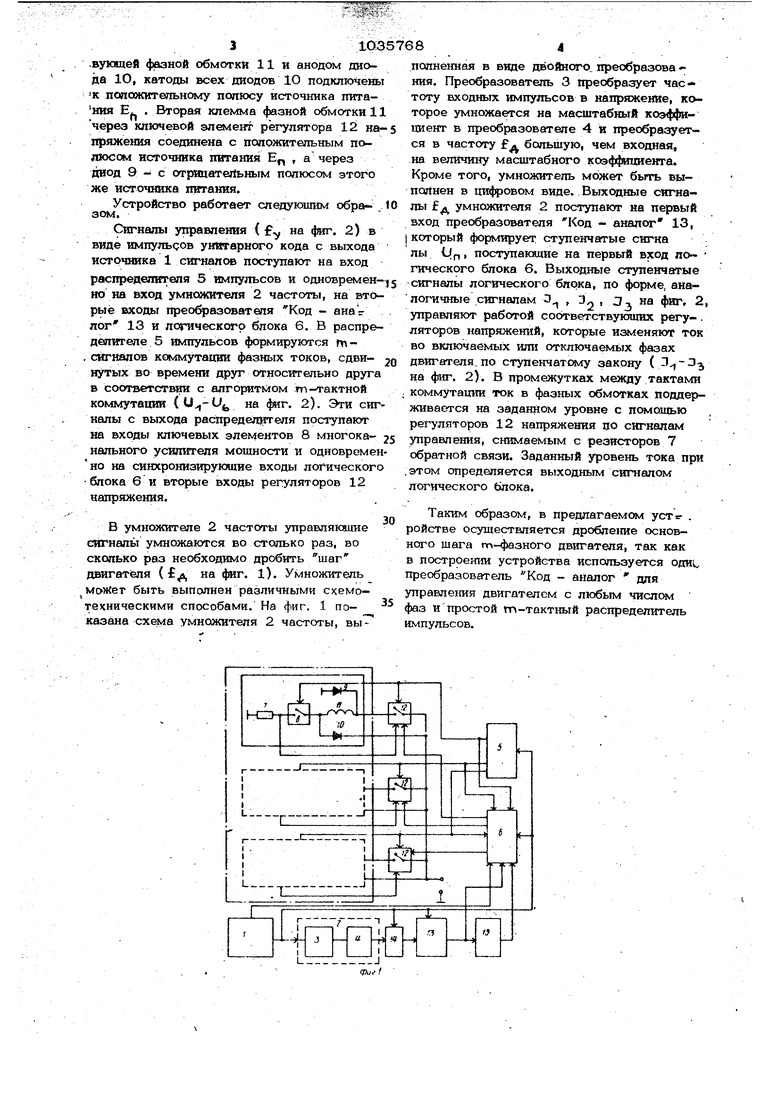

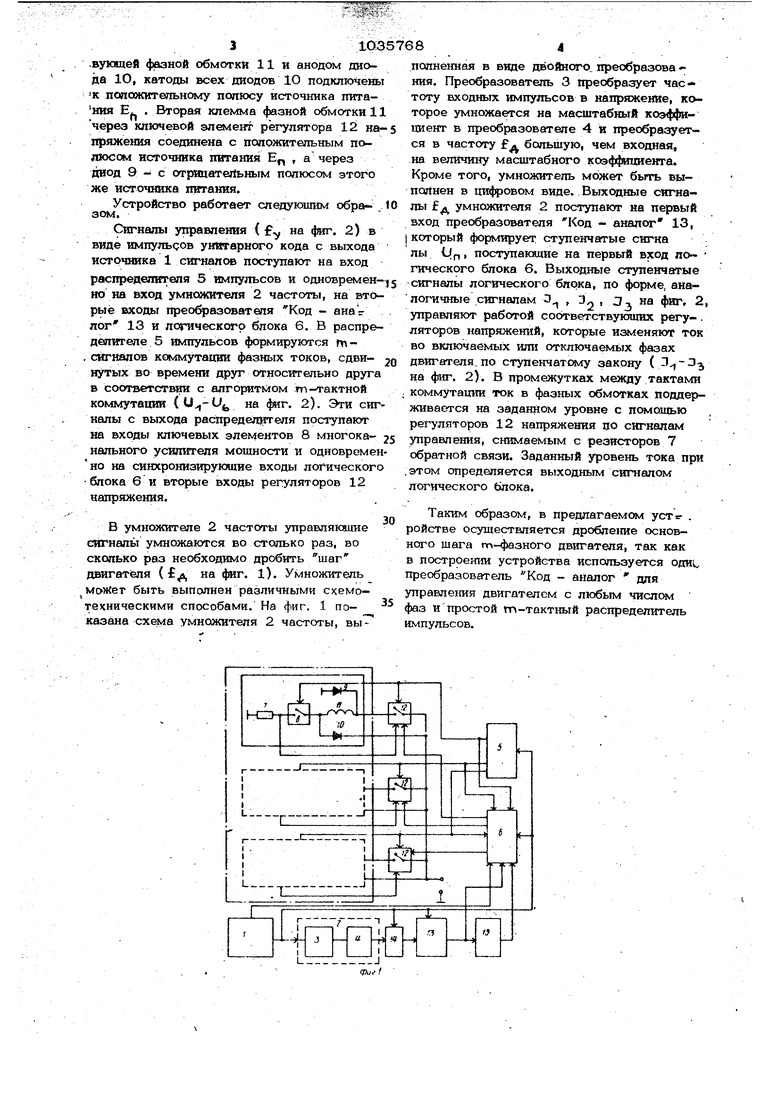

ИзобретейИе относится к эпектротехни е И мдасет быть иснопьзовано для управ « ленш шагошлми двигателями, например, в систолах числового прогфаммного управления метшшорежуншми станками. Известно устройство для управления фаговым двигателем с электрическим дроб лением шага, содержащее распределит ш импульсов, многоканальнетй усилитель мошности с рет упяторами напряжения на фаэах дашгатепя, преобразователи Код -. аналог и датчики обратной связи по току в фаэах двигателя f1 . Наибсотее близким по технической сущности и достигаемому результату является устройство для управления m-фазным шаговым двигателем с электрическим дробneHHewf шага, содержащее источник сигналов улфаБЛНИЯ, распреде«гштепь импульсов и Jr -каг альный усилитель мощности с ре . гуляторамв напряжения, изменяющими токи в фазах двигатеий по сигналам преобразователя Код - аналог, и резисторами обратной связи 3. Недостатком известных устройств является повышенная сложность, обуслоы1енкая бсв1ЫШ5м числом преобразователей Код анелог, особенно для многофазньгх двигателей. Цель изобретения - упрощение устройства, . . Поставленная цель достигается тем, что устройство для управления rrt-фазным шаговым двкгатеяем с электрическим дроб лением шага, содержащее источник сигнадов управления, распределитель импульсов и m-канальный усилитель мсяцности с ре гулятфами напряжения, изменяющими токи в фазах двигателя по сигналам преобра: ватш1я Код - аналог, и резисторы обратной связи, снабжено умножителем Ч|астоты синхронизатором, инвертором и логическим блоком, причем вход умножителя частот подключен к первому выходу источника сигналов управления, соединенному с входсйл распределителя импульсов, вторым входом синхронизатора и втчрыми входами преобразователя Код - аналог и логического блока, выход умножителя частоты соединен с первым входсы синхронизатора, подюкоченного выходом ко входу преобразователя, Код - аналог, соединенного вы«ходом с первым входсял логического блока и через инвертор - с третьим входгал пос ледаего, синхронизирующие входы логичеокого блока подключены к соответствуивдим выхода л распределителя, соединенным одновременно со входами fn-канального уси,лнтеля мощности, а выходы логического блока подключены к управляющим третьим входам соответствующих регуляторов на- пряж01ия, первые входы которых соединень с резисторами обратной связи, а вто рые входы подключены к соответствукигам выходам распределителя, выход ис точкика сигналов управления соединен с четвертым входом логического блока. На ijsir. 1 приведена функциональная схема предлагаемого устройства) на фиг. 2 - временные диаграммы сигналов, щлкютрируюшие работу схемы. Устройство (фиг. 1) содержит источ. НИК 1 сигналов управления, соединенный одним своим выходом с умножителем 2 частоты, включающим в себя преобразователи Чатота напряжение 3 и Напряжение - частота 4. Второй выход источника 1 сигналов управления подключен к входам распределителя S импульсов и логическото блока 6. Выходы распределителя S импульсов подключены к входам многоканального устогетеля мощности, каждый канал которого содержит резистор 7 обратной связи, ключевой элемент 8, разделительные диоды 9,10 и фазную обмотку 11 двигателя. Каждый канал усилителя мощности с обмоткой 11 двигателя подключи к выходу регулятора 12 напряжения. Преобразователь Код - аналог 13 связан входалда с одним из выходов источника 1 сигналов управления нетосредственно и через синхронизатор 14с выходом преобразователя. Напряжение - частота 4, а выходсал - с вторым входом логического блока 6 непосредственно, а с третьим входом этого же блока - через инвертор 15. источника 1 сигналов управления соеданен с входом распределителя 5, входом умножителя 2 частоты с синхронизирукнцими входами преобразователя 13, синхронизатсра 14 и логического блока 6. Выход умножителя 2 частоты через синхронизатор 14 соединен с входом преобразователя Код - аналог 13, выход которого подключен.к первому входу логического блока б.Синхронизируюшие входы логическогоблока б соединены с выходами рас шределителя 5, которые одновременно подключены Е входам соответствукшгах ключевых элементов 8 m-канального усилителя мо}1шости и вторым входам регуляторов 12 напряжения, первые входы которых подключены к резисторам 7 обратной связи, а управляющий вход каждого регулятора 12 соединен с соответствующим выход(Ж1 логического блока 6, Выход каждого ключе вого элемента 8 многоканального усилителя соединен с первой клеммой соответст.вукяцей фазной обмотки 11 и анодом диода 1О, катоды всех диодов 1О подключены К положительному полюсу источника питания Е , Вторая клемма фазной обмотки 1 через ключевой элемент регулятора 12 на пряжения соединена с псзяржитепьным полюсом источника питания Е, , а через ДИОД 9 - с отрицательным полюсом этого же источника питания. Устройство работает следующим обраэом. Сигналы управления { на фаг. 2) в виде импульсов унитарного кода с выхода источника 1 сигнале поступают на вход распределителя 5 импульсов и одновременКб на вход умножителя 2 частоты, на вто рые входы преобразователя Код - ана лог 13 и логическсмгр блока 6. В распре делителе 5 импульсов формируются m . сигналов коммуташш фазных токов, сдвинутых во времени друг относительно друга в соответствии с алгоритмом :тп-тактной коммуташти ( . на фиг. 2). Эти сиг налы с выхода распределителя поступают на входы ключевых элементов 8 многоканального усилителя мощности и одновреме но на синхронизирующие входы логическог блока 6 и вторые входы регуляторов 12 напряжения. В умножителе 2 частоты управляющие енгналь умножаются во столько раз, во сколько раз необходимо дробить шаг двигателя на фиг. 1). Умножитель моЖег быть выполнен различными схемотечническими способами. На фиг. 1 показана схема умножителя 2 частоты, вы полненная в виде двойного преобразова ния. Преобразователь 3 преобразует час тоту входных импульсов в напряжение, которое умножается на масштабный коэф П циент в преобразователе 4 и преобразуется в частоту д большую, чем входная, на величину масштабного коэффициента. Кроме того, умножитель может быть выnortHeH в цифровом виде. Выходные сигналы д умножителя 2 поступают на первый вход преобразователя Код - аналог 13, который формирует ступенчатые сигна лы (Jp, поступающие на первый вход по- гического блока 6. Выходные ступенчатые сигналы логического блока, по форме, аналогичные сигналам 3 , -з э ™ упраЕ1ляют работой соответствующих регу-. ляторов напряжений, которые изменяют ток во включаемых или отключаемых фазах двигателя, по ступенчатсму закону ( на фиг. 2). В промежутках между тактами коммутации ток в фазных обмотках поддерживается на заданном уровне с псжюшью регуляторов 12 напряжения по сигналам управления, снимаемым с резисторов 7 обратной связи. Заданный уровень тока при этом определяется выходным сигналом логического tmoKa. Таким образом, в предпагаемс д усте- . ройстве осуществляется дробле1ше основного шага т-фазного двигателя, так как в построении устройства используется одис реобразователь Код - аналог для правления двигателем с любым числен аз и простой т-тактный распределитель мпульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления шаговым двигателем | 1982 |

|

SU1042151A1 |

| Устройство для управления @ -фазным шаговым двигателем | 1984 |

|

SU1246331A1 |

| Устройство для управления @ -фазным шаговым двигателем | 1983 |

|

SU1115194A2 |

| Способ внутричерепной диагностики и устройство для его осуществления | 1989 |

|

SU1708307A1 |

| Устройство для управления шаговым двигателем | 1975 |

|

SU566294A2 |

| Устройство для управления шаговымэлЕКТРОдВигАТЕлЕМ | 1979 |

|

SU801217A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Устройство для управления -фазным шаговым двигателем | 1977 |

|

SU738091A2 |

| Устройство для управления п-шаговыми двигателями | 1983 |

|

SU1144183A1 |

| Способ фазового управления асинхронным электродвигателем и устройство для его осуществления | 1978 |

|

SU928582A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ гп ФАЗНЫМ ШАГСеЫМ ДВИГАТЕЛЕМ с электрическим дроблением шага, содержащее источник сигналов управления, распредетггель импульсов и m-канальный усилитель мощности с регуляторами напряжения, изменякииими токи в фазах пвигатеI ля по сигналам преобразователя Коа-ана(лсяг, и резисторами обратной связи, о т л и ч а ю щ ее с я тем, что, с целью упрощения устройства, оно снабжено умножвргелем частоты, синхронизатором, инвертором и логическим блоком, причем вход умножителя частоты подключен к первому выходу источника сигналов управления, соединенному с вкоаом распределителя импульсов, вторым входом сийхрониэатсзра ,и вторыми входами преобраэователя Коа-, аналог и логического блока, выход умножителя частоты соединен с первьлм входсж синхронизатора, подключенного выходом ко входу преобразователя Код - аналог, соединенного выходслл с входом логического блока и черезинвертор - с третьим входом последнего , синхрониз(Ирующие входы логического блока подключены к соответствующим вьтходам распределителя, соединенным одновременно со входами m-канального усилителя мовшости а выходаг лслтдческого блока подключены к управляющим третьим входам соответствующих регуляторов напр$шеН11я, первые входы которых соединены с резисторами обратной связи, а вторые етсоды подклк ч& ны к соответствующим выходам распредё- С лителя, wrapott выход источника сигналов управления соединен с четвертым входом 00 логического блока. Р1

44

.: :§

ь

Н

Ч

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления шаговым двигателем | 1975 |

|

SU566294A2 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ получения аргона | 1936 |

|

SU51441A1 |

| кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1983-08-15—Публикация

1981-12-29—Подача