причем информационный, управлйющий(п+1)-м выходом адресного блока сои адресный входы переключателя режи-ответственно, а выход переключателя

мов коммутации соединены с вторым .режимов коммутации соединен с :пправля-и пятым выходами вычислителя иющим входом распределителя импульсов.

1144183,

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1997 |

|

RU2125762C1 |

| Частотноуправляемый электропривод переменного тока | 1982 |

|

SU1086535A1 |

| Частотноуправляемый электропривод переменного тока | 1982 |

|

SU1086536A1 |

| УЛЬТРАЗВУКОВОЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС ДЛЯ ФОРМИРОВАНИЯ И ВИЗУАЛИЗАЦИИ ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 1997 |

|

RU2125836C1 |

| Устройство многопрограммного регулирования тепловых процессов | 1980 |

|

SU954970A1 |

| Калибратор фазы | 1988 |

|

SU1647449A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Устройство для регистрации ритма сердечной деятельности и характера его изменений | 1978 |

|

SU784867A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ П ЧИАГОВЬИН даИГАТЕЛЯМИ, содер жащее вычислитель, распределитель импульсов, адресный блок и подключенные к фазам двигателей ц многоканальных усилителей мощности с блоками памяти на входах, соединенными входами с соответствующими выходами адресного блока, отличающееся тем, что, с целью упрощения устройства, введены блок синхронизации, два оперативных запоминающих устройства, преобразователь параллельного кода в последовательный, причем nepBt выход вычислителя подключен к информационньм входам второго оперативного запоминающего устройства, третий выход вычислителя соединен с входом блока синхронизации, первьй выход которого подключен к входу управле- НИЯ режимом записи первого оператив«ого запоминающего устройства, четвертый выход вычислителя соединен с входом записи торо.го оперативного запоминающего устройства, второй. третий и пятый выходы блока синхронизации подюпочены соответственно к первым входам распределителя импульсов, преобразователя параллельного кода в последовательный и адресного ; блока, четвертый выход блока синхронизации соединен с вторьм входом адресного блока, (п + О-й выход которого соединен с адресными входами первого и второго оперативных запоми нающих устройств, а его (п+2)-й выход соединен с третьим входом преобразователя параллельного кода в последовательный, с вторьм входом которого соединен выход второго операс 5 тивного запоминающего устройства, первьв и второй выходы преобразоват ля параллельного кода в последовательный подключены соответственно к суммирующему и вычитающему входам . распределителя импульсбв,.третий выход преобразователя параллельного : кода в последовательный соединен с вз{одом вычислителя, информационные 4i 4 входы распределителя импульсов сое-; динены с выходами первого оперативг ного запоминающего устройства, инЭО &0 фо ; ационные входы которого подключены к первым информационным выходам распределителя импульсов, соединенного вторьми .шформацисжньми выходами с информационными входами блока злементов памяти всех каналов усилителей мощности. 2. Устройство по п. t, о т л ичающееся тем, что, с целью расширения функциональных возможностей, в него введен переключатель режимов коммутации, а распределитель импульсов выпотЬен многорежимным.

Из обретение относится к электротехнике, а именно к управлению несколькими шаговыми двигателями, и может быть использовано, например, в системах числового программного управления металлорежущими станками.

Известно устройство для управления несколькими шаговьми двигателями (ШД), содержащее вычиcлитёл 5нoe устройство, регистр команд, дешифраторы, блоки управления ШД, задатчики скорости, времени разгона и времени задержки, триггер разгона-торможения, счетчик импульсов отработки и формирователи импульсов Л .

Недостатки этого устройства сложность и низкое быстродействие, обусловленное последовательной QTработкой команд.

наиболее близким по технической сущности к изобретению является устройство для упоавления п -шаговыми двигателями, содержащее вычислитель, распределитель импульсов, адресный блок и подключенные к фазам двигаталей Ц многоканальных усилителей мощности с блоками памяти на входах, соединенными входами с соответствующими выходами адресного блока 2.

Недостатки известного устройствасложность и больщие аппаратные затраты при реализации. Кроме того, устройство, обеспечивая одновременно управление несколькими ШД, имеет ограниченные возможности и не позволяет изменять алгоритм управления ВД в динамике, а также не может управлять несколькими ШД различных типов

Цель изобретения - упрощение устройства и расширение его функциональных возможностей.

Поставленная цель достигается тем, что в устройство для управления П.-шаговыми двигателями, содержащее вычислитель, распределитель импульсов, адресный,блок и подключенные

к фазам двигателей П многоканальных усилителей мощности сблоками Ьамяти на входах, соединенными входами с соответствующими выходами адресного блока, введены блок синхронизации два оперативных запоминающих устройства и преобразователь параллельного кода в последовательный, первый выход вычислителя подключен к информационным входам второго оперативного запоминающего устройства, третий выход вычислителя соединен с входом блока синхронизации, первый выход которого подключен к входу управления режимом записи первого оперативного запоминающего устройства, четвертьй выход вычислителя соединен с входом записи второго оперативного запоминающего устройства, вторс, третий и пятый выходы блока синхронизации подключены соответственно к первым входам распределителя импульсов, преобразователя параллельного Кода в последовательный и ад;ресногр блока, а четвертый выход блока синхронизации соединен с вторым входом адресного блока, (п+1)й выход адресного блока соединен с адресными входами первого и второго оперативных запоминающих устройствj а (п+2)-й выход - с третьим входом преобразователя параллельного кода в последовательньй, с вторым входом которого соединен выход второго ofteративного запоминающего устройства, первый и второй выходы преобразователя параллельного кода в последо- вательньй подключены (ответственно к суммирующему и вычитающему входам распределителя импульсов, а его третий выход соединен с входом вычислителя , информационные входы распределителя импульсов - с выходами первого оперативного запоминающего устройства, подключенного своими информационньми входами к первьм

информационньм выходам распределителя импульсов, вторые информационные выходы которого соединены с информационньпчи входами блоков памяти всех каналов усилителей мрщности. 5

Кроме того, в устройство введен переключатель режимов коммутации, а распределитель импульсов выполнен многорежимным, информационный, управляющий и адресный входы переклю- fO чателя режимов коммутации соединены с вторым и пятым выходами вычислителя и (11 + 1)-м выходом адресного блока соответственно., выход переключателя режимов коммутации - с уп- 5 равляющим входом многорежимного распределителя импульсов.

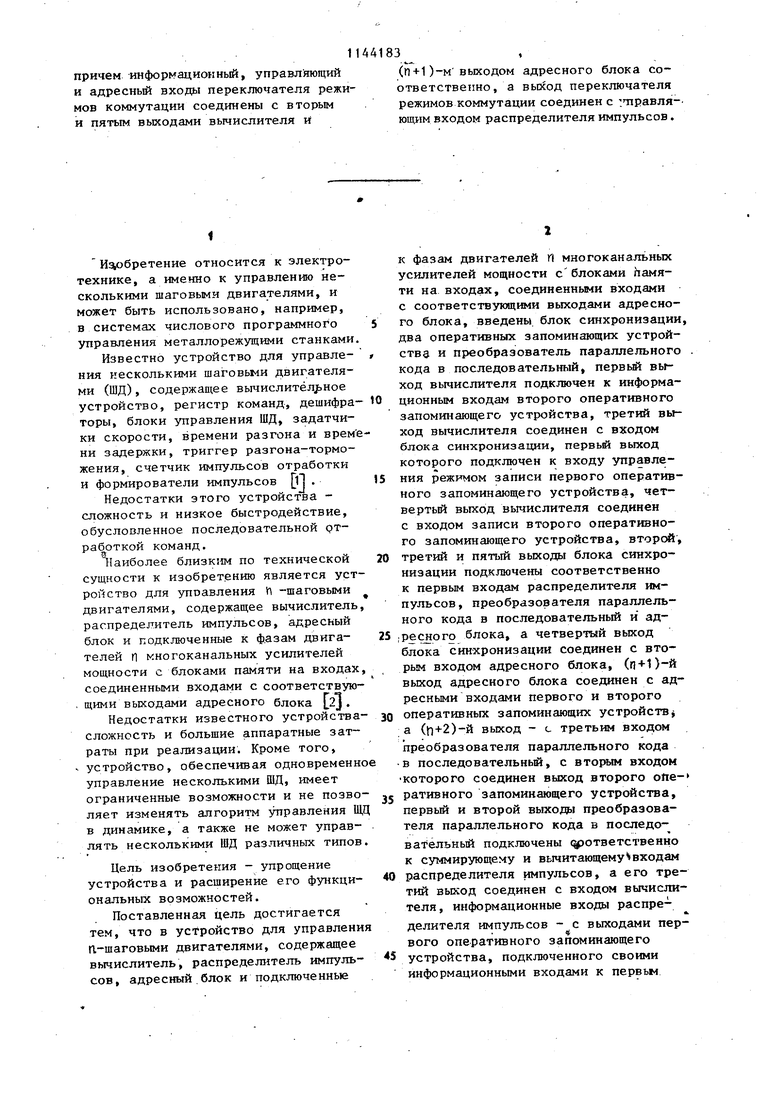

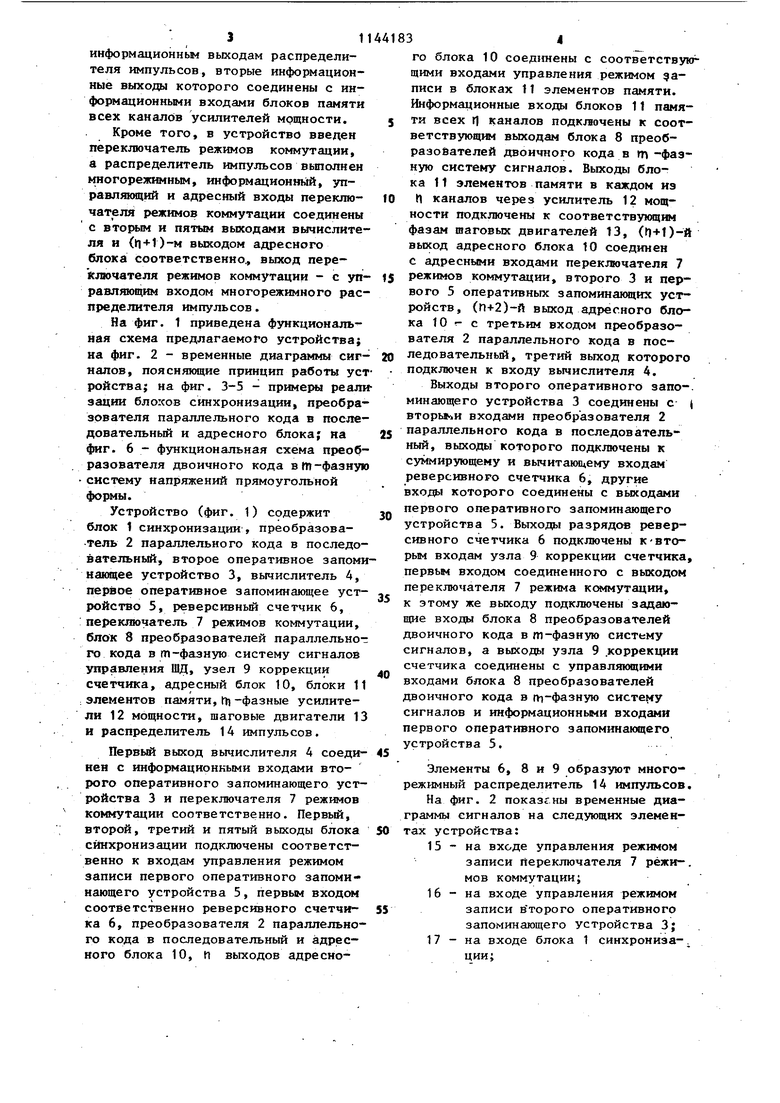

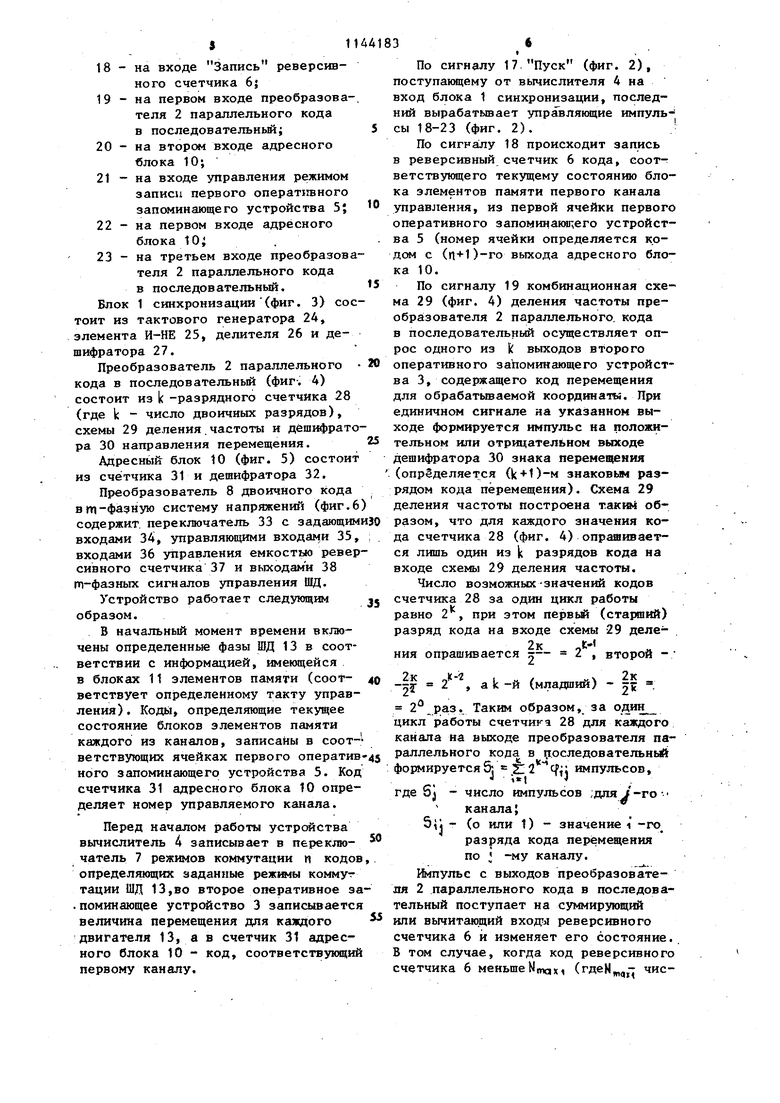

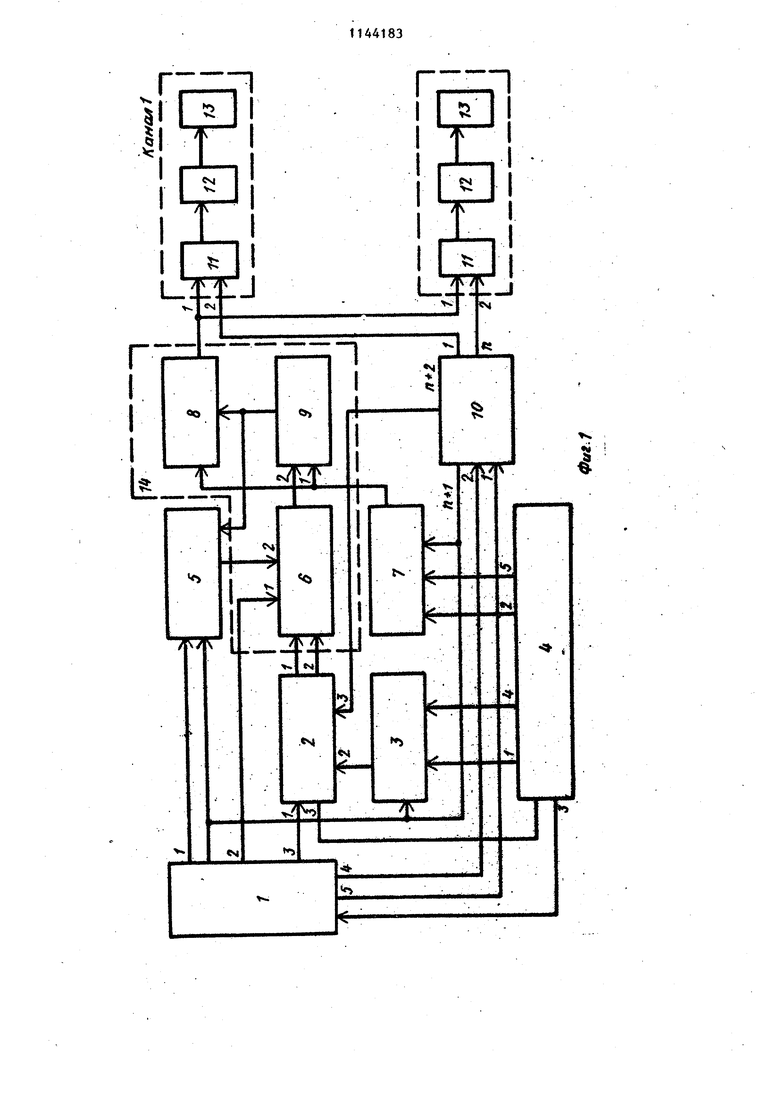

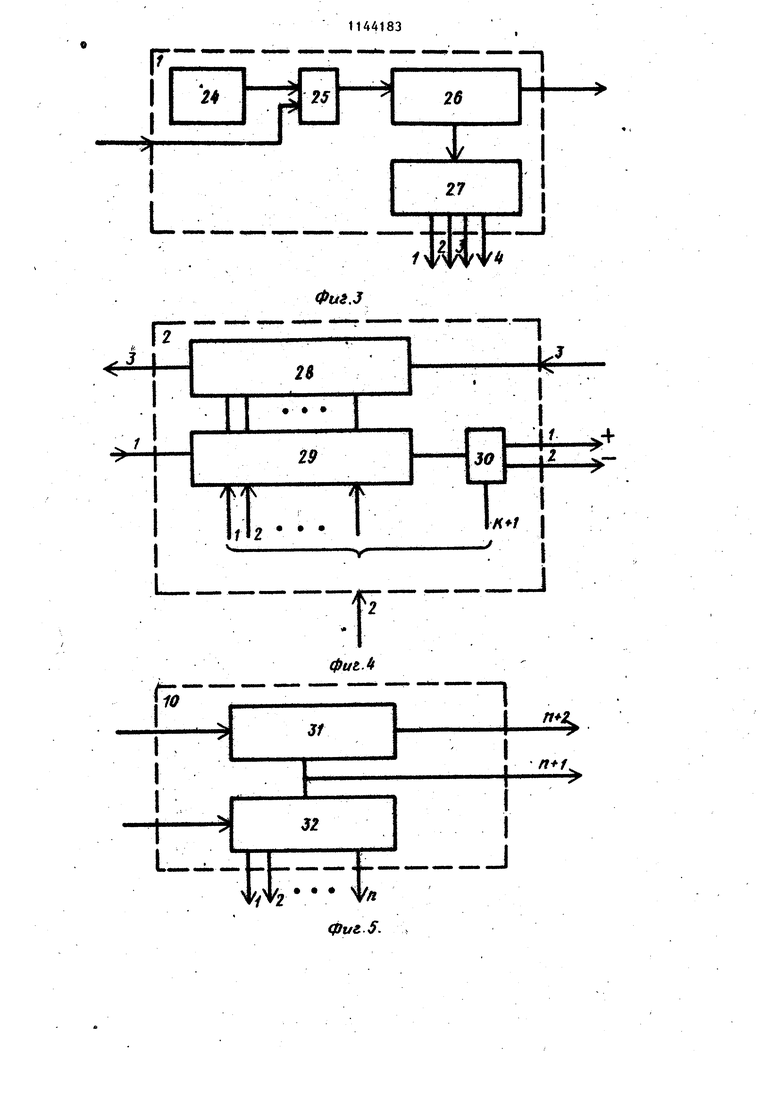

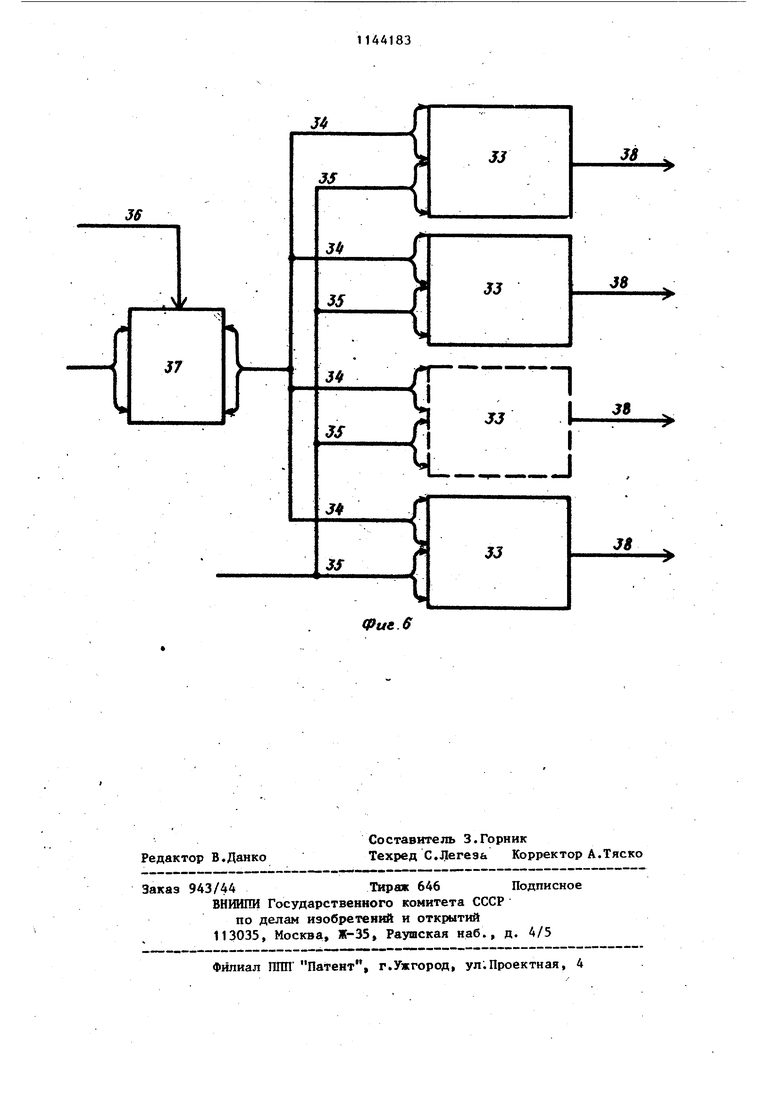

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы сиг- 20 налов, поясняющие принцип работы уст- ройства; на фиг. 3-5 - примеры реализации блоков синхронизации, преобразователя параллельного кода в последовательный и адресного блока; на 25 фиг. 6 - функциональная схема преобразователя двоичного кода Bfn-фазную систему напряжений прямоугольной формы.

Устройство (фиг. 1) содержит ЗО блок 1 синхронизации, преобразователь 2 параллельного кода в последовательный, второе оперативное запоминакицее устройство 3, вычислитель 4, первое оперативное запоминаиицее уст- ,, ройство 5, реверсивньй счетчик 6, переключатель 7 режимов коммутации, блок 8 преобразователей параллельного кода в т-фазную систему сигналов управления ШД, узел 9 коррекции Q счетчика, адресный блок 10, блоки 11 элементов памяти, fn -фазные усилители 12 мощности, шаговые двигатели 13 и распределитель 14 импульсов.

Первый выход вычислителя 4 соеди- 45 ней с информационными входами второго оперативного запоминающего устройства 3 и переключателя 7 режимов коммутации соответственно. Первый, второй, третий и пятый выходы блока 50 синхронизации подключены соответственно к входам управления режимом записи первого оперативного запоминающего устройства 5, первым входсм соответственно реверсивного счетчи- 55 ка 6, преобразователя 2 параллельного кода в последовательный и адресного блока 10, И выходов адресного блока 10 соединены с соответствующими входами управления режимом даписи в блоках 11 элементов памяти. Информационные входы блоков 11 памяти всех г) каналов подклочены к соответствующем выходам блока 8 преобразователей двоичного кода в 1т -фазную систему сигналов. Выходы блока 11 элементов памяти в каждом из h каналов через усилитель 12 мощности подключены к соответствуницим фазам шаговых двигателей 13, (1+1)-й выход адресного блока 10 соединен с адресными входами переключателя 7 режимов коммутации, второго 3 и первого 5 оперативных запоминающих устройств, (П+2)-й выход адресного блока 10 г- с третьим входом преобразователя 2 параллельного кода в последовательный, третий выход которого подключен к входу вычислителя 4.

Выходы второго оперативного запоминающего устройства 3 соединены с вторык и входами преобразователя 2 параллельного кода в последовательный, выходы которого подключены к суммирующему и вычитающему входам реверсивного счетчика 6, другие входы которого соединены с выходами первого оперативного запоминающего устройства 5. Выходы разрядов реверсивного счетчика 6 подключены к-вторым входам узла 9 коррекции счетчика первьм входом соединенного с выходом переключателя 7 режима коммутации, к этому же выходу подключены задгио- щие входы блока 8 преобразователей двоичного кода в т-фазную систему сигналов, а выходы узла 9 коррекции счетчика соединены с управлякицими входами блока 8 преобразователей двоичного кода в ги фазную систему сигналов и информационными входами первого оперативного запоминающего устройства 5.

Элементы 6, 8 и 9 образуют многорежимный распределитель 14 импульсов

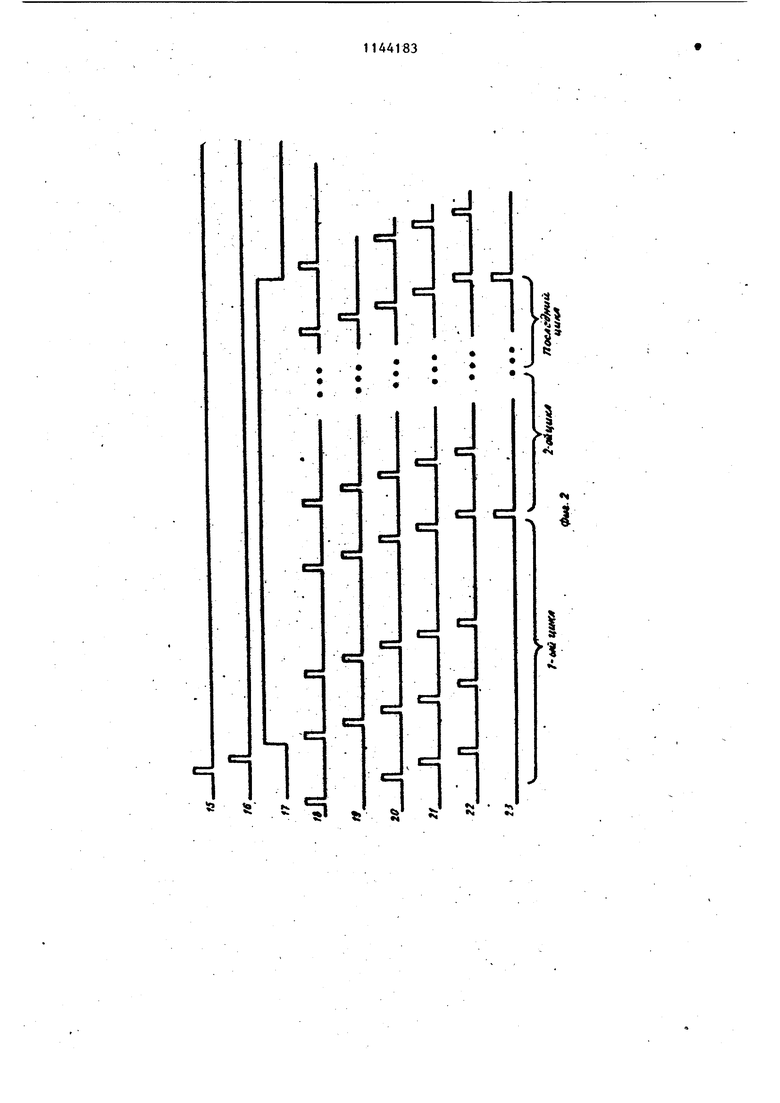

На фиг. 2 показаны временные диаграммы сигналов на следующих элементах устройства:

15- на входе управления режимом

записи Переключателя 7 рёжи мов коммутации;

16- на входе управления режимом

записи второго оперативного запоминающего устройства 3;

17- на входе блока 1 синхронизации;SП 18- на входе Запись реверсивного счетчика 6; 19- на первом входе преобразователя 2 параллельного кода в последовательный; 20- на втором входе адресного блока 10; 21- на входе управления режимом записи первого операт1тного запоминающего устройства 5; 22- на первом входе адресного блока 10i . 23- на третьем входе преобразова теля 2 параллельного кода в последовательный. Блок 1 синхронизации (фиг. 3) сос тоит из тактового генератора 24, элемента И-НЕ 25, делителя 26 и дешифратора 27. Преобразователь 2 параллельного кода в последовательньй (фиг-. 4) состоит из k -разрядного счетчика 28 (где k - число двоичных разрядов), схемы 29 деления.частоты и дешифрато ра 30 направления перемещения. Адресный блок tO (фиг. 5) состои из счётчика 31 и дешифратора 32. Преобразователь 8 двоичного кода вm-фазную систему напряжений (фиг. содержит, переключатель 33 с задающим входами 34, управляющими входами 35 входами 36 управления емкостью реве сивного счетчика 37 и выходами 38 т-фазных сигналов управления ИЩ. Устройство работает следующим образом. В начальный момент времени включены определенные фазы ШД 13 в соот ветствии с информацией, имеющейся в блоках 11 элементов памяти (соответствует определенному такту управ ления) . Кодй, определяющие текущее состояние блоков элементов памяти каждого из каналов, записаны в соот ветствующих ячейках первого операти ного запоминающего устройства 5. Ко счетчика 31 адресного блока 10 опре деляет номер управляемого канала. Перед началом работы устройства вычислитель 4 записывает в переключатель 7 режимов коммутации п кодо определяющих заданные режимы коммут тации ШД 13,во второе оперативное з .поминающее устройство 3 записываетс величина перемещения для каждого двигателя 13, а в счетчик 31 адресного блока 10 - код, соответствующи первому каналу. 36 По сигналу 17.Пуск (фиг. 2), поступающему от вычислителя 4 на вход блока 1 синхронизации, последний вырабатывает управляющие импульсы 18-23 (фиг. 2). По сигналу 18 происходит запись в реверсивный счетчик 6 кода, соот ветствующего текущему состоянию блока элементов памяти первого канала управления, из первой ячейки первого оперативного запоминакмцего устройства 5 (номер ячейки определяется крдсм с (п+1)-го выхода адресного блока 10. По сигналу 19 комбинационная схема 29 (фиг. 4) деления частоты преобразователя 2 параллельного, кода в последовательный осуществляет опрос одного из Ц; выходов второго оперативного за минающего устройства 3, содержащего код перемещения для обрабатьгоаемой координаты. При единичном сигнале на указанном выходе формируется импульс на положительном или отрицательном выходе дешифратора 30 знака перемещения (определяется (|()-м знаковым разрядом кода перемещения). Схема 29 деления частоты построена тлккн образом, что для каждого значения кода счетчика 28 (фиг. 4) опрашивается лишь один из k разрядов кода на входе схемы 29 деления частоты. Число возможных-значений кодов счетчика 28 за один цикл работы равно 2, при этом первый (старший) разряд кода на входе схемы 29 деле2кt ния опрашивается j- 2 , второй -; 2 , а k -и (младший) - r|j .з. Таким образом, за один цикл работы счетчика 28 для каждого канала на выходе преобразователя параллельного кода в последовательный формируется5; импульсов, J i«l J где Sj - число импульсов ;для У-гоканала; - (о ипи 1) - значение i -го разряда кода перемещения по -му каналу. йетульс с выходов преобразователя 2 .параллельного кода в последовательный поступает на суммирующий ипи вычитающий входил реверсивного счетчика 6 и изменяет его состояние. В том случае, когда код реверсивного счетчика 6 меньше Мтам (,- число тактов в одном цикле коммутации), код tia выходе узла 9 коррекции счетчика 6 совпадает с кодом последнего. Если же код реверсивного счетчика 6 равен нулю (перемещение на один шаг в минус), то код на выходе узла 9 коррекции счетчика 6 устанавливается в Hniqxi случае появления кода N, +1 на выходах счетчиков (перемещение на один шаг в плюс из кода N, ,) на выходе узла 9 коррекции формируется код единицы. Таким образом, узел 9 коррекции обеспечивает циклическое изменение кода счетчика б с периодомН как при положительном, так и при отрицательном нап равлении перемещения, причем ,определяется -кодом, записанным в соответствующей ячейке переключателя 7 режимов коммутации, иможет оператив-20 но изменяться вычислителем 4 в процессе работы устройства. Код с выхода узла 9 коррекции счетчика поступает на адресные вход блока 8 преобразователя двоичного кода в m -фазную систему сигналов, на задаюпфгх входах которого установ . лен код с. выхода переклочателя 7 ре ЖШ4ОВ коммутации. Сигналы с выходов блока 8 преобразователей поступают на первые входы блоков 11 элементов .памяти каждого из каналов. Адрес управляемого в данный момент канала определяет номер одного из ц выходов адресного блока 10 (в рассматриваемом случае - первого ма котором по сигналу 20 формируется импульс записи кода с выхода бло ка 8 преобразователя в блок 11 элементов памяти управляемого канала. По сигналу 21 (фиг. 2) код с выхода узла 9 коррекции счетчика 6 записывается в ячейку первого опера тивного запоминающего устройства 5, адрес которой поступает с ()-го выхода адресного блока 10. По сигналу 22 (фиг. 2) код адреса в адресном блоке 10 увеличивается на единицу, и устройство переход к управлению следующим каналом. После окончания указанных циклов счетчик 31 (фиг. 5) адресного блока 10 переполняется, а импульс 23 с его (|И-2)-го выхода увеличивает значение кода счетчика 28 преобразователя 2 на единицу..Преобразователь 2 .параллельного кода в последовательный переходит к следующеь у циклу преобразования. В течение каждого из указанных циклов происходит изменение (если это требуется) состояний всех л каналов управления двигателями, что обеспечивает одновременное и независимое управление каждым двигателем 13 путем работы распределителя 14 в режиме разделения времени. Переполнение счетчика 28 вызьгаает появление сигнала на третьем выходе преобразователя 2 параллельного кода в последовательный, который, поступая в вычислитель 4, дает команду запроса на выдачу следующих заданий на перемещение или остановку двигателей, Если период запросов в вычислитель 4 достаточно мал, устройство работает в контурном режиме. При этом любая криволинейная траектория . заменяется ломаной линией, состоящей из малых отрезков прямых линий. Адресный блок 10 (фиг. 5) обеспечивает последовательную во времени работу всех каналов управления, т.е. обеспечивает перезапись информации из блока 8 преобразователей двоичного кода в т-фазную систему сигналов в блок 11 элементов памяти управляемого в данный момент времени канала. Введение в устройство для управления несколькими двигателями двух оперативных запоминающих устройств, блока синхронизации, переключателя режимов коммутации и преобразователя параллельного кода в последова- тельньй дает возможность управлять различными типами двигателей и программно изменять алгоритмы коммутации их фаз в процессе работы. При использовании в одном изделии различных типов ШД отпадае- необходимость разработки специализированных систем, управления для каждого типа двигателя, что снижает аппаратурные затраты, повышает надежность и весо-габаритные характеристики. Изменение алгоритма коммутации программно в процессе работы позволяет улучшить динамические характеристики привода, уменьшает время разгона и торможения, повьпиает производительность привода ча счет увеличения скорости двигателя.

14

1

а «5

«N

; I

I

t

s:

N«4

Фи.

Г

2$

1144183

п

1

29

тп т

Iflz I

фиг л

f7n

/

Jf

.ij:I

4vv2VV Фл

фиг. У.

,

1

4-2:4.

JS

JJ

J8

JJ

37

Г

п

je

JJ

L,I

J

JJ

6

| I | |||

| Луценко В.В., Рубцов В.П | |||

| апектропривод с иаговьми двигателя | |||

| ми. | |||

| - Электропривод и автоматизация промьшленных установок | |||

| Т | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ВИНИТИ, 1978, с | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство для управленияшАгОВыМи дВигАТЕляМи | 1978 |

|

SU798731A1 |

Авторы

Даты

1985-03-07—Публикация

1983-05-06—Подача