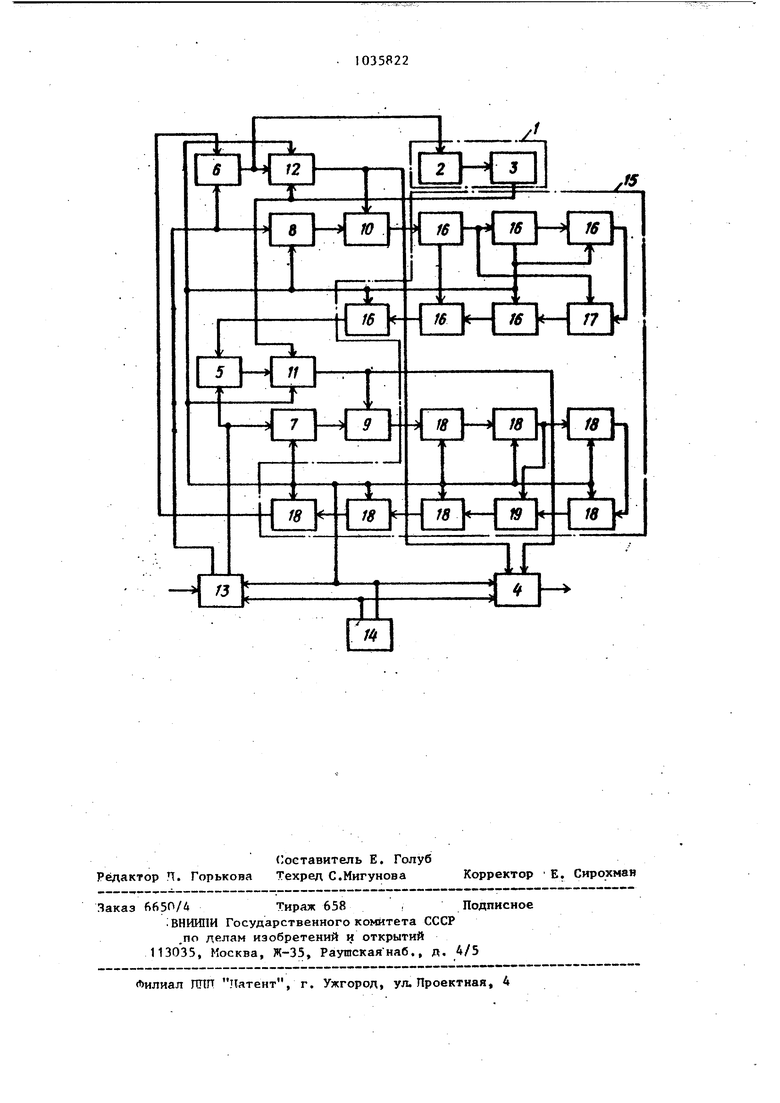

Ияобретенне относится к технике измерений в цнфроиьгх линиях связи и может использоваться для выявлени сбоеп испытательного псевдослучаймого сигналя, поступающего линии связи, а также на выходе лини связи. 11илью изобретения является повышение точности контроля при увеличении тактовой частоты псевдослучай ного испытательного сигнала и умень шение уровня собственных помех, а также уменьшение искажений структуры пачек сбоев. На чертеже приведена структурная электрическая схема устройства для контроля сбоев псевдослучайного испытательного сигнала. Устройство для контроля сбоев, псевдослучайного испытательного сигнала содержит блок 1 интегрирования, состоящий из фильтра 2 нижни част т и порогового элемента 3, выходной коммутатор f сумматоры 5 и по модулю два, блоки 7 и 8 задержки дополнительные сумматоры 9 и 10 по дулю два5D-триггеры 11 и 12, входной кo г yтaтop 13, генератор 1 так вой частоты, генератор 15 псевдо-. случайного сигнала в параллельном коде, состоящий из двух ветвей, в первой из которых имеются В -тригге 16, и сумматор 17 по модулю два, а во второй ветви В-триггеры 18 и сумматор 19по подулю два. Устройство работает следуки1им образом. Исследуемый сигнал в виде М-последовательности поступает на вход входного коммутатора 13, который осуществляет преобразование из последовательного кода на входе я двухразрядный бинарный параллельньй код на своих выходах. При этом на каждом выходе входного коммутатора 13 длительность кодового импульс равна двум тактовым интервалам, причем сигнал, поступающий на вход .сумматора 5, соответствует сигналу 5„., в первой половине предьццущего двухтактного интервала, а сигнал, поступающий на вход сумматора 6 - сигналу. 5р во второй половине предыдущего двухтактового интервала преобразования из последовательного кода на входе в параллельный код на выходе входного коммутатора 13, Чачя.гю двухтактоного иите. задастся напряжением полутактопой частоты с имхода генератора 1А тактовой частоты. Генератор /4 входит в постав регенерационной аппаратуры исследуемой линии связи, либо является специальным выделителем тактовой частоты в данном устройстве, подобным выделителем тактовой часПб.означим 5 тоты регенераторов, с; соответственно, коды сигналов на выходах Г -триггеров 11 и 12 аналогично кодам 3 и 5 в первой и второй половинах двухтактового интервала, задаваемого напряжением полутактовой частоты свыхода генератора 1Д тактовой частоты. Выразим, 5 и через 5. и 5„ и оператор задержки Д . Поскольку задержка в каждом из элементов, составляющих генератор 15, равна двум такто.вым интервалам, то оператор задержки для каждого из Ц .-триггеров 11 и. 12 выражается в форме X .т Устройство для контроля сбоев всевдослучайного испытательного сигнала может работат.ь в двух режимах: режим синхронизации, когда Б -трипгеры 11 и 12 сброшены в нулевое состояние импульсом, сформированным на выходе порогового элемента 3 блока интегрирования 1 режим измерения сбоев, когда логические уровни напряжения на выходах D-триггеров 11 и 12 изменяются в соответствии с сигналами на входах сумматоров 5 и 6, поскольку логический уровень напряжения на выходе порогового элемента 3 равен нулю, .Получим вьфажение для кодов 5 и 5 на выходах сумматоров 5 и 6 в первой и второй полоринах двухтактового интервала в режиме синхронизации, при котором с выхода сумматора 6 на вход блока 1 интегрирования поступает непрерывный поток импульсов с шибок. 1а выходе .блока 1 интегрирования вырабатывается при этом сигнал уровня логической единицы, который сбрасывает в нулевое состояние и -триггеры 11 и 12. Указанный поток импульсов ошибок образуется лотому, что сигнал, записанный в И -триггерах 16 и 18 генератора 15 в момент включения устройства, не соответствует по структуре всевдослучайной последорате.пьности, поступающей на вход входного комму татора 13. В этом случае код сигнала S в ражается суммой по модулю два кода ha одном входе сумматора 5 и хода яа выходе последнего 3)-триггера 1б первой ветви генератора 15, кот рый можно выразить в следующем виде: . vCsn n y (1 где выражение в скобках соответствует коду на выходе сумматора 17 по модулю два генератора 15, которое является результатом суммирования кода первом входе сумматора 17 и кода 5«Х- на втором его входе. Тогда справедливо соотношение-;. 5;,-.-1 Ч «.« « Аналогично можно вычислить, что код на выходе сумматора 6 5|, выражается в виде .f(s .хЧ9„,х )., , Код Sf, является результатом задержки всевдослучайного сигнала на один такт. Поэтому, используя оператор згщержки, можно записать соотношение Sn-Sn--. () (2) и (3), подставив которое лучим выражения s;,.5.,O.); .11 S.) Х COOTв которых полином 1 + ветствует образующему полиному генератора 15 псевдослучайного сигна ла в виде М-последовательности со структурой обратных связей, показа ной на чертеже. Если псевдослучайный сигнал 5,. 5|, вырабатьгаается генератором 15 со структурой обратных связей, опи сываемой образу1011(им полином 1 f х + У, и не содержит сбоев , то н 5 равны нулю (в установившемся режиме). В этом случае на входах сброса D -триггеров 11 и 12 устаг новится напряжение логического нул поскольку на вход блока 1 интегрн: 24рования поступает нулевое напряжений. В результате D -триггеры 11 и 12 будут функционировать как блоки 7 и 8 задержки. Устройство для контроля сбоев псевдослучайного,испытательного сигнала переходит в режим изменения сбоев. Если при этом в псевдослучайном сигнале появляются отклонения (сбои) Е по сравнению с эталонной М-последовательностью, т.е. Vi-5M(,.,)-i . 5п t« гдеЗдц/,,,,}, 5м„ - соответствующие значения кодов для Мгпоследовательности в первой и второй половинах двухтактового интервала, Е. , Е„ аналогичные значения для сбоев М-последовательности, то на входах В-триггеров 11 и 12 появляются сигналы ошибки 5|, , S}, , которые меняют логические уровни поступающего входного сигнала Sp. S. При этом опорная псевдослучайная последовательность, записанная ранее в генераторе 15, не меняется. Благодаря этому на .выходах Ь -триггеров 11 и 12 выделяется сигнал ошибок (сбоев) 5., , Sj, соответствующие сигналам сбоев ЕП. , Е входного испытательного .псевдослучайного сигнала 5 „, , 5f, . Стуктура пачек сбоев в таком случае регистрируется без искажений, причем на сигнальных входах выходного коммутатора 4 появляются сигналы . 5 «Е 5:,-fn п-1 первый из которых при мультиплексировании на выход выходного коммутатора 4 появляется в первой половине двухтактного интервала, а второй - во второй половине двухтактного интервала напряжения полутактовой частоты. Покажем теперь, каким образом выходные сигналы 5., 51, выражаются через входные сигналы 5, данного устройства, работаюего в режиме измерения сбоев, моет быть записана следующая систеа уравнений (5п-5з5)

Sn.r(5n-/.4). 0)

V.)), (11) 5

) .(«)

где Sij 5я сигналы на выходах последних Г -триггеров 18 и 16 обоик 10 ветвей генератора 15.

Из системы уравнений (10) - (13) могут быть получены следующие уравнения для 5|,. и S{,;:

;-5п 5„н(«)5и(Лх),(«,.

s;v,-v, ((,(«i откуда следует, что с учетом (4)

s;.5,)-5:(xn), («)

5:rv,x(Ax«),(i -). w

Уо ножение на образунлций полином 1. + Х Х в .уравнениях .(16), (17) означает вьщеление ошибок; Е ,;.,, Е (7) и (8) из принятой М-последовательности. Поэтому уравнения (16), (17) для сбоев Е. , Е могут быть осле соотйетствуюрщх преобразований записаны в следующей форме

Е„.Е,Х , Е .;.Е,.,Х , («1

где tf,,, п сигналы оншбок (сбоев) на сигнальный входах выходного коммутатора 4.

Уравнение US) показывает, что сигнал ошибок на выходе выходного

коммутатора 4 задержан на два тактовых интервала по отношению к сигналу ошибок (сбоев) во входной последовательности, однако, структура пачки сбоев на выходе полностью соответствует структуре пачки сбоев на входе.

Таким образом, благодаря тому, что имеющиеся в предложенном устройстве дополнительные сумматоры 9, 10 по модулю два, а также сумматоры 17, 19 нигде не соединяются непосредственно друг с другом, поскольку разделены D -триггерами, сумма задержек в сумматоре 5 по модулю два fe и в il-триггере 11 должна быть меньше двоного тактового интервала 2Т, т.е..

(20)

20

Если Тg Tj 4 но, то максимальное значение тактовой частоты i 1/Т равно 250 МГц, что в 5 раэ превышает соответствующее значение, достижимое в прототипе.

Поскольку основной тракт работае на полутактовой частоте, уменьшается уровень собственных помех в выхоном сигнале.

При необходимости дальнейшего .повышения быстродействия следует увеличить количество параллельных ветвей предложенного устройства.

Кроме того, из-за отсутствия искажений структуры пачек сбоев повышается точность контроля сбоев псевдослучайного испытательного сигнала и позволяется возможность проводить исследования статистики сбоев и их корреляционных характеритик.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1984 |

|

SU1234985A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1267595A2 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Устройство для контроля ошибок многоканального аппарата магнитной записи | 1987 |

|

SU1432604A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| Устройство для контроля ошибок магнитной записи-воспроизведения цифровой информации | 1985 |

|

SU1273994A1 |

| Генератор псевдослучайных чисел | 1987 |

|

SU1529218A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СБОЕВ ПСЕВДОСЛУЧАЙНОГО ИСНЪГГАТЕПЬНОГО СИГНАЛА, содержащее генератор тактовой частоты, выходы которого подключены к синхронияирующему входу генератора псевдослучайного сигнала в параллельном коде и к управляющим входам выходного коммутатора, отличающееся тем, что, с целью повьшения точности контроля при увеличении тактовой частоты псевдослучайного испытательного сигнала и у геньшения уровня собственных помех, в него введены сумматоры по модулю два и входной коммутатор, выходы котопого подключены к сигнальным входам генератора всевдослучайного сигнала в параллельном коде, соединенным с входами соответствующих сумматоров по модулю два, другие входы которых :-...-..-.„ . соединены с выходами генератора псевдослучайного сигнала я параллельном коде, а выходы подключены к сигнальным входам выходного ком гутатора, причем выходы генератора тактовой частоты подключены к управляющим входам входного коммутатора. 2. Устройство по п. 1, о т л ичаю::ееся тем, что, с целью уменьшения искажений структуры пачек сбоев, между каждым из выходов входного коммутатора и соответствующим сигнальным входом генератора псевдослучайного сигнала в параллельном коS де включена введенная цепь из последовательно соединенных Рлока задержел ки и дополнительного сумматора по модулю два, а между выходом каждого сумматора по модулю два и соответствующим сигнальным входом выходного коммутатора включен введенный D-триггер, ко входу сброса каждого из которых подключен выхсгд введенсо ного блока интегрирования, вход коСП 00 торого соединен с выходом одного из сумматоров по модулю два, при го этом синхронизируюгще входы блоков задержки и J) -триггеров соединены с одним из выходов генератора тактовой частоты. 3. Устройство по п. 2, о т л и-. а ю щ е е с я тем, что блок ин тегрирования содержит последовяте.пьно соединенные фильтр нижних частот и пороговый элемент.

| Способ получения ускорителей путем обработки паст связующими веществами | 1959 |

|

SU128139A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Патент OlA , кя | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| () | |||

Авторы

Даты

1983-08-15—Публикация

1981-05-18—Подача