где S41 и S33 - сигналы на выходах D- триггеров 41 и 33 генератора 1 псевдослучайной последовательности. Из системы уравнений (8) - (11)

могут быть получены следующие урав

и S

«

+ Sn-i(x

14

+ X11) +

+ S „,(

+ х

Г,

S., - SB., х + Sn(x

14

+ X

u}

+ s; (x

10 + х 14

),

(3)

откуда следует, что с учетом S h - Shx20+x + х 1S) +

x15) -, (12)

0

5

5

Если

В-4

не,

то максимальное значение тактовой частоты f 1/Т равно 250 Ш ц.

В предлагаемом устройстве регистрация импульсов сбоев (ошибок) производится следующим образом.

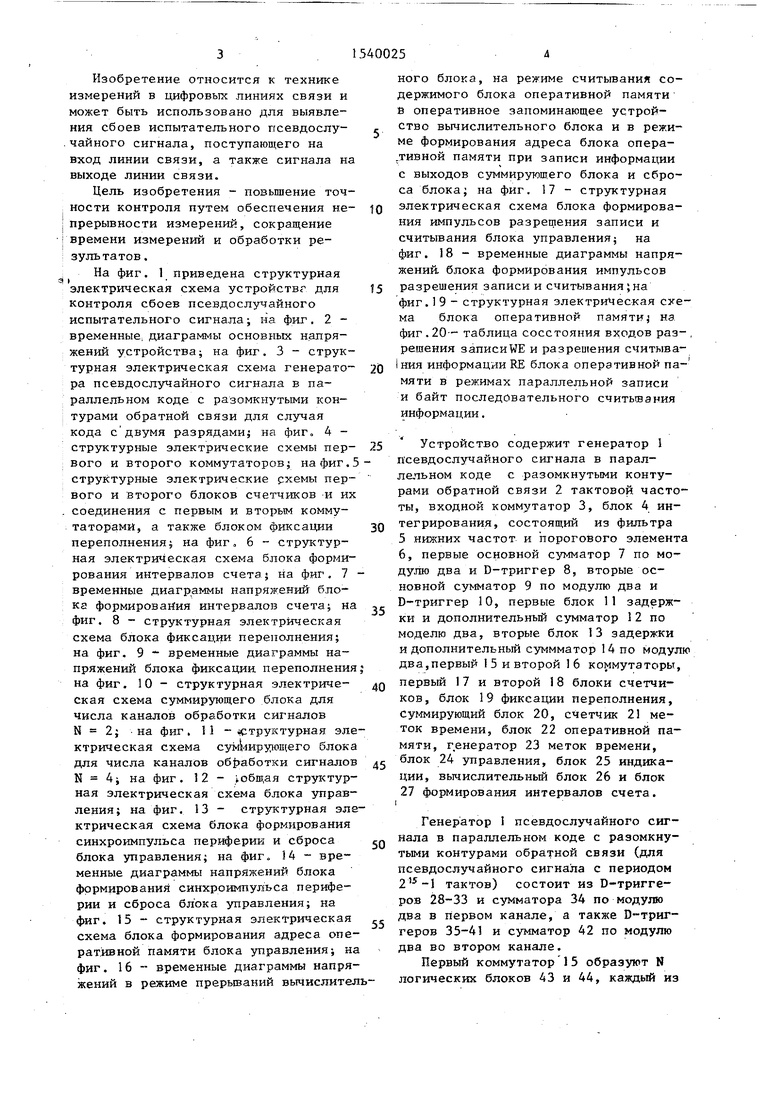

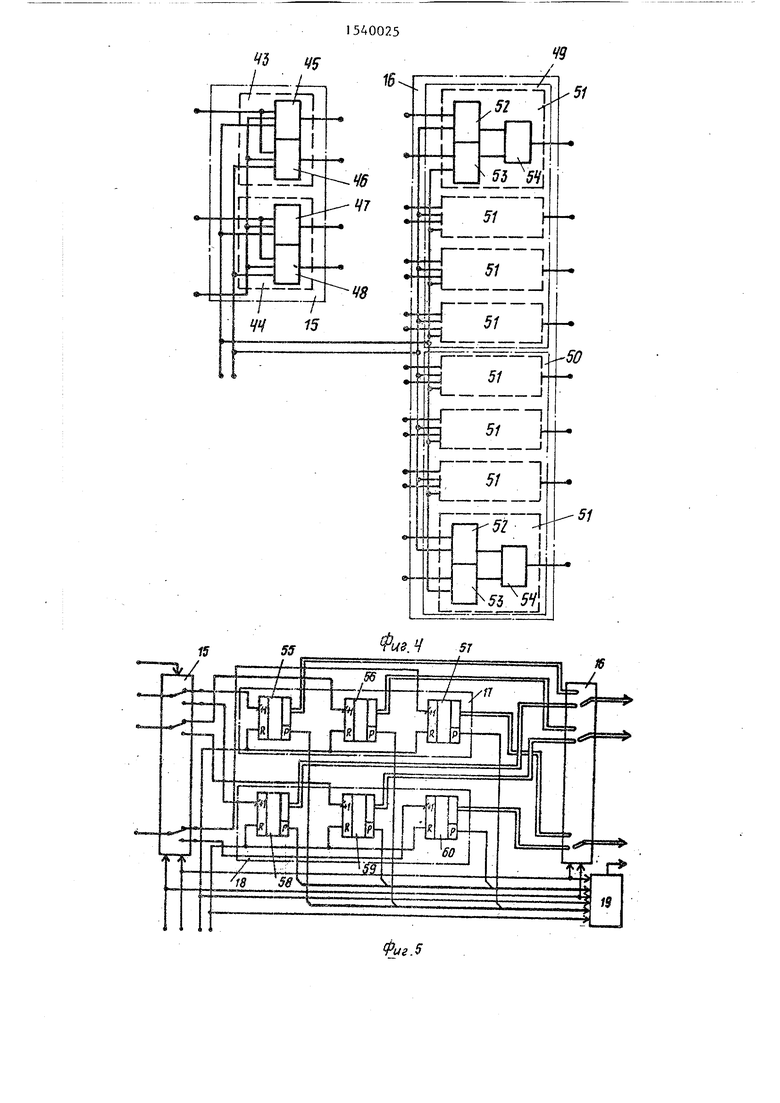

Импульсы сбоев в параллельном коде поступают на первый и второй сигнальные входы первого коммутатора I 5 и в зависимости от фазы напряжений коммутации счетчиков (фиг.8 б,в) на выходах управления коммутацией блока 27 формирования интервалов счета, поступающих на входы управления коммутацией первого коммутатора 15, появляются на его выходах, причем импульсы сбоев регистрируются I соответственно счетчиками 55 и 57 первого блока 17 счетчиков либо счетчиками 58 и 60 второго блока 18 счетчиков. Элементы И 45-48 первого коммутатора J 5 стробируются по входу напряжением полутактовой, частоты для того, чтобы при многократных сбоях счетчики фиксировали количество тактовых интервалов, соответствующих продолжительности сбоя.

Напряжения с выходов счетчиков 55 и 57 или 58 и 60 соответствующие количеству зарегистрированных сбоев, поступают через второй коммутатор 16 на входы суммирующего блока 20 в те моменты времени, когда счет импуль- сов не производится. В суммирующем блоке 20 происходит суммирование разрядов двоичных кодов чисел, соответствующих количеству импульсов сбоев, зарегистрированных в счетчиках групп, а также определение признака ненулевого результата.

Если результат суммирования на нулевой, то с помощью блока 24 управления происходит запись в блок 22 one- ративной памяти информации с выхода суммирующего блока 20, с выхода счетчика 21 меток времени, а также с выхода блока 19 фиксации переполнения групп счетчиков. Весь указанный объем информации записывается по последовательно увеличивающимся адресам блока 22 оперативной памяти. После записи информации в последнюю ячейку блока 22 оперативной памяти блок 24 управления формирует сигнал прерывания вычислительного блока 26. Под воздействием этого сигнала вычислительный блок 26 переписывает в свое оперативное запоминающее устройство со- держимое блока 26 оперативной памяти, после чего вычислительный блок 26 переходит к продолжению прерванного процесса обработки данных или регистрации результатов обработки в блоке 25 индикации, а в блок 22 оперативной памяти в следующем интервале измерений записывается информация о количестве зарегистрированных сбоев .

Обработка информации в вычисли- тельном блоке 26 заключается в преобразовании во внутренний формат данных о количестве сбоев, показаний счетчика меток времени, соответствующих моменту завершения очередного интервала измерений, а также бита переполнений групп счетчиков, единичное значение которого указывает, что количество сбоев за интервал

измерений превосходит максималъйую емкость счетчиков групп. Если такое явление происходит слишком часто,то это свидетельствует о необходимости уменьшения длительности интервала измерений сбоев. Нулевое значение бита переполнения свидетельствует, что пачка сбоев, укладывается по времени в интервал измерений, а со- ответствующее количество сбоев может в дальнейшем быть использовано при статической обработке результатов.

Дальнейшая обработка информации в вычислительном блоке 26 может заключаться в накоплении информации на внешнем накопителе в случае переполнения памяти оперативного запоминающего устройства вычислительного блока 26, подсчете доли интервалов измерений с ошибками (сбоями) и без них, подсчете средней частости сбоев, построении гистограммы количества сбоев, построении распределения количества сбоев в зависимости о времени суток.

Рассмотрим теперь более подробно особенности работы блока 27 формирования интервалов счета, блока 19 фиксации переполнения групп счетчиков и блока 24 управления.

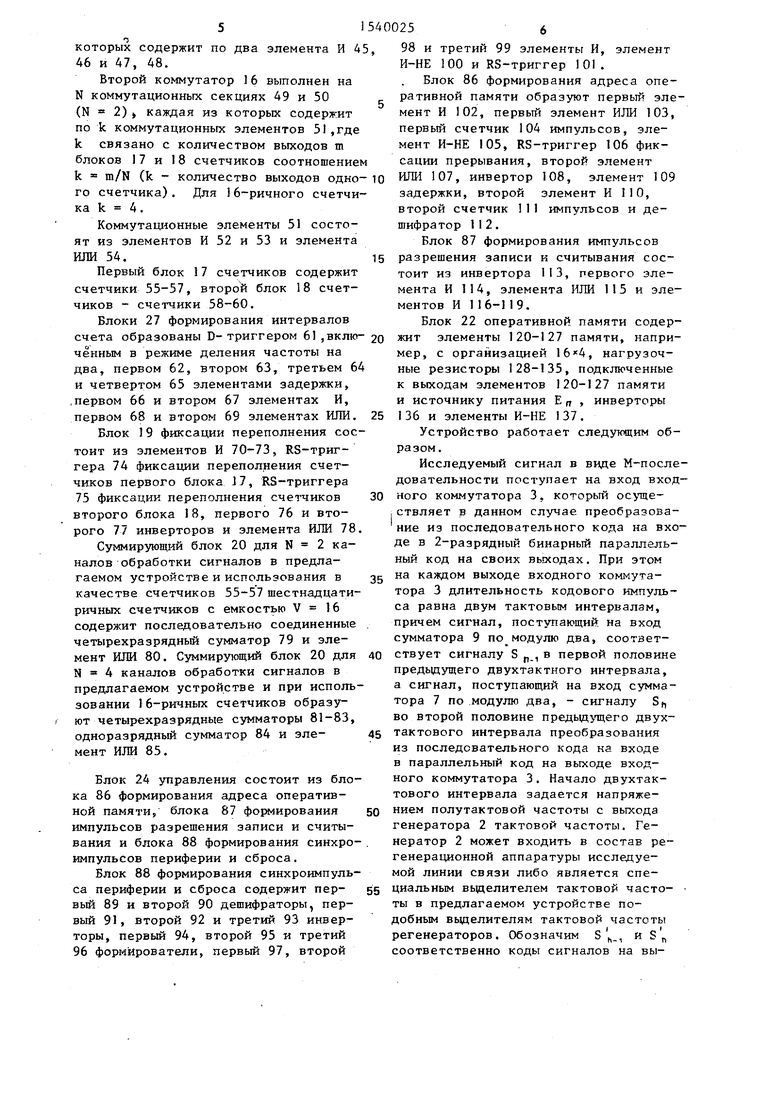

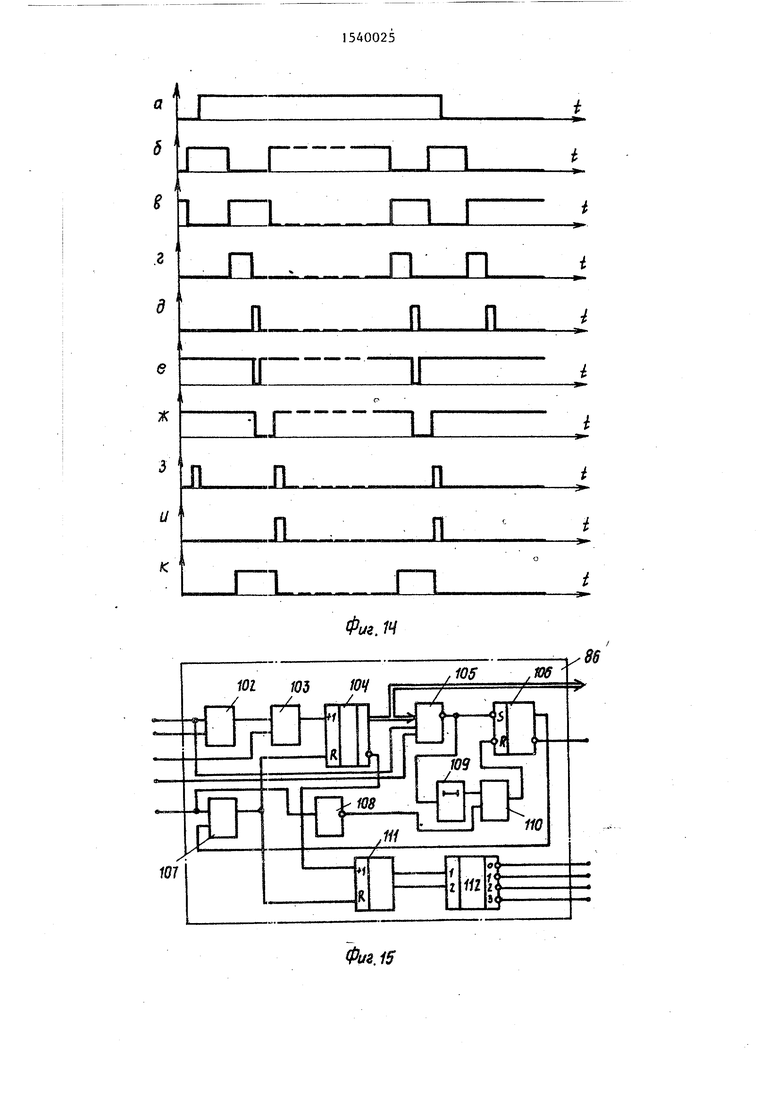

На вход блока формирования интервалов счета поступают импульсы меток времени (фиг.7а) с генератора 23 меток времени. I

D-триггер 61, включенный в режим деления частоты, вырабатывает напряжение коммутации счетчиков первого блока 17 (фиг.7б) и напряжение коммутации счетчиков второго блока 18 (фиг.7в). Благодаря последовательно включенным элементам 62-64 задержки на выходах формируются соответственно импульсы разрешения записи содержимого суммирующего блока 20 и выходного сигнала блока 19 фиксации переполнения в блок 22 оперативной памяти (фиг.7е), импульсы опроса переполнения счетчика адреса блок оперативной памяти (фиг.7з) и импульсы приращения содержимого счетчика адреса блока оперативной памяти (фиг.7ж). Для каждой из групп счетчиков формируется напряжения сброса (фиг.7г,д). Благодаря включению четвертого элемента 65 задержки импульс сброса формируются после того, как произошла запись информации в блок 9

13

оперативной памяти и выполнено изменение адреса блока 22 оперативной памяти с целью подготовки блока 22 для последующей фиксации результатов измерений. Кроме того, сброс счетчиков производится напряжением с блока 4 интегрирования по входу запрета, а также по входу сброса напряжением сброса с выхода сброса блока 24 управ- ления,поступающем в начале измерений при подготовке устройства к работе. Сброс блоков 1 7 и 18 счетчиков по входу запрета гарантирует,что не будет реги- страции пачек сбоев ,которые могут воз- никнуть из-за случайной рассинхрони- зации генератора 1 псевдослучайного сигнала по отношению к входной псевдслучайной последовательности.

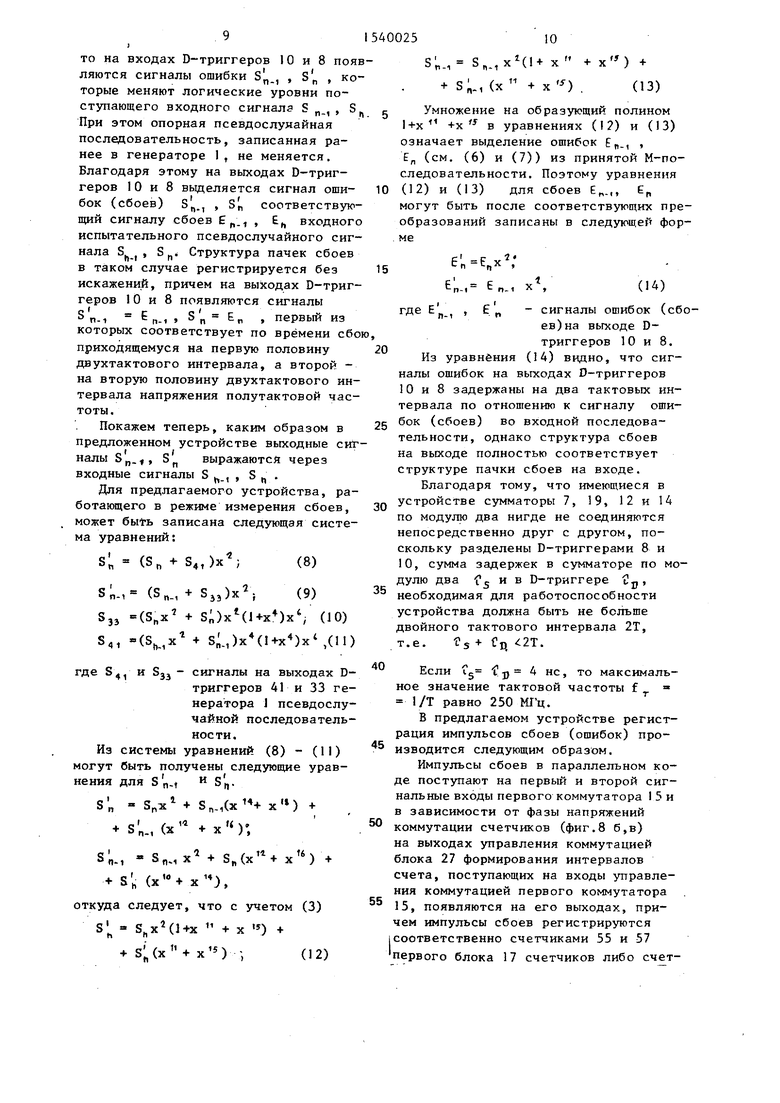

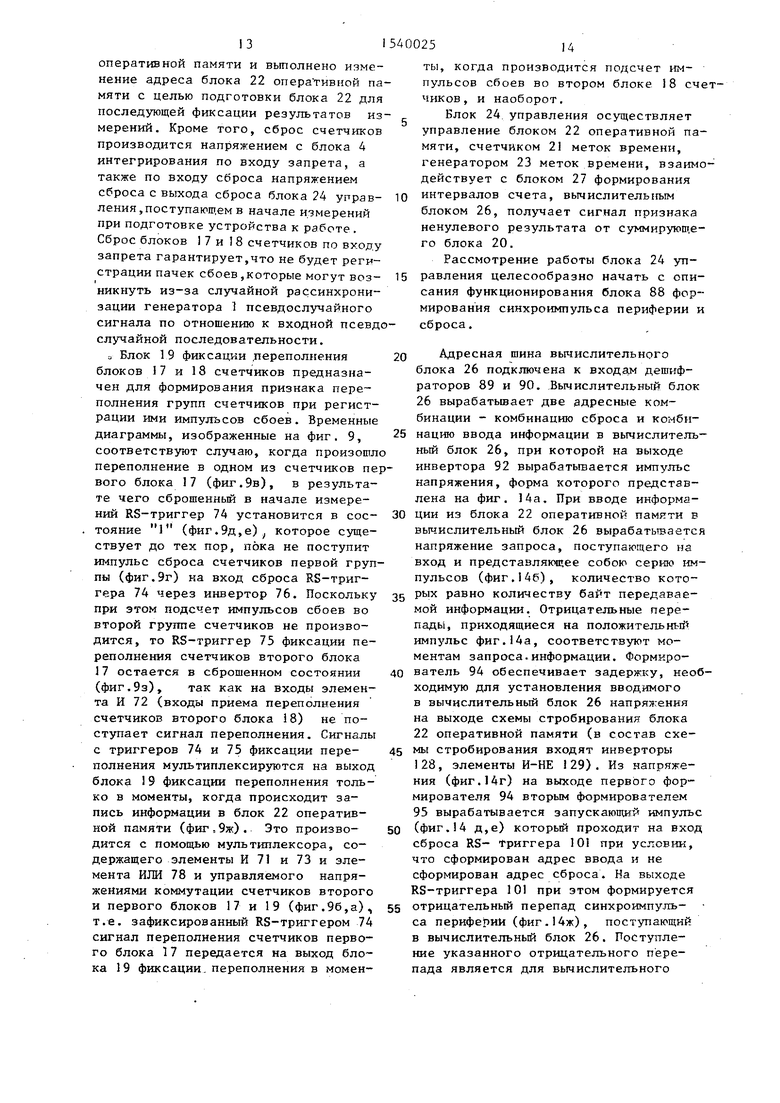

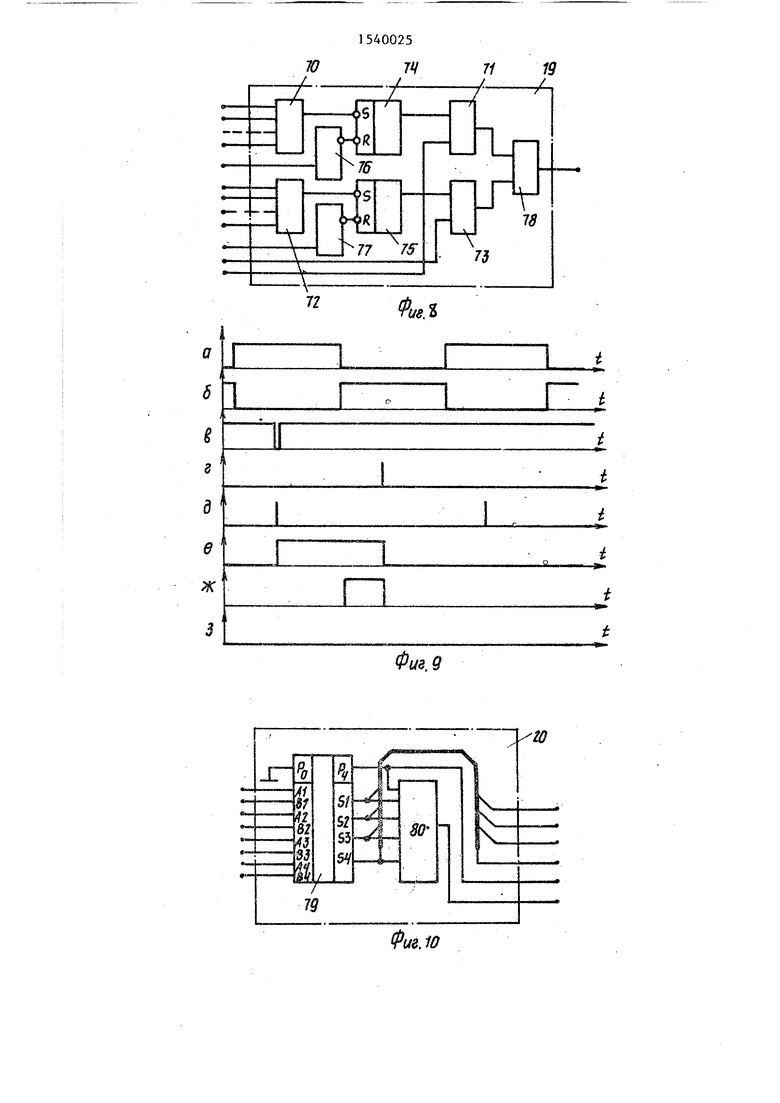

„ Блок 19 фиксации переполнения блоков 17 и 18 счетчиков предназначен для формирования признака переполнения групп счетчиков при регистрации ими импульсов сбоев. Временные диаграммы, изображенные на фиг. 9, соответствуют случаю, когда произошл переполнение в одном из счетчиков певого блока 17 (фиг.9в), в результате чего сброшенный в начале измерений RS-триггер 74 установится в сое-

тояние 1 (фиг.9д,е), которое существует до тех пор, пока не поступит импульс сброса счетчиков первой группы (фиг.Эг) на вход сброса RS-триг- гера 74 через инвертор 76. Поскольку при этом подсчет импульсов сбоев во второй группе счетчиков не производится, то RS-триггер 75 фиксации переполнения счетчиков второго блока 17 остается в сброшенном состоянии (фиг.9з), так как на входы элемента И 72 (входы приема переполнения счетчиков второго блока 18) не поступает сигнал переполнения. Сигналы с триггеров 74 и 75 фиксации пере- полнения мультиплексируются на выход блока 19 фиксации переполнения только в моменты, когда происходит запись информации в блок 22 оперативной памяти (фиг,9ж). Это произво- дится с помощью мультиплексора, содержащего элементы И 71 и 73 и элемента ИЛИ 78 и управляемого напряжениями коммутации счетчиков второго и первого блоков 17 и 19 (фиг.96,а), т.е. зафиксированный RS-триггером 74 сигнал переполнения счетчиков первого блока 17 передается на выход блока 19 фиксации переполнения в момен25

14

ты, когда производится подсчет импульсов сбоев во втором блоке 18 счечиков, и наоборот.

Блок 24 управления осуществляет управление блоком 22 оперативной памяти, счетчиком 21 меток времени, генератором 23 меток времени, взаимодействует с блоком 27 формирования интервалов счета, вычислительным блоком 26, получает сигнал признака ненулевого результата от суммирующего блока 20.

Рассмотрение работы блока 24 управления целесообразно начать с описания функционирования блока 88 формирования синхроимпульса периферии и сброса.

0 0

5

5 0 5 5

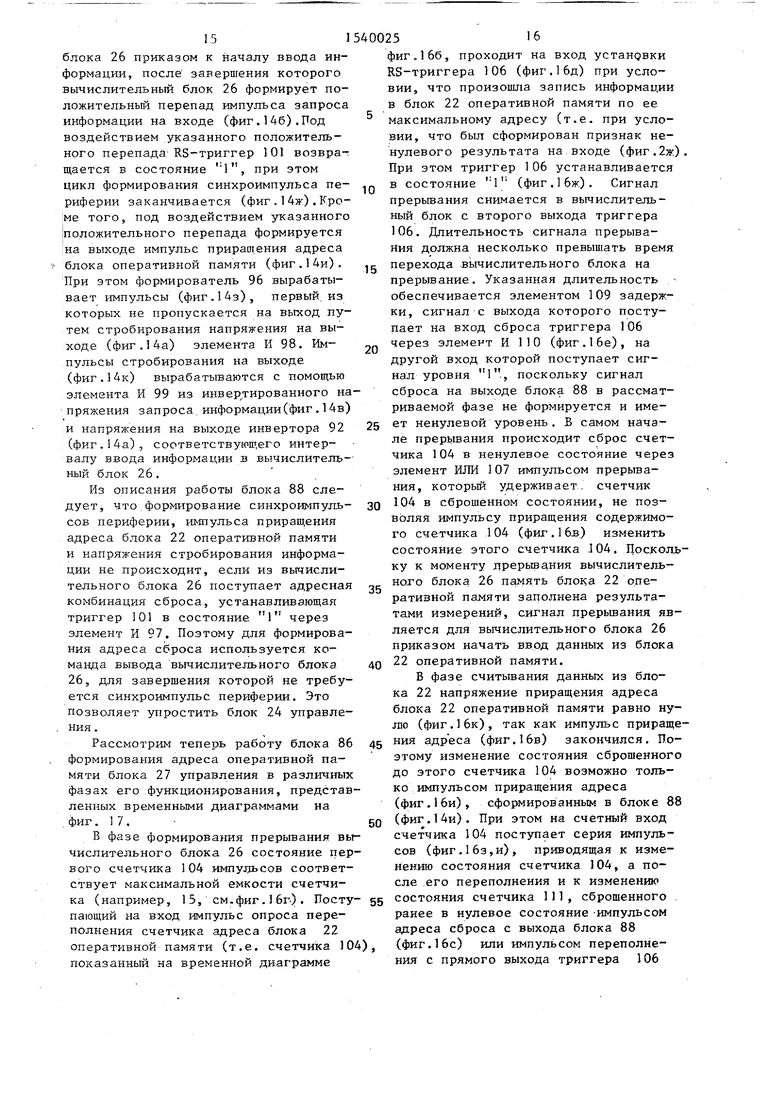

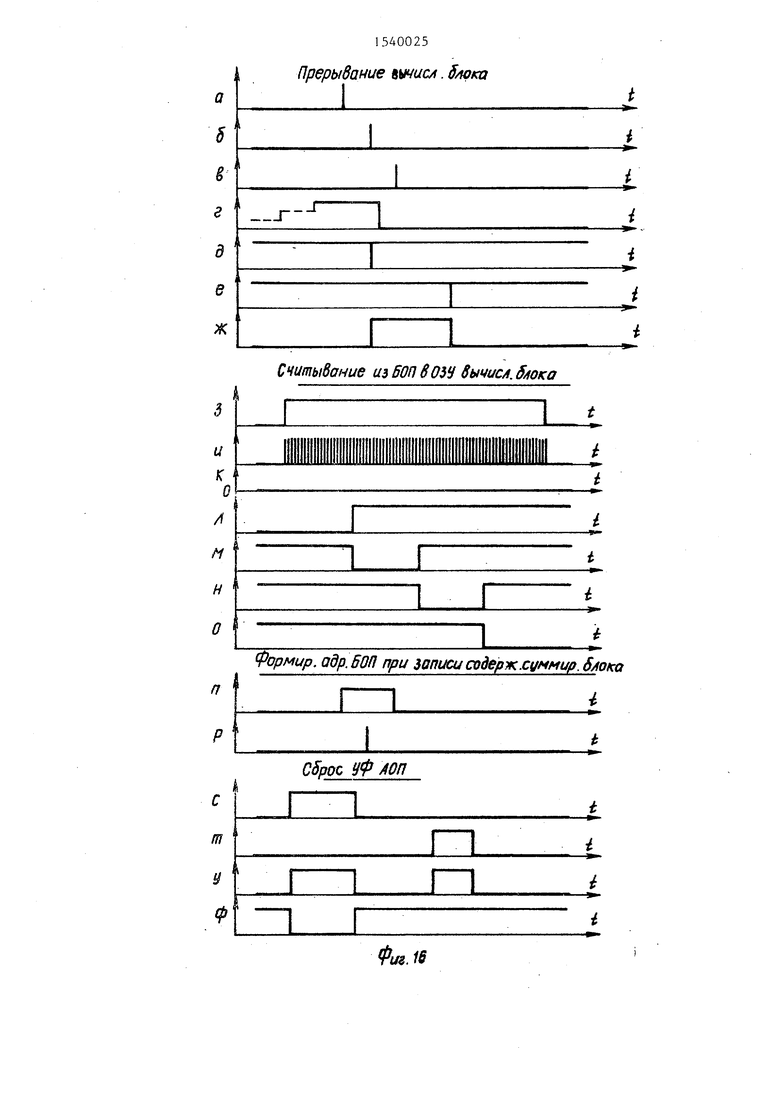

Адресная шина вычислительного блока 26 подключена к входам дешифраторов 89 и 90. Вычислительный блок 26 вырабатывает две адресные комбинации - комбинацию сброса и комбинацию ввода информации в вычислительный блок 26, при которой на выходе инвертора 92 вырабатывается импульс напряжения, форма которого представлена на фиг. 14а. При вводе информации из блока 22 оперативной памяти в вычислительный блок 26 вырабатывается напряжение запроса, поступающего на вход и представляющее собою серию импульсов (фиг.146), количество которых равно количеству байт передаваемой информации. Отрицательные перепады, приходящиеся на положит ель ный импульс фиг.14а, соответствуют моментам запроса.информации. Формирователь 94 обеспечивает задержку, необходимую для установления вводимого в вычислительный блок 26 напряжения на выходе схемы стробирования блока 22 оперативной памяти (в состав схемы стробирования входят инверторы 128, элементы И-НЕ 129). Из напряжения (фиг.14г) на выходе первого формирователя 94 вторым формирователем 95 вырабатывается запускающий импульс (фиг.14 д,е) который проходит на вход сброса RS- Триггера 101 при условии, что сформирован адрес ввода и не сформирован адрес сброса. На выходе RSтриггера 101 при этом формируется отрицательный перепад синхроимпуль- - са периферии (фиг.14ж), поступающий в вычислительный блок 26. Поступление указанного отрицательного перепада является для вычислительного

блока 26 приказом к началу ввода информации, после завершения которого вычислительный блок 26 формирует положительный перепад импульса запроса информации на входе (фиг.14б).Под воздействием указанного положительного перепада RS-триггер 101 возвращается в состояние , при этом цикл формирования синхроимпульса пе- риферии заканчивается (фиг.14ж).Кроме того, под воздействием указанного положительного перепада формируется на выходе импульс прирашения адреса блока оперативной памяти (фиг.14и). При этом формирователь 96 вырабатывает импульсы (фиг.14з), первый из которых не пропускается на выход путем стробирования напряжения на выходе (фиг.14а) элемента И 98. Им- пульсы стробирования на выходе (фиг.14к) вырабатываются с помощью элемента И 99 из инвертированного напряжения запроса информации(фиг. 14в) и напряжения на выходе инвертора 92 (фиг.14а), соответствующего интервалу ввода информации в вычислительный блок 26.

Из описания работы блока 88 следует, что формирование синхроимпуль- сов периферии, импульса прирашения адреса блока 22 оперативной памяти и напряжения стробирования информации не происходит, если из вычислительного блока 26 поступает адресная комбинация сброса, устанавливающая триггер 101 в состояние 1 через элемент И 97. Поэтому для формирования адреса сброса используется команда вывода вычислительного блока 26, для завершения которой не требуется синхроимпульс периферии. Это позволяет упростить блок 24 управления .

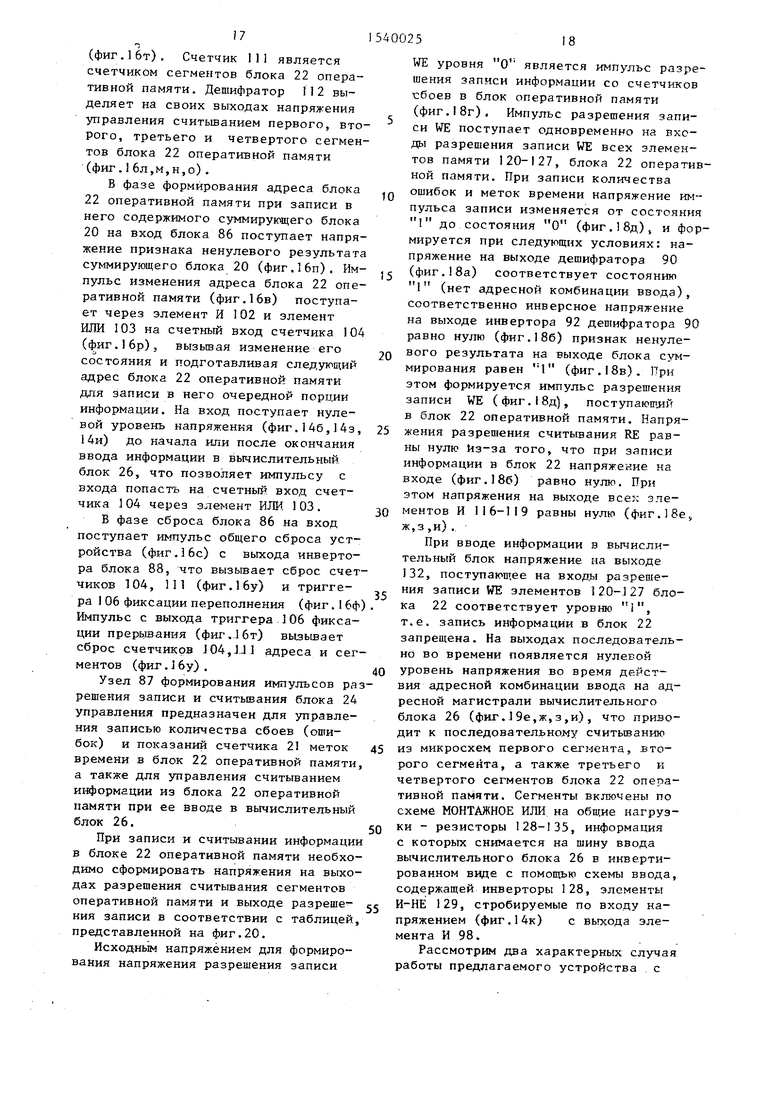

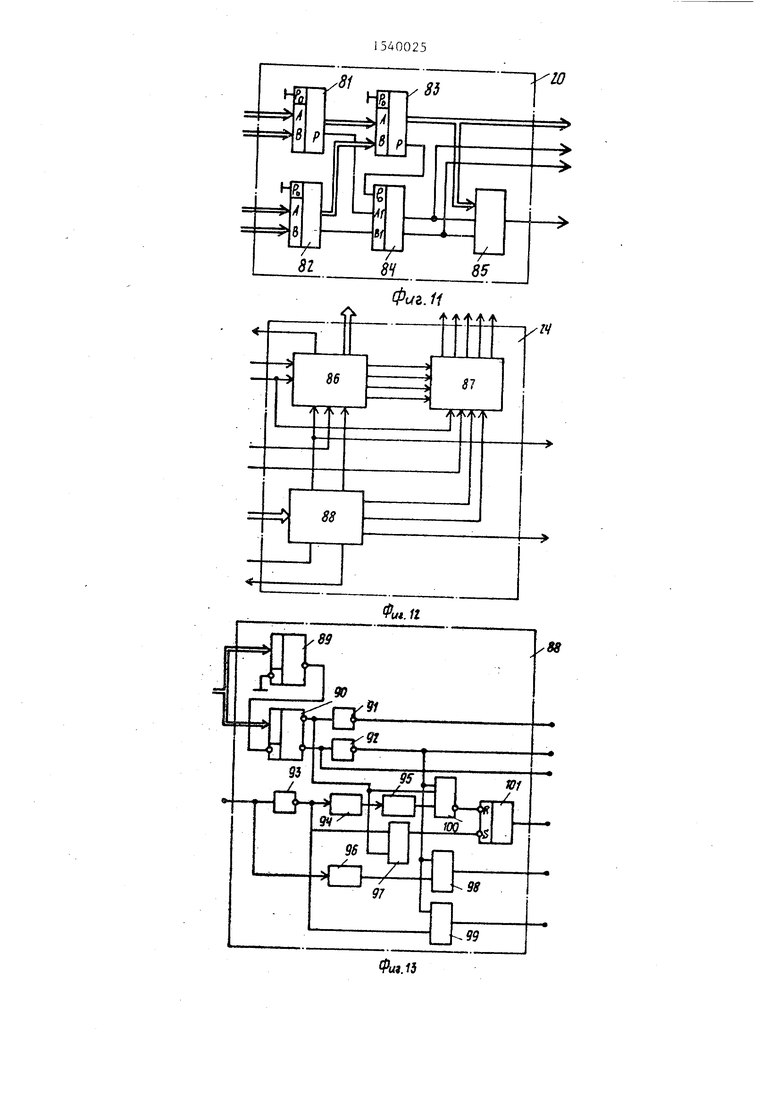

Рассмотрим теперь работу блока 86 формирования адреса оперативной памяти блока 27 управления в различных фазах его функционирования, представленных временными диаграммами на Фиг.17.

В фазе формирования прерывания вычислительного блока 26 состояние первого счетчика 104 импульсов соответствует максимальной емкости счетчика (например, 15, см.фиг.16г). Посту пающий на вход импульс опроса переполнения счетчика адреса блока 22 оперативной памяти (т.е. счетчика 10 показанный на временной диаграмме

фиг.16б, проходит на вход устандвки RS-триггера 106 (фиг.16д) при условии, что произошла запись информации в блок 22 оперативной памяти по ее максимальному адресу (т.е. при условии, что был сформирован признак ненулевого результата на входе (фиг.2ж При этом триггер 106 устанавливается в состояние (фиг.16ж). Сигнал прерывания снимается в вычислительный блок с второго выхода триггера 106. Длительность сигнала прерывания должна несколько превышать время перехода вычислительного блока на прерывание. Указанная длительность обеспечивается элементом 109 задержки, сигнал с выхода которого поступает на вход сброса триггера 106 через элемент И ПО (фиг. 1 бе), на другой вход которой поступает сигнал уровня I, поскольку сигнал сброса на выходе блока 88 в рассматриваемой фазе не формируется и имеет ненулевой уровень. В самом начале прерывания происходит сброс счетчика 104 в ненулевое состояние через элемент ИЛИ 107 импульсом прерывания, который удерживает счетчик 104 в сброшенном состоянии, не позволяя импульсу приращения содержимого счетчика 104 (фиг.16в) изменить состояние этого счетчика J04. Поскольку к моменту лрерьюания вычислительного блока 26 память блока 22 оперативной памяти заполнена результатами измерений, сигнал прерывания является для вычислительного блока 26 приказом начать ввод данных из блока 22 оперативной памяти.

В фазе считывания данных из блока 22 напряжение приращения адреса блока 22 оперативной памяти равно нулю (фиг.Збк), так как импульс приращения адреса (фиг.16в) закончился. Поэтому изменение состояния сброшенного до этого счетчика 104 возможно только импульсом приращения адреса (фиг.16и), сформированным в блоке 88 (фиг.14и). При этом на счетный вход счетчика 104 поступает серия импульсов (фиг.16з,и), приводящая к изменению состояния счетчика 104, а после его переполнения и к изменению состояния счетчика HI, сброшенного ранее в нулевое состояние импульсом адреса сброса с выхода блока 88 (фиг.16с) или импульсом переполнения с прямого выхода триггера 106

(фиг.16т). Счетчик 111 является счетчиком сегментов блока 22 оперативной памяти. Дешифратор 112 выделяет на своих выходах напряжения управления считыванием первого, второго, третьего и четвертого сегментов блока 22 оперативной памяти (фиг.16л,м,н,о) .

В фазе формирования адреса блока 22 оперативной памяти при записи в него содержимого суммирующего блока 20 на вход блока 86 поступает напряжение признака ненулевого результата суммирующего блока 20 (фиг.16п). Импульс изменения адреса блока 22 оперативной памяти (фиг.16в) поступает через элемент И 102 и элемент ИЛИ 103 на счетный вход счетчика 104 (фиг.16р), вызывая изменение его состояния и подготавливая следующий адрес блока 22 оперативной памяти для записи в него очередной порции информации. На вход поступает нулевой уровень напряжения (фиг.146,14з, i4и) до начала или после окончания ввода информации в вычислительный блок 26, что позволяет импульсу с входа попасть на счетный вход счетчика 104 через элемент ИЛИ 103.

В фазе сброса блока 86 на вход поступает импульс общего сброса устройства (фиг.36с) с выхода инвертора блока 88, что вызывает сброс счетчиков 104, ИЗ (фиг. 16у) и триггера 1 06 фиксации переполнения (фиг. 1 6ф) Импульс с выхода триггера 106 фиксации прерывания (фиг.16т} вызывает сброс счетчиков J04,J.1J адреса и сегментов (фиг. 1 6у} .

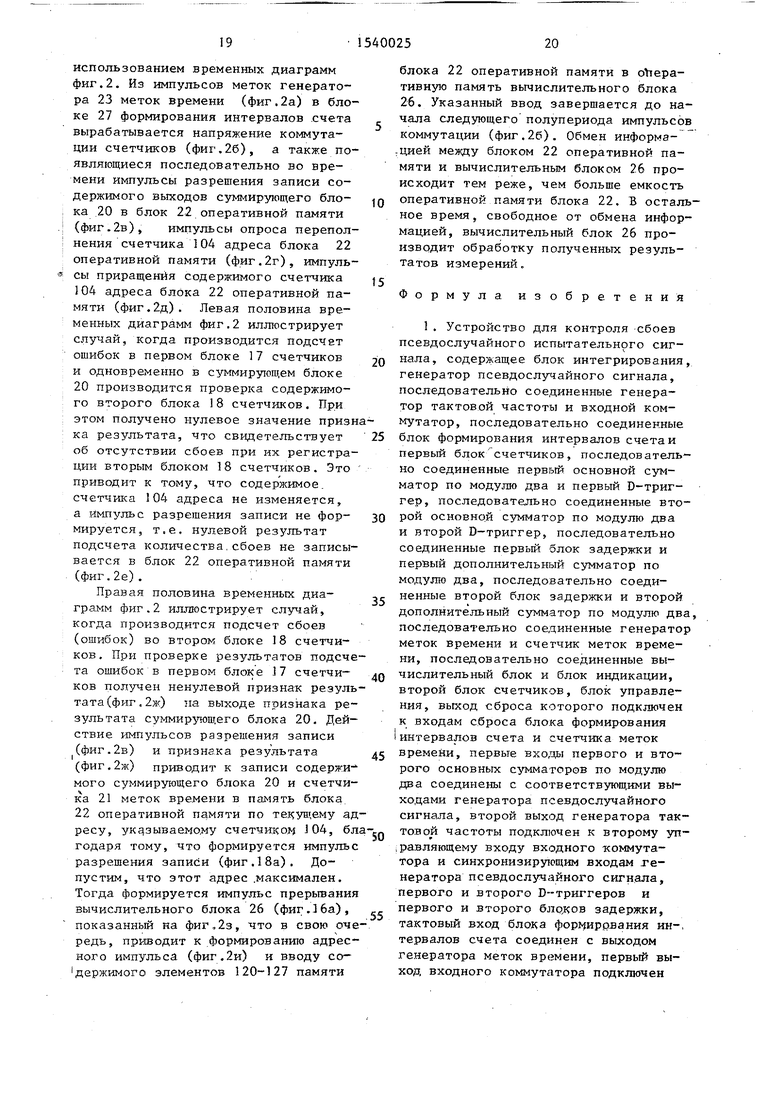

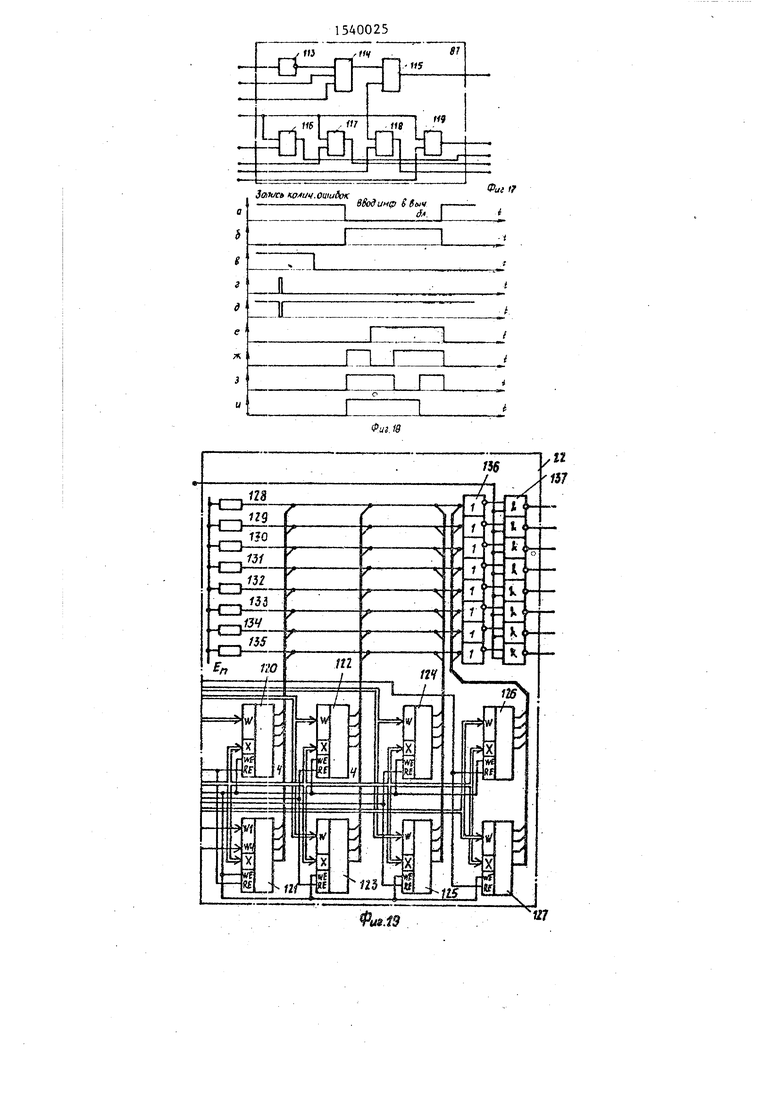

Узел 87 формирования импульсов разрешения записи и считывания блока 24 управления предназначен для управления записью количества сбоев (ошибок) и показаний счетчика 2 меток времени в блок 22 оперативной памяти, а также для управления считыванием информации из блока 22 оперативной памяти при ее вводе в вычислительный блок 26.

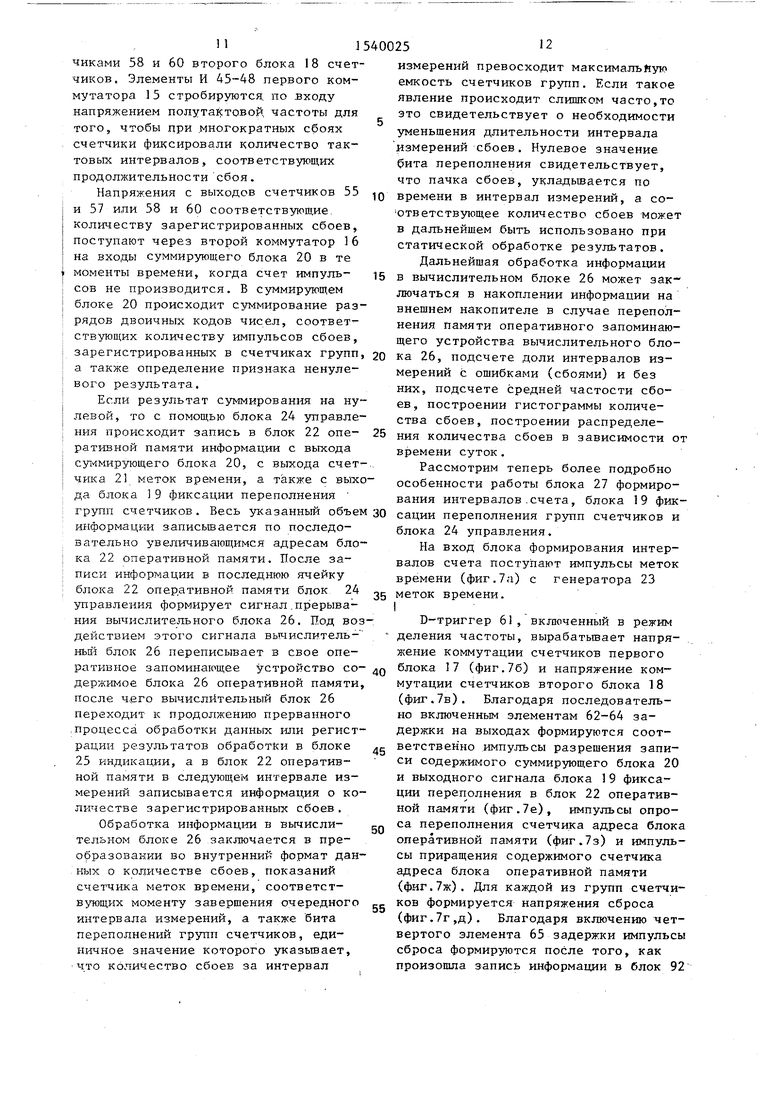

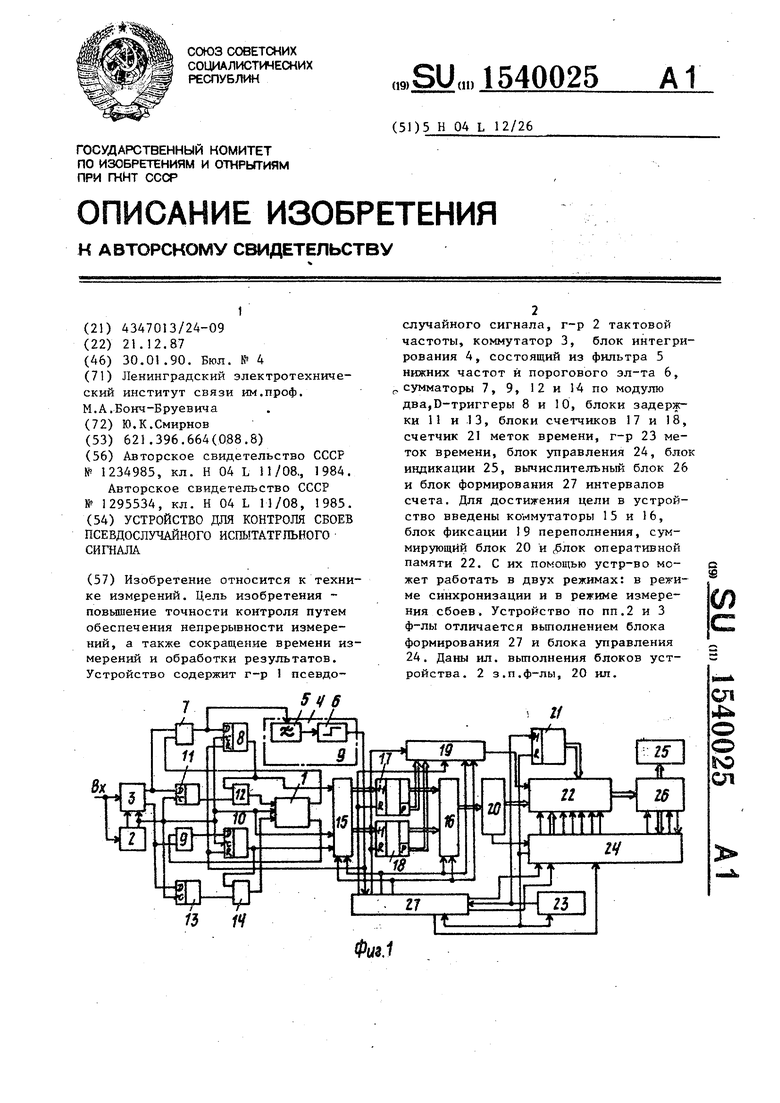

При записи и считывании информации в блоке 22 оперативной памяти необходимо сформировать напряжения на выходах разрешения считывания сегментов оперативной памяти и выходе разрешения записи в соответствии с таблицей, представленной на фиг.20.

Исходным напряжением для формирования напряжения разрешения записи

0

5

0

5

0

5

0

5

0

5

WE уровня О является импульс разрешения записи информации со счетчиков сбоев в блок оперативной памяти (фиг.18г). Импульс разрешения записи WE поступает одновременно на входы разрешения записи WE всех элементов памяти 120-127, блока 22 оперативной памяти. При записи количества ошибок и меток времени напряжение импульса записи изменяется от состояния 1 до состояния О (фиг.18д), и формируется при следующих условиях: напряжение на выходе дешифратора 90 (фиг.18а) соответствует состоянию I (нет адресной комбинации ввода), соответственно инверсное напряжение на выходе инвертора 92 дешифратора 90 равно нулю (фиг.18б) признак ненулевого результата на выходе блока суммирования равен (фиг.18в). При этом формируется импульс разрешения записи WE (фиг.18д), поступающий в блок 22 оперативной памяти. Напряжения разрешения считывания RE равны нулю из-за того, что при записи информации в блок 22 напряжение на входе (фиг.18б) равно нулю. При этом напряжения на выходе всех элементов И 116-119 равны нулю (фиг.18е, ж,з,и).

При вводе информации в вычислительный блок напряжение на выходе 132, поступающее на входы разрешения записи WE элементов 120-127 блока 22 соответствует уровню I, т.е. запись информации в блок 22 запрещена. На выходах последовательно во времени появляется нулевой уровень напряжения во время действия адресной комбинации ввода на адресной магистрали вычислительного блока 26 (фиг.19е,ж,з,и), что приводит к последовательному считыванию из микросхем первого сегмента, второго сегмента, а также третьего к четвертого сегментов блока 22 оперативной памяти. Сегменты включены по схеме МОНТАЖНОЕ ИЛИ на общие нагрузки - резисторы 128-135, информация с которых снимается на шину ввода вычислительного блока 26 в инвертированном виде с помощью схемы ввода, содержащей инверторы 128, элементы И-НЕ 129, стробируемые по входу напряжением (фиг.14к) с выхода элемента И 98.

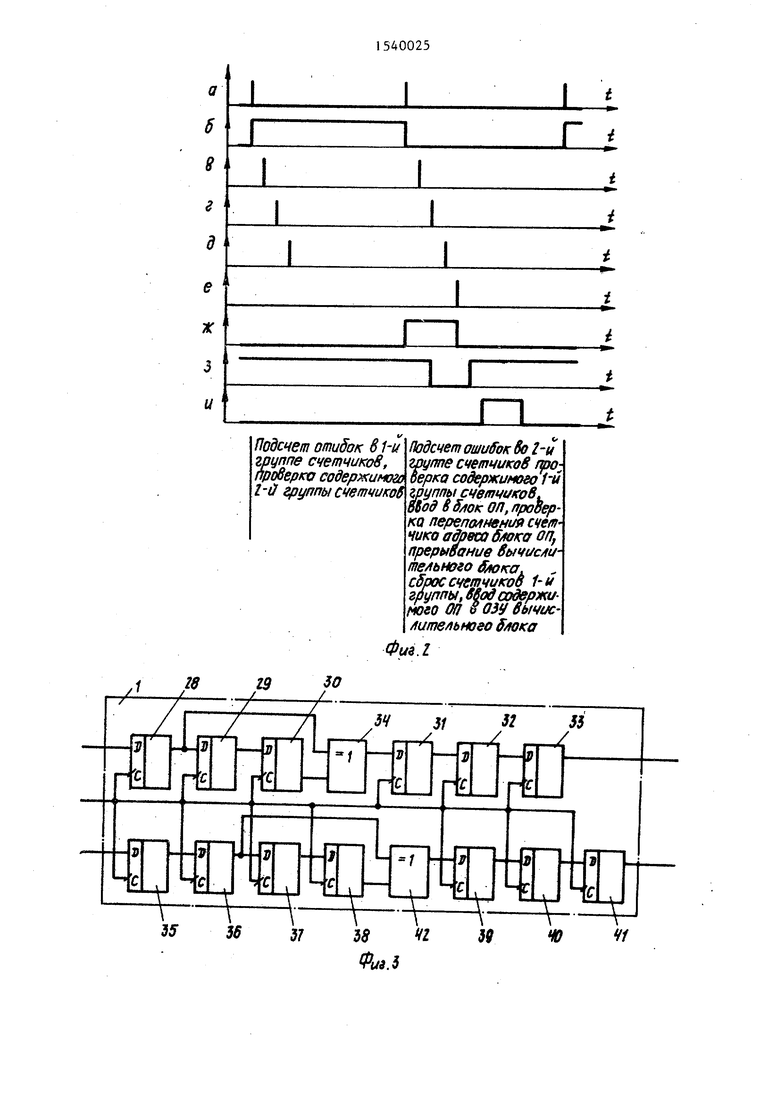

Рассмотрим два характерных случая работы предлагаемого устройства с

использованием временных диаграмм фиг.2. Из импульсов меток генератора 23 меток времени (фиг.2а) в блоке 27 формирования интервалов счета вырабатывается напряжение коммутации счетчиков (фиг.26), а также появляющиеся последовательно во времени импульсы разрешения записи содержимого ВЫХОДОВ СуММИруЮЩеГО бЛО- JQ

ка 20 в блок 22 оперативной памяти (фиг.2в), импульсы опроса переполнения счетчика 104 адреса блока 22 оперативной памяти (фиг.2г), импуль- сы приращения содержимого счетчика 104 адреса блока 22 оперативной памяти (фиг.2д). Левая половина временных диаграмм фиг.2 иллюстрирует случай, когда производится подсчет ошибок в первом блоке 17 счетчиков 20 и одновременно в суммирующем блоке 20 производится проверка содержимого второго блока 18 счетчиков. При этом получено нулевое значение признака результата, что свидетельствует 25 об отсутствии сбоев при их регистрации вторым блоком 18 счетчиков. Это приводит к тому, что содержимое счетчика 104 адреса не изменяется, а импульс разрешения записи не фор- 30 мируется, т.е. нулевой результат подсчета количества сбоев не записывается в блок 22 оперативной памяти (фиг.2е).

Правая половина временных диаграмм фиг.2 иллюстрирует случай, когда производится подсчет сбоев (ошибок) во втором блоке 18 счетчиков. При проверке результатов подсчета ошибок в первом блоке 17 счетчи- Q ков получен ненулевой признак результата (фиг.2ж) на выходе признака результата суммируюшего блока 20, Действие импульсов разрешения записи (фиг.2в) и признака результата 45 (фиг.2ж) приводит к записи содержи- мого суммирующего блока 20 и счетчика 21 меток времени в память блока 22 оперативной памяти по текущему адресу, указываемому счетчиков J04, бла- годаря тому, что формируется импульс разрешения записи (фиг.18а). Допустим, что этот адрес максимален. Тогда формируется импульс прерывания вычислительного блока 26 (фиг.Зба), ,е показанный на фиг.2з, что в свою очередь, приводит к формированию адресного импульса (фиг.2и) и вводу со- держимого элементов 120-127 памяти

35

0

Q 5 е

5

блока 22 оперативной памяти в оперативную память вычислительного блока 26. Указанный ввод завершается до начала следующего полупериода импульсов коммутации (фиг.2б). Обмен информацией между блоком 22 оперативной памяти и вычислительным блоком 26 происходит тем реже, чем больше емкость оперативной памяти блока 22. Б остальное время, свободное от обмена информацией, вычислительный блок 26 производит обработку полученных результатов измерений.

Формула изобретения

1. Устройство для контроля сбоев псевдослучайного испытательного сигнала, содержащее блок интегрирования, генератор псевдослучайного сигнала, последовательно соединенные генератор тактовой частоты и входной коммутатор, последовательно соединенные блок формирования интервалов счета и первый блок счетчиков, последователь- но соединенные первый основной сумматор по модулю два и первый D-триггер, последовательно соединенные второй основной сумматор по модулю два и второй D-триггер, последовательно соединенные первый блок задержки и первый дополнительный сумматор по модулю два, последовательно соединенные второй блок задержки и второй дополнительный сумматор по модулю два, последовательно соединенные генератор меток времени и счетчик меток времени, последовательно соединенные вычислительный блок и блок индикации, второй блок счетчиков, блок управления, выход сброса которого подключен к входам сброса блока формирования I интервалов счета и счетчика меток времени, первые входы первого и второго основных сумматоров по модулю два соединены с соответствующими выходами генератора псевдослучайного сигнала, второй выход генератора тактовой частоты подключен к второму управляющему входу входного коммутатора и синхронизирующим входам генератора псевдослучайного сигнала, первого и второго D-триггеров и первого и второго блоков задержки, тактовый вход блока формирования интервалов счета соединен с выходом генератора меток времени, первый выход входного коммутатора подключен

к второму входу второго основного сумматора по модулю два и к сигнальному входу второго блока задержки, второй выход входного коммутатора подключен к второму входу первого основного сумматора по модулю два и к сигнальному входу первого блока задержки, выходы первого и второго D-триггеров подключены соответственно к вторым входам первого и второго дополнительных сумматоров по модулю два, выходы которых подключены к соответствующим входам генератора псевдослучайного сигнала, выход первого основного сумматора по модулю два подключен к входу блока интегрирования, выход которого подключен к входам сброса первого и второго D-триггеров, адресные выходы, выход запроса и вход приема синхроимпульса вычислительного блока соединены соответственно с адресными входами, входом запроса и выходом синхроимпульса блока управления, отличающееся тем, что, с целью повышения точности контроля путем обеспечения непрерывности измерений, сокращения времени измерений и обработки результатов, в него введены первый коммутатор, соединенные последовательно второй коммутатор, суммирующий блок и блок оперативной памяти, блок фиксации переполнения, выход прерывания блока управления соединен с входом прерывания вычислительного блока, выход блока интегрирования соединен с входом запрета блока формирования интервалов счета, тактовый вход первого коммутатора соединен с вторым выходом генератора тактовой частоты, выход сброса блока управления подключен к входу сброса генератора меток времени, выход стробирования информации, выходы адресной шины, выходы разрешения считывания сегментов оперативной памяти, выход разрешения записи блока управления подключены соответственно к входу стробирования информации входам адресной шины, входам разрешения считывания сегментов оперативной памяти и входу разрешения записи блока оперативной памяти, вход фиксации переполнения и информационные выходы которого подключены соот- ветственно к выходу блока фиксации переполнения и входам информационной шины вычислительного блока, информа

ционные выходы счетчика меток времени соединены с входами регистрации времени блока оперативной памяти, выход признака ненулевого результата суммирующего блока соединен с входом приема признака ненулевого результата блока управления, вход разрешения записи, вход опроса, вход приращения адреса блока управления подключены

5

0

соответственно к выходам разрешения записи, опроса и приращения адреса блока формирования интервалов счета, первый и второй выходы управления

с коммутацией которого подключены соответственно к первому и второму входам управления первого коммутатора, второго коммутатора и блока фиксации переполнения, выходы сброса блока

Q формирования интервалов счета соединены соответственно с входом сброса второго блока счетчиков, с первым и вторым входами сброса блока фиксации переполнения, к входам приема сиг5 налов переполнения которого подключены соответствующие выходы переполнения первого и второго блоков счетчиков, счетные входы которых подключены к соответствующим выходам пер0 вого коммутатора, а информационные выходы подключены к соответствующим входам второго коммутатора, выходы первого и второго D-триггеров подключены к соответствующим сигнальным входам первого коммутатора, а третий вход входного коммутатора соединен с входом генератора тактовой частоты и является входом устройства.

2. Устройство по п. 1, о т л и ц чающееся тем, что блок формирования интервалов счета содержит соединенные последовательно D-триггер, первый элемент И и первый элемент ИЛИ, соединенные последовательно пер5 вый,второй,третий,четвертый элементы задержки,второй элемент И и второй элемент ИЛИ, причем выход четвертого элемента задержки соединен с вторым входом первого элемента И, вход первого элемента задержки соединен с входе -м синхронизации D-триггера и является тактовым входом блока формирования интервалов счета, второй вход второго элемента И соединен с прямым выходом D-триггера и являе ся первым выходом управления коммутацией блока формирования интервалов счета, вторые входы первого и второго элементов ИЛИ соединены и являются входом

запрета блока формирования интервалов счета, третьи входы первого и вто- i

рого элементов ИЛИ соединены и являются входом сброса блока формирования интервалов счета, инверсный выход D-триггера соединен с его D-вхо- дом и является вторым выходом управг- ления коммутацией блока формирования интервалов счета, а выходы первого и второго элементов ИЛИ, первого, второго и третьего элементов задержки являются соответственно выходами сброса,.выходами разрешения записи, опроса, приращения адреса блока формирования интервалов счета. i

3. Устройство по п. отличающееся тем, что блок управления содержит блок формирования адреса оперативной памяти и блок формирования импульсов разрешения записи и считывания, соединенные последовательно, блок формирования синхроимпульсов периферии и сброса, выход сброса которого соединен с входом сброса блока формирования адреса оперативной памяти и является выходом сброса блока управления, причем выход приращения адреса оперативной памяти блока формирования синхроимпульса периферии и сброса, а также выход прямого напряжения адреса ввода и выход инверсного напряжения адреса ввода соединены соответственно с входом приращения адреса оперативной

памяти блока формирования адреса оперативной памяти, входами прямого и инверсного напряжений адреса ввода блока формирования, импульсов разрешения записи и считывания, входы приема признака ненулевого результата блока формирования адреса оперативной памяти и блока формирования импульсов разрешения записи и считывания соединены и являются входом приема признака ненулевого результата блока управления, вход опроса переполнения счетчика адреса оперативной памяти, вход прира5 щения, выход прерывания и выходы адресной шины блока формирования адреса оперативной памяти являются соответственно входом опроса, входом приращения адреса, выходом прерывания

0 и выходами адресной шины блока управления, адресные входы, вход запроса, выход стробирования, выход синхро- Р импульса блока формирования синхроимпульса -периферии и сброса явля5 ются соответственно адресными выходами, входом запроса, выходом стробирования и выходом синхроимпульса блока управления, а вход и выход разрешения записи и выходы разрешения считы0 вания сегментов оперативной памяти блока формирования импульсов разрешения записи и считывания являются соответственно входом и выходом раз- решения записи и выходами разрешения

5 считывания сегментов оперативной памяти блока управления.

0 к

49

2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1984 |

|

SU1234985A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| УСТРОЙСТВО ВЫБОРА ОПТИМАЛЬНОГО МАРШРУТА МАНЕВРА | 1992 |

|

RU2045773C1 |

Изобретение относится к технике измерений. Цель изобретения - повышение точности контроля путем обеспечения непрерывности измерений, а также сокращение времени измерений и обработки результатов. Устройство содержит г-р 1 псевдослучайного сигнала, г-р 2 тактовой частоты, коммутатор 3, блок интегрирования 4, состоящий из фильтра 5 нижних частот и порогового эл-та 6, сумматоры 7,9,12 и 14 по модулю два, D-триггеры 8 и 10, блоки задержки 11 и 13, блоки счетчиков 17 и 18, счетчик 21 меток времени, г-р 23 меток времени, блок управления 24, блок индикации 25, вычислительный блок 26 и блок формирования 27 интервалов счета. Для достижения цели в устройство введены коммутаторы 15 и 16, блок фиксации 19 переполнения, суммирующий блок 20 и блок оперативной памяти 22. С их помощью устройство может работать в двух режимах: в режиме синхронизации и в режиме измерения сбоев. Устройство по пп.2 и 3 ф-лы отличается выполнением блока формирования 27 и блока управления 24. Даны ил. выполнения блоков устройства. 2 з.п. ф-лы, 20 ил., 1 табл.

55

Фиг. Ч 57

Фиг.5

1

+я

1

С Ж 9

Q В

8 9

Ј300 К

п

П

г

а

е

ж

3

1540025

14

7119

/

Фие.Ъ

Фиг. 9

Риг. Ю

Л/

10

фцг. 11

а

6

JL

ТТЛ

л

п

I

ш

п

п

и

п

гп

Фиг. IS

Г

л п

лп

1

п

п

Фиг. П

1540025

Прерывание twuu. блока

Т

г

Считывание из 60П в ОМ вычисл. блока

н

н

о

1

Формир. адр.ВОП при записи содерж.суммир. блока

Сирое УФ АОП

У

L

i

-

1

де

Фиг. IS

РЩД

Зотх колич ошибок

г д е ж 3 и

$ (ыч дл

ГП

Pua.20

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1984 |

|

SU1234985A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР S- 1295534, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-01-30—Публикация

1987-12-21—Подача