ИЛИ, RS-T привязки, D-T, два эл- та , эл-т . работает в режимах: 1) режим синхронизации, когда D-T 8 и 10 сброшены в нулевое состояние импульсом, сформированным на выходе эл-та 6; 2) режим

Изобретение относится к технике измерений в цифровых линиях связи и может быть использовано для выявления сбоев испытательного псевдослучайного сигнала, поступающего на вход линии связи, а также на выходе линии связи, в частности оно предназначено для линий связи со скоростью свьппе 140 Мбит/с, в которых не могут быть использованы технические средства менее скоростных линий связи и-за их недостаточного быстродействия.

Цель изобретения - повышение точности контроля.

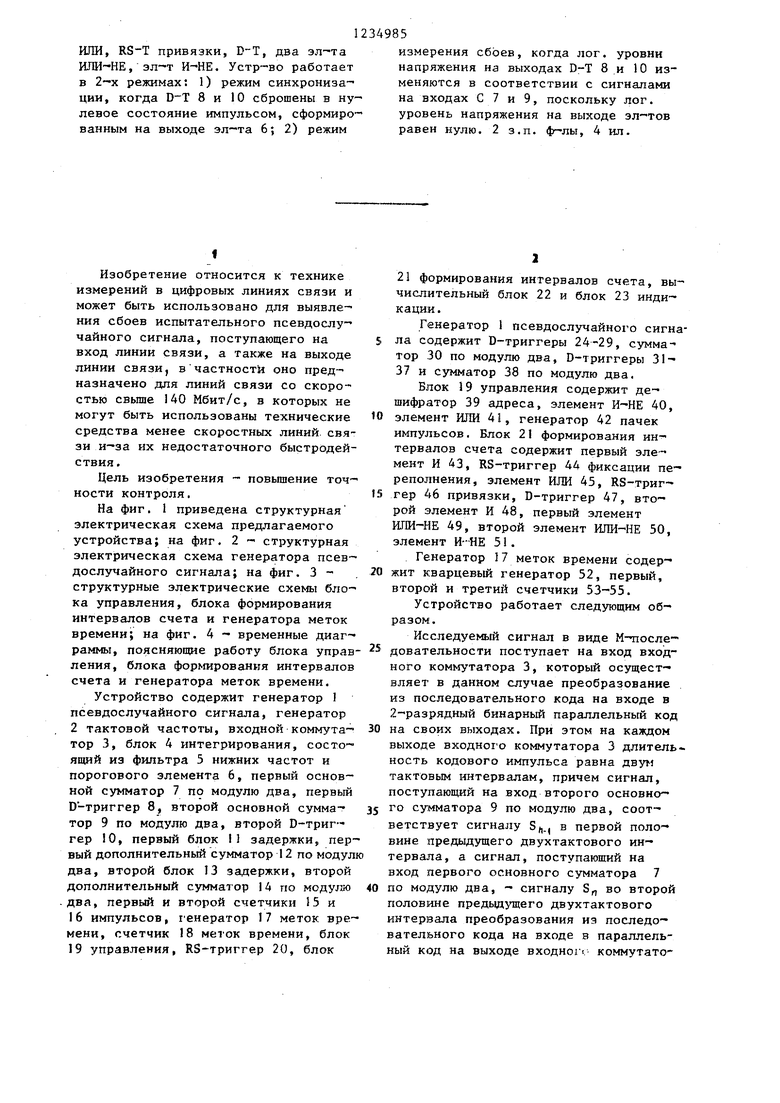

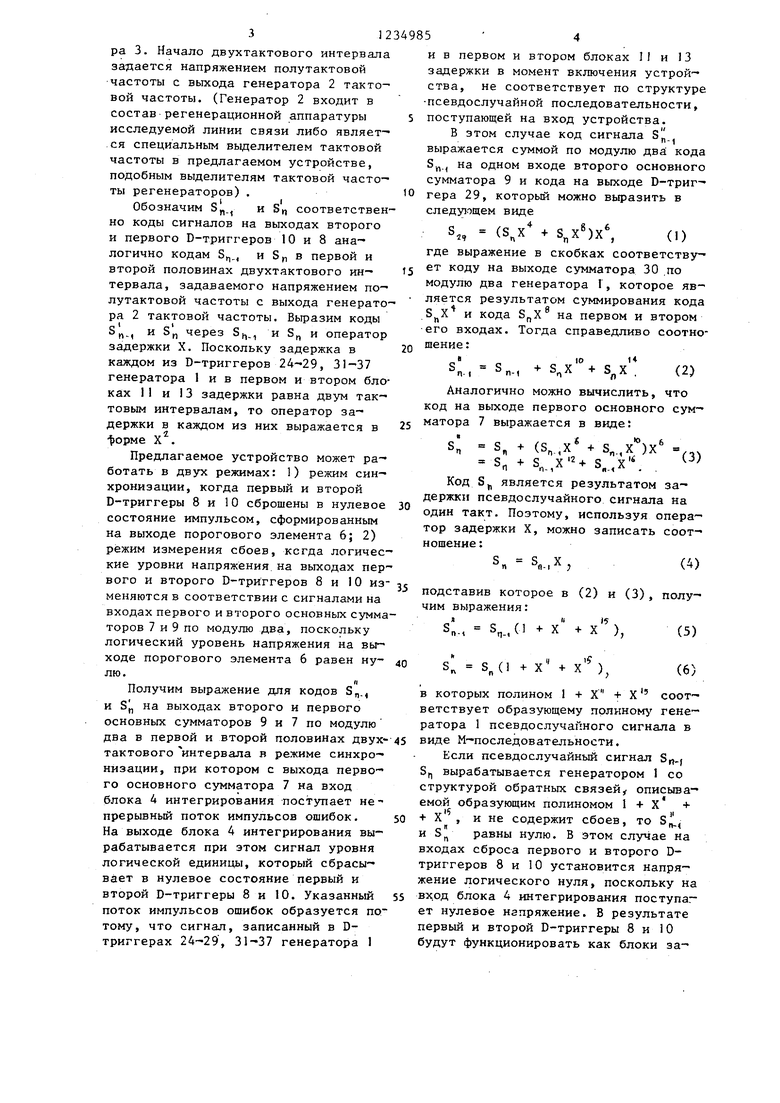

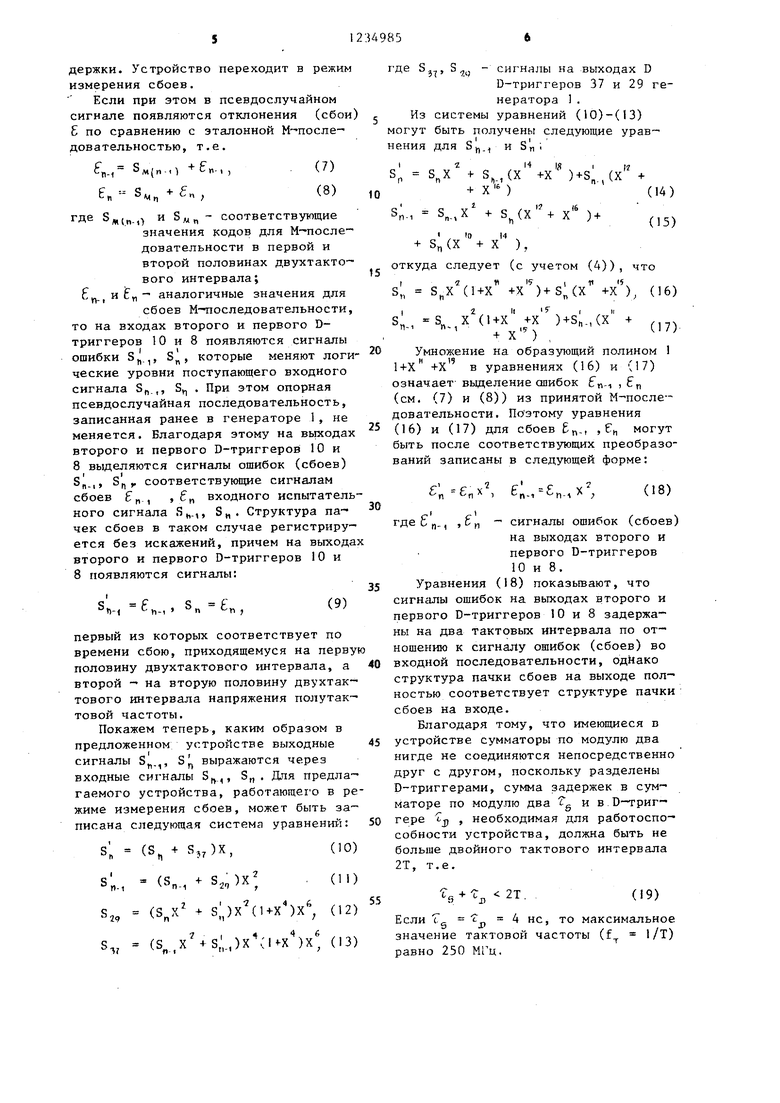

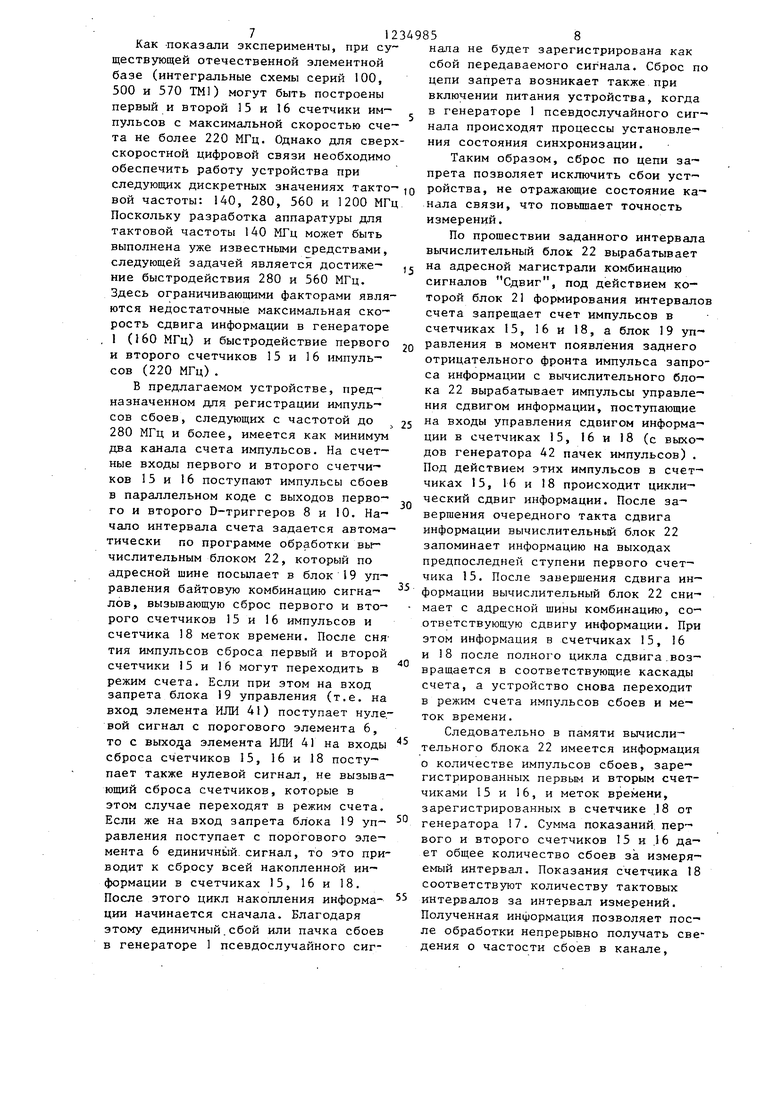

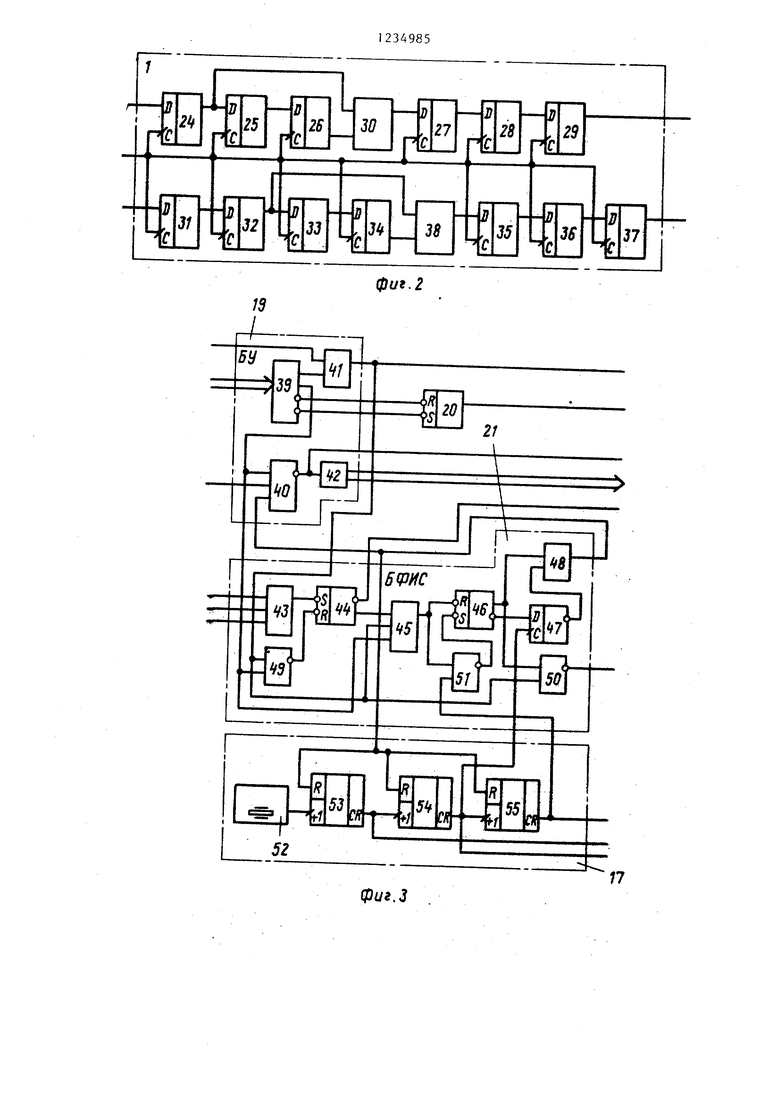

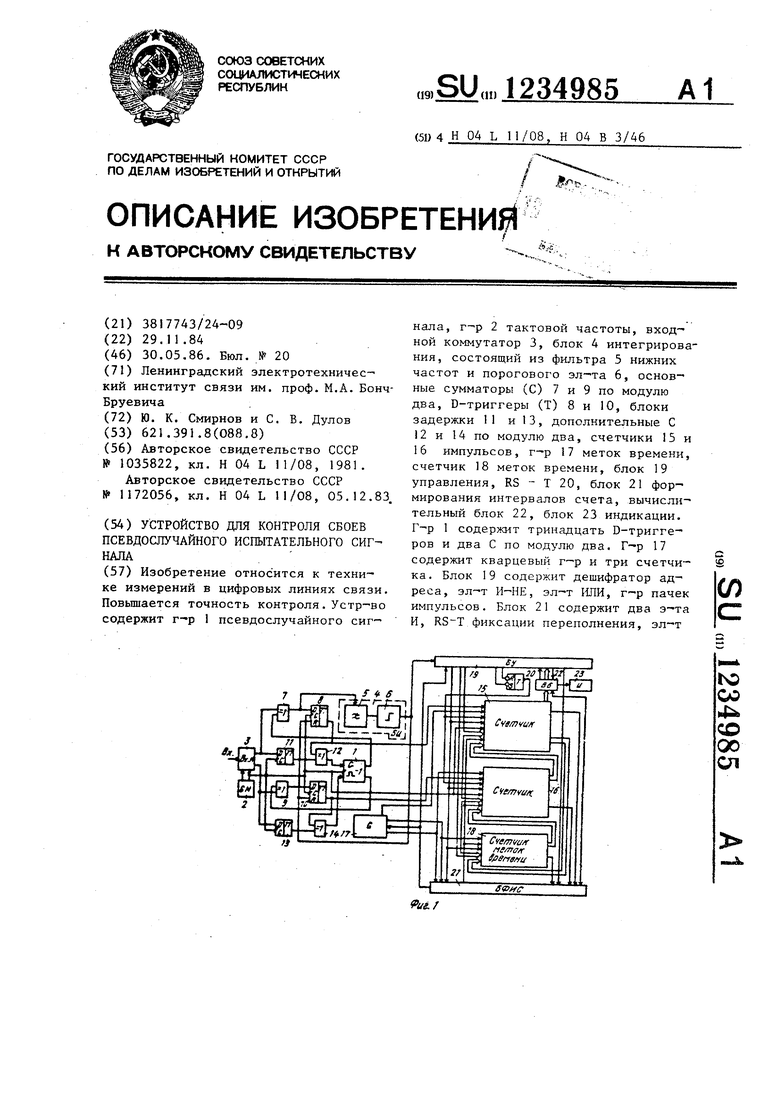

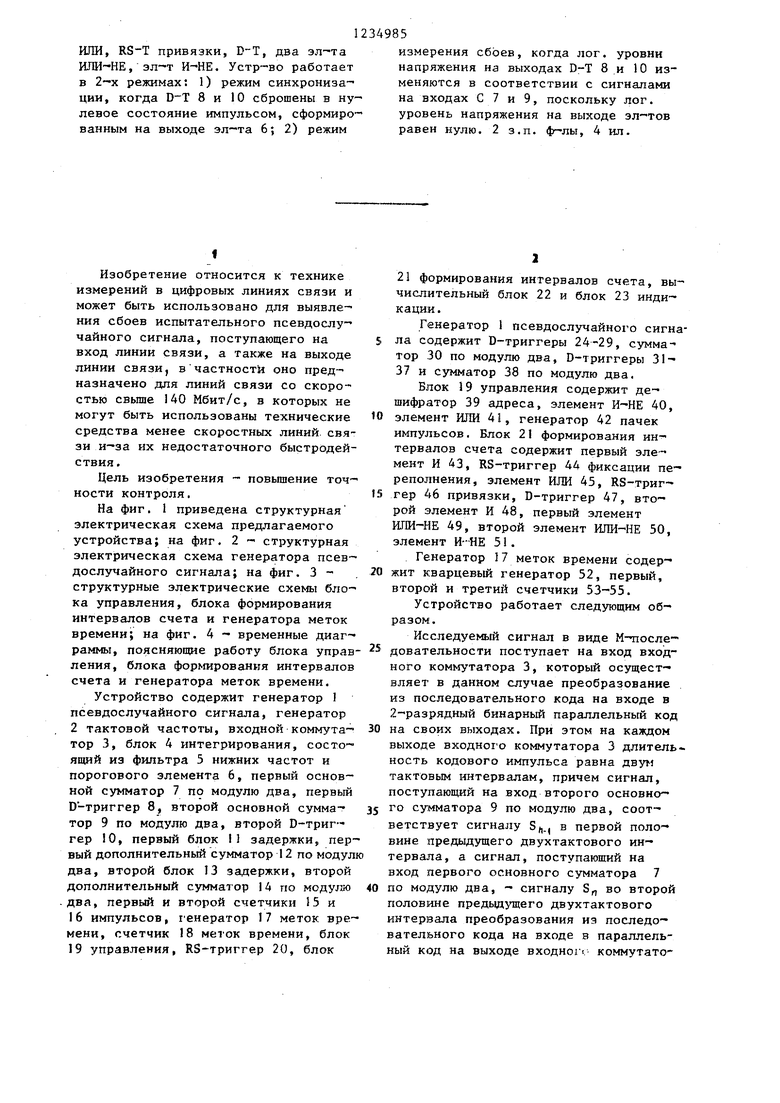

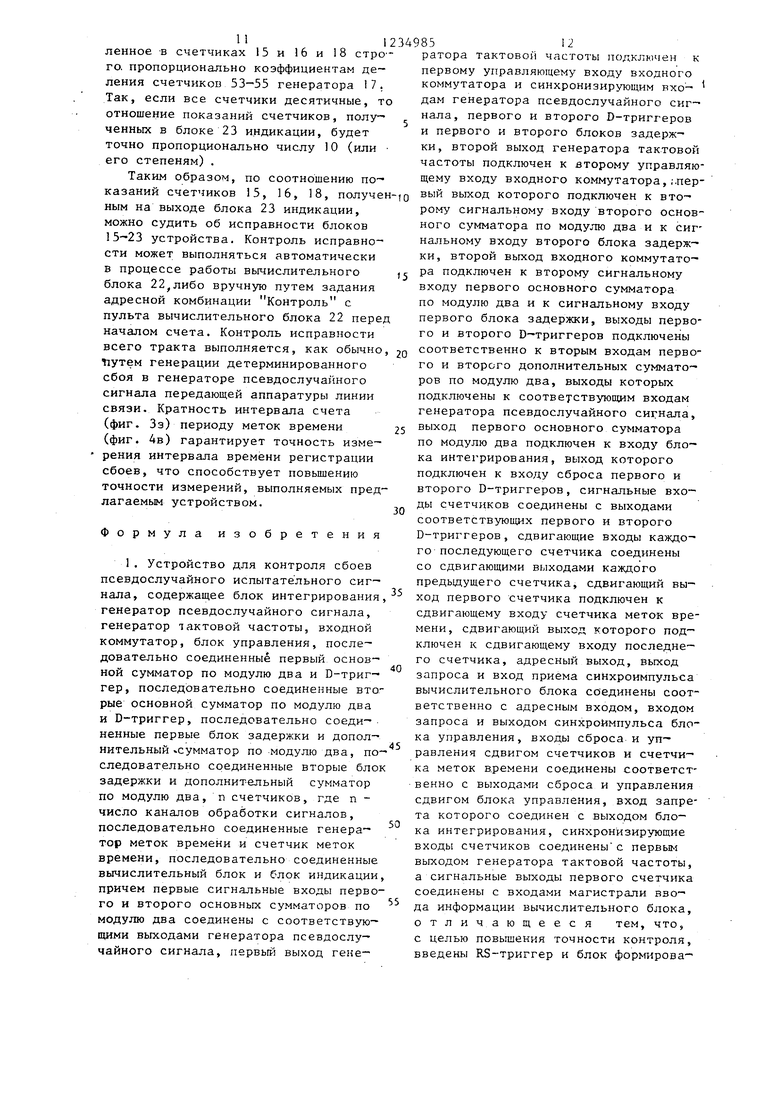

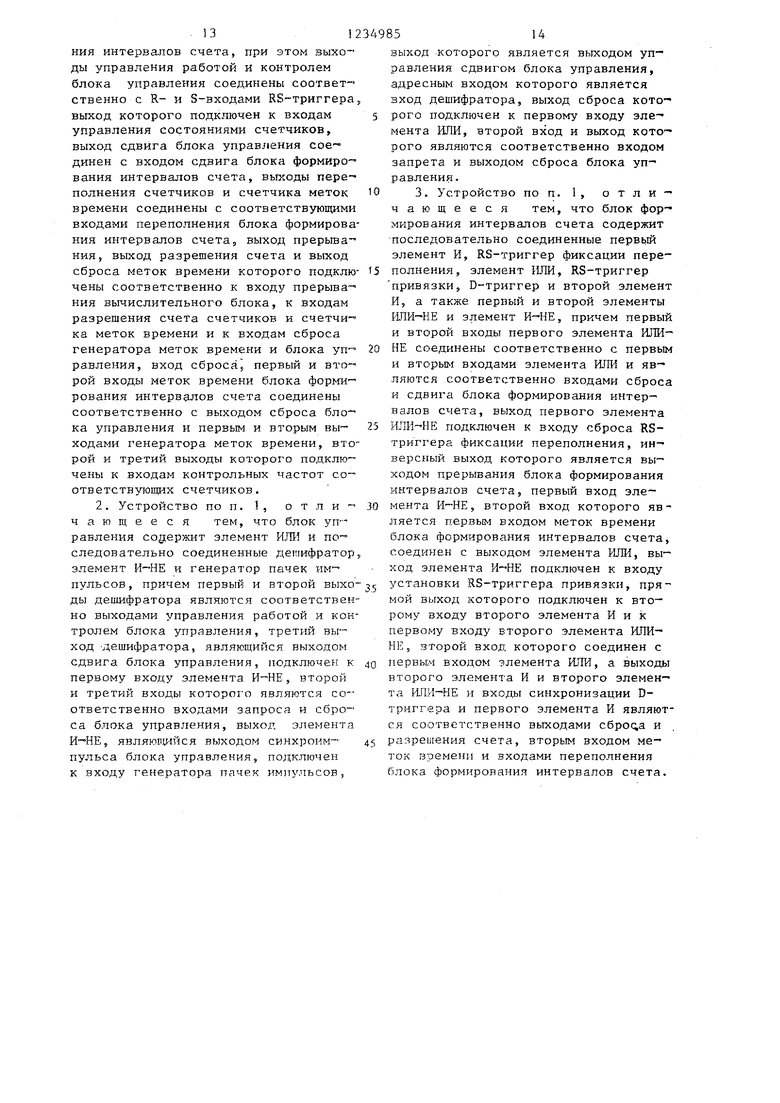

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 - структурная электрическая схема генератора псевдослучайного сигнала; на фиг. 3 - структурные электрические схемы блока управления, блока формирования интервалов счета и генератора меток времени; на фиг. 4 - временные диаграммы, поясняющие работу блока управ ления, блока формирования интервалов счета и генератора меток времени.

Устройство содержит генератор 1 псевдослучайного сигнала, генератор 2 тактовой частоты, входной коммута- тор 3, блок 4 интегрирования, состоящий из фильтра 5 нижних частот и порогового элемента 6, первый основной сумматор 7 по модулю два, первый D-триггер 8, второй основной сумма- тор 9 по модулю два, второй D-триггер 10, первый блок 11 задержки, первый дополнительный сумматор 12 по модул два, второй блок 13 задержки, второй дополнительный сумматор 14 по модулю два, первый и второй счетчики 15 и 16 импульсов, генератор 17 меток времени, счетчик 18 меток времени, блок 19 управления, RS-триггер 20, блок

измерения сбоев, когда лог. уровни напряжения на выходах D-T 8 .и 10 изменяются в соответствии с сигналами на входах С 7 и 9, поскольку лог. уровень напряжения на выходе эл-тон равен нулю. 2 з.п. ф-лы, 4 ил.

21 формирования интервалов счета, вычислительный блок 22 и блок 23 индикации.

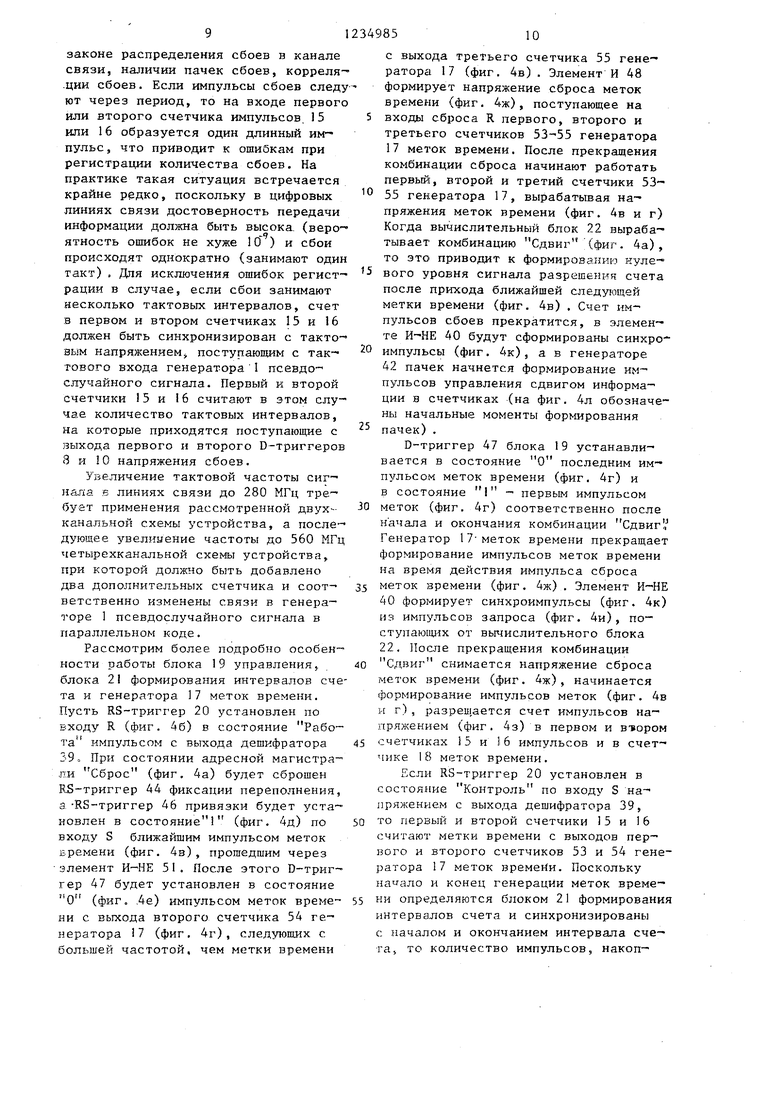

Генератор 1 псевдослучайного сигнла содержит D-триггеры 24-29, сумматор 30 по модулю два, D-триггеры 31- 37 и cyiMMaTop 38 по модулю два.

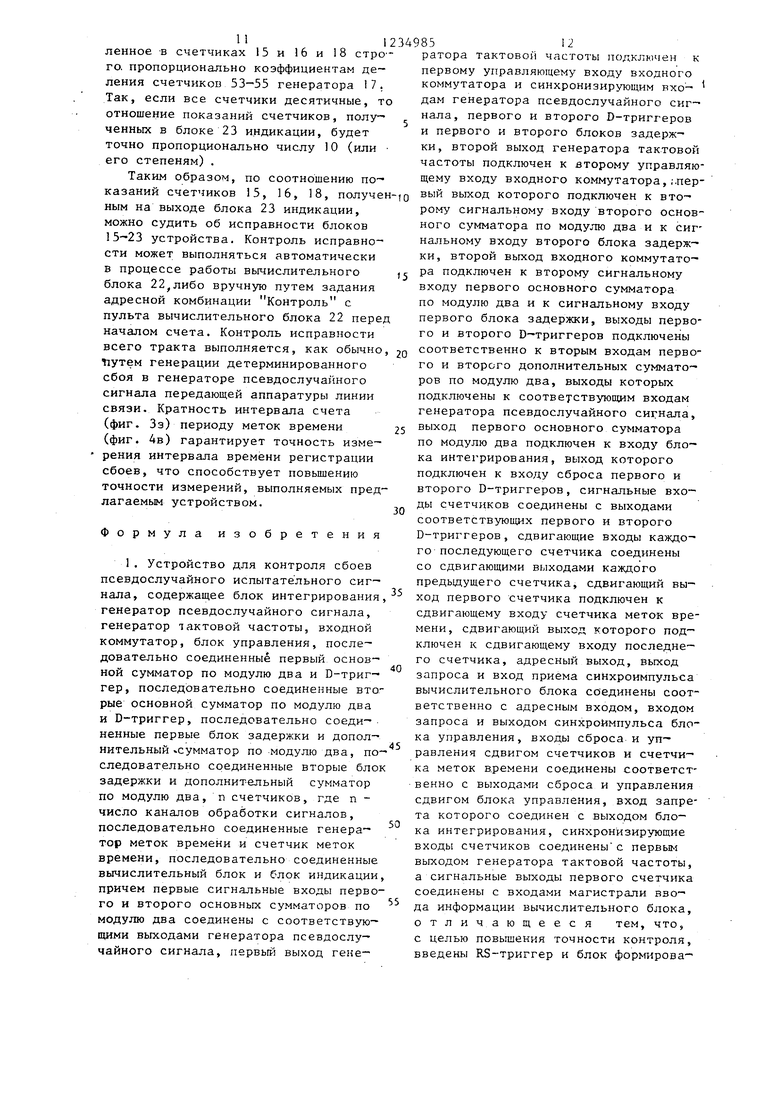

Блок 19 управления содержит дешифратор 39 адреса, элемент И-НЕ 40, элемент ИЛИ 41, генератор 42 пачек импульсов. Блок 21 формирования ин-- тервалов счета содержит первый элемент И 43, RS-триггер 44 фиксации переполнения, элемент ИЛИ 45, RS-триггер 46 привязки, D-триггер 47, второй элемент И 48, первый элемент ИЛИ-НЕ 49, второй элемент ИЛИ-НЕ 50, элемент И-НЕ 51.

Генератор 17 меток времени содержит кварцевый генератор 52, первый, второй и третий счетчики 53-55.

Устройство работает следующим образом.

Исследуемый сигнал в виде М-после довательности поступает на вход входного коммутатора 3, который осущест- вляет в данном случае преобразование из последовательного кода на входе в 2-разрядный бинарньй параллельный код на своих выходах. При этом на каждом выходе входног о коммутатора 3 длительность кодового импульса равна двум тактовым интервалам, причем сигнал, поступающий на вход второго основного сумматора 9 по модулю два, соответствует сигналу S., в первой половине предыдущего двухтактового интервала, а сигнал, поступающий на вход первого основного сумматора 7 по модулю два, - сигналу 5„ во второй половине предыдущего двухтактового интервала преобразования из последовательного кода на входе в параллельный код на выходе входного коммутатоpa 3. Начало двухтактового интервала задается напряжением полутактовой частоты с выхода генератора 2 такто вой частоты. (Генератор 2 входит в состав регенерационной аппаратуры исследуемой линии связи либо является специальным выделителем тактовой частоты в предлагаемом устройстве, подобным выделителям тактовой частоты регенераторов) .

Обозначим S

П-1

и Sn соответственно коды сигналов на выходах второго и первого D-триггеров 10 и 8 аналогично кодам S., и S в первой и второй половинах двухтактового ин- тервала, задаваемого напряжением по- лутактовой частоты с выхода генератора 2 тактовой частоты. Вьфазим коды S, и БП через S., и 8„ и оператор задержки X. Поскольку задержка в каждом из D-триггеров 24-29, 31-37 генератора 1 и в первом и втором блоках 11 и 13 задержки равна двум тактовым интервалам, то оператор задержки в каждом из них выражается в 2

форме X .

Предлагаемое устройство может работать в двух режимах: 1) режим синхронизации, когда первый и второй D-триггеры 8 и 10 сброшены в нулевое состояние импульсом, сформированным на выходе порогового элемента 6; 2) режим измерения сбоев, когда логические уровни напряжения на выходах первого и второго D-триггеров 8 и 10 из- меняются в соответствии с сигналами на входах первого и второго основных сумматоров 7 и 9 по модулю два, поскольку логический уровень напряжения на вЫ ходе порогового элемента 6 равен ну- лю.

Получим выражение для кодов 8„., и S на выходах второго и первого основных сумматоров 9 и 7 по модулю два в первой и второй половинах двухтактового интервала в режиме синхронизации, при котором с выхода первого основного сумматора 7 на вход блока 4 интегрирования поступает непрерывный поток импульсов ошибок, На выходе блока 4 интегрирования вырабатывается при этом сигнал уровня логической единицы, который сбрасывает в нулевое состояние первый и второй D-триггеры 8 и 10. Указанный поток импульсов ошибок образуется потому, что сигнал, записанный в D- триггерах 24-29, 31-37 генератора 1

и в первом и втором блоках II и 13 задержки в момент включения устройства, не соответствует по структуре псевдослучайной последовательности, поступающей на вход устройства.

В этом случае код сигнала S , выражается суммой по модулю два кода S., на одном входе второго основного сумматора 9 и кода на выходе D-триг- гера 29, который можно вьфазить в следующем виде

S,, ( -h 8„хЪх , (1)

где выражение в скобках соответствует коду на выходе сумматора 30 по модулю два генератора Г, которое является результатом суммирования кода и кода на первом и втором его входах. Тогда справедливо соотношение:

Sn-, + S,X +

(4

п-1 п-( -п Аналогично можно вычислить, что код на выходе первого основного сумматора 7 выражается в виде:

S, (S,,X + S.

Sn + Sn., s..;xr .

(3)

Код Sj, является результатом задержки псевдослучайного сигнала на один такт. Поэтому, используя оператор задержки X, можно записать соотношение :

(А)

Sn V,x,

подставив которое в (2) и (3), получим выражения:

-, Sn-,1 (5)

sl 5„(1 + Х - х ), (6)

в которых полином 1 + X + X соответствует образующему полином генератора 1 псевдослучайного сигнала в виде М-последовательности.

Если псевдослучайный сигнал S вырабатывается генератором 1 со структурой обратных связей описываемой образующим полиномом 1 + X iCJl

4-х , и не содержит сбоев, то S и S| равны нулю. В этом случае на входах сброса первого и второго D- триггеров 8 и 10 установится напряжение логического нуля, поскольку на вх.од блока 4 интегрирования поступаг ет нулевое напряжение. В результате первый и второй D-триггеры 8 и 10 будут функционировать как блоки задержки. Устройство переходит в режим измерения сбоев.

Если при этом в псевдослучайном сигнале появляются отклонения (сбои по сравнению с эталонной М-после- довательностью, т.е.

. (7)

Ср.,- , ) + Cn-i , и -

(8)

где 8(„., и 8м„ - соответствующие

значения кодов для М-после довательности в первой и второй половинах двухтакто- вого интервала;

6, и &„ - аналогичные значения для сбоев М-шоследовательности, то на входах второго и первого D- триггеров 10 и 8 появляются сигналы

It

ошибки S.,, 8„ , которые меняют логические уровни поступающего входного сигнала 8„.,, S, . При этом опорная псевдослучайная последовательность, записанная ранее в генераторе 1, не меняется. Благодаря этому на вьгходах второго и первого D-триггеров 10 и 8 выделяются сигналы ошибок (сбоев) s)|,, s соответствующие сигналам сбоев Е„ , , п входного испытатель

кого сигнала .Я., 8„. Структура па- чек сбоев в таком случае регистрируется без искажений, причем на вьгхода второго и первого D-триггеров 10 и 8 появляются сигналы:

S.., f,.,. 8„,, (9)

первый из которых соответствует по времени сбою, приходящемуся на перву половину двухтактового интервала, а второй - на вторую половину двухтактового интервала напряжения полутак- товой частоты.

Покажем теперь, каким образом в предложенном устройстве выходные сигналы S.,, S выражаются через входные сигналы S,.,, 8„ . Для предлагаемого устройства, работающег о в режиме измерения сбоев, может быть за писана следующая система уравнений:

(S, 8,,)Х,

Sn-, S,,)X

(10) (11)

Sj, (3„Х + S;,))X (12) S,, (8„, 8;,)xV;Ux )x ; (13)

где Sj, S ,,j - сигналы на выходах D

D-триггеров 37 и 29 генератора 1 .

Из системы уравнений (10)-(13) могут быть получены следующие уравнения для S. и S n ;

Sp У s,.,(x 4x),(x

-ЬХ )(14)

s;., 8„„Х + 8ЛХ % х )4

1о и + 5„(Х + X ),

(15)

откуда следует (с учетом (4)), что

I 1 W 15 I И 15

S,, (1+Х +Х ) +Х ), (16) -, ()+5;.,(Х ,,j

Умножение на образующий полином 1 1+х +Х в уравнениях (16) и (17) означает выделение опибок f., , Е„ (см. (7) и (8)) из принятой М- после- довательности. По этому уравнения (16) и (17) для сбоев f и могут быть после соответствующих преобразований записаны в следующей форме:

г Г F f ч -ц п 1 n-i }

(18)

., ,„ - сигналы ошибок (сбоев на выходах второго и первого D-триггеров 10 и 8.

Уравнения (18) показьгоают, что сигналы ошибок на выходах второго и первого D-триггеров 10 и 8 задержаны на два тактовых интервала по отношению к сигналу ошибок (сбоев) во входной последовательности, одНако структура пачки сбоев на выходе полностью соответствует структуре пачки сбоев на входе.

Благодаря тому, что имеющиеся в устройстве сумматоры по модулю два нигде не соединяются непосредственно друг с другом, поскольку разделены D-триггерами, сумма задержек в сумматоре по модулю два i g и в D-триг- гере tj, , необходимая для работоспособности устройства, должна быть не больше двойного тактового интервала 2Т, т.е.

2Т.

(19)

Если c g jj 4 НС, то максимальное значение тактовой частоты (f /Т) равно 250 МГц.

15

20

Как -показали эксперименты, при существующей отечественной элементной базе (интегральные схемы серий 100, 500 и 570 ТМ1) могут быть построены первый и второй 15 и 16 счетчики им-- пульсов с максимальной скоростью счета не более 220 МГц. Однако для сверхскоростной цифровой связи необходимо обеспечить работу устройства при следующих дискретных значениях такто JQ вой частоты: 140, 280, 560 и 1200 МГц Поскольку разработка аппаратуры для тактовой частоты 140 МГц может быть выполнена уже известными средствами, следующей задачей является достижение быстродействия 280 и 560 МГц. Здесь ограничивающими факторами являются недостаточные максимальная скорость сдвига информации в генераторе 1 (160 МГц) и быстродействие первого и второго счетчиков 15 и 16 импульсов (220 МГц) .

В предлагаемом устройстве, предназначенном дпя регистрации импульсов сбоев, следующих с частотой до 280 МГц и более, имеется как минимум два канала счета импульсов. На счетные входы первого и второго счетчиков 15 и 16 поступают импульсы сбоев в параллельном коде с выходов первого и второго D-триггеров 8 и 10. Начало интервала счета задается автоматически по программе обработки вычислительным блоком 22, который по адресной шине посылает в блок 19 управления байтовую комбинацию сигналов, вызывающую сброс первого и второго счетчиков 15 и 16 импульсов и счетчика 18 меток времени. После снятия импульсов сброса первый и второй счетчики 15 и 16 могут переходить в режим счета. Если при этом на вход запрета блока 19 управления (т.е. на вход элемента ИЛИ 41) поступает нулевой сигнал с порогового элемента 6,

25

30

35

40

нала не будет зарегистрирована как сбой передаваемого . Сброс по цепи запрета возникает также при включении питания устройства, когда в генераторе 1 псевдослучайного си1- нала происходят процессы установления состояния синхронизации.

Таким образом, сброс по цепи запрета позволяет исключить сбои устройства, не отражающие состояние канала связи, что повьшает точность измерений.

По прошествии заданного интервала вычислительный блок 22 вырабатывает на адресной магистрали комбинацию сигналов Сдвиг, под действием которой блок 21 формирования интервалов счета запрещает счет импульсов в счетчиках 15, 16 и 18, а блок 19 управления в момент появления заднего отрицательного фронта импульса запроса информации с вычислительного блока 22 вырабатывает импульсы управления сдвигом информации, поступающие на входы управления сдвигом информации в счетчиках 15, 16 и 18 (с выходов генератора 42 пачек импульсов) . Под действием этих импульсов в счетчиках 15, 16 и 18 происходит циклический сдвиг информации. После завершения очередного такта сдвига информации вычислительный блок 22 запоминает информацию на выходах предпоследней ступени первого счетчика 15. После завершения сдвига информации вычислительный блок 22 снимает с адресной шины комбинацию, соответствующую сдвигу информации. При этом информация в счетчиках 15, 16 и 18 после полного цикла сдвига.возвращается в соответствующие каскады счета, а устройство снова переходит в режим счета импульсов сбоев и меток времени.

Следовательно в памяти вычислито с выхода элемента ИЛИ 41 на входы тельного блока 22 имеется информация

-, 50

сброса счетчиков 15, 16 и 18 поступает также нулевой сигнал, не вызывающий сброса счетчиков, которые в этом случае переходят в режим счета Если же на вход запрета блока 19 уп равления поступает с порогового элемента 6 единичный, сигнал, то это приводит к сбросу всей накопленной информации в счетчиках 15, 16 и 18. После этого цикл накопления информации начинается сначала. Благодаря этому единичный.сбой или пачка сбоев в генераторе 1 псевдослучайного сиг55

о количестве импульсов сбоев, зарегистрированных первым и вторым счетчиками 15 и 16, и меток времени, зарегистрированных в счетчике .18 от генератора 17. Сумма показаний первого и второго счетчиков 15 и .16 дает общее количество сбоев за измеряемый интервал. Показания счетчика 18 соответствуют количеству тактовых интервалов за интервал измерений. Полученная информация позволяет после обработки непрерывно получать сведения о частости сбоев в канале.

5

0

Q

5

0

0

нала не будет зарегистрирована как сбой передаваемого . Сброс по цепи запрета возникает также при включении питания устройства, когда в генераторе 1 псевдослучайного си1- нала происходят процессы установления состояния синхронизации.

Таким образом, сброс по цепи запрета позволяет исключить сбои устройства, не отражающие состояние канала связи, что повьшает точность измерений.

По прошествии заданного интервала вычислительный блок 22 вырабатывает на адресной магистрали комбинацию сигналов Сдвиг, под действием которой блок 21 формирования интервалов счета запрещает счет импульсов в счетчиках 15, 16 и 18, а блок 19 управления в момент появления заднего отрицательного фронта импульса запроса информации с вычислительного блока 22 вырабатывает импульсы управления сдвигом информации, поступающие на входы управления сдвигом информации в счетчиках 15, 16 и 18 (с выходов генератора 42 пачек импульсов) . Под действием этих импульсов в счетчиках 15, 16 и 18 происходит циклический сдвиг информации. После завершения очередного такта сдвига информации вычислительный блок 22 запоминает информацию на выходах предпоследней ступени первого счетчика 15. После завершения сдвига информации вычислительный блок 22 снимает с адресной шины комбинацию, соответствующую сдвигу информации. При этом информация в счетчиках 15, 16 и 18 после полного цикла сдвига.возвращается в соответствующие каскады счета, а устройство снова переходит в режим счета импульсов сбоев и меток времени.

Следовательно в памяти вычисли тельного блока 22 имеется информация

50

55

о количестве импульсов сбоев, зарегистрированных первым и вторым счетчиками 15 и 16, и меток времени, зарегистрированных в счетчике .18 от генератора 17. Сумма показаний первого и второго счетчиков 15 и .16 дает общее количество сбоев за измеряемый интервал. Показания счетчика 18 соответствуют количеству тактовых интервалов за интервал измерений. Полученная информация позволяет после обработки непрерывно получать сведения о частости сбоев в канале.

законе распределения сбоев в канале связи, наличии пачек сбоев, корреля- .дни сбоев. Если импульсы сбоев следу ют через период, то на входе первого или второго счетчика импульсов, 15 или 16 образуется один длинный импульс , что приводит к ошибкам при регистрации количества сбоев. На практике такая ситуация встречается крайне редко, поскольку в цифровых линиях связи достоверность передачи информации должна быть высока, (вероятность ошибок не хуже 10 ) и сбои происходят однократно (занимают один гакт) , Для исключения ошибок регистрации в случае, если сбои занимают несколько тактовых интервалов, счет в первом и втором счетчиках 15 и 16 должен быть синхронизирован с такто- зьш напряжением поступающим с тактового входа генератора 1 псевдослучайного сигнала. Первый и второй счетчики 15 и 16 считают в этом случае количество тактовых интервалов, на которые приходятся поступающие с выхода первого и второго D-триггеров 8 и 10 напряжения сбоев.

Увеличение тактовой частоты сигнала Б линиях связи до 280 МГц требует применения рассмотренной двух- канальной схемы устройства, а последующее увелиыение частоты до 560 МГц четырехканальной схемы устройства, при которой должно быть добавлено два дополнительных счетчика и соответственно изменены связи в генераторе 1 псевдослучайного сигнала в параллельном коде.

Рассмотрим более подробно особенности работы блока 19 управления, блока 21 формирования интервалов счета и генератора 17 меток времени. Пусть RS-триггер 20 установлен по входу R (фиг. 4б) в состояние Рабо та импульсом с выхода дешифратора 39. При состоянии адресной магистра- -яи Сброс (фиг. 4а) будет сброшен ЦБ-триггер 44 фиксации переполнения, а, -Кй-триггер 46 привязки будет установлен в состояние (фиг. 4д) по входу S ближайшим импульсом меток времени (фиг. 4в), прошедшим через элемент И-НЕ 5I. После этого D-триг- гер 47 будет установлен в состояние О (фиг. ,4е) импульсом меток времени с выхода второго счетчика 54 генератора 7 (фиг. 4г), следующих с большей частотой, чем метки времени

с выхода третьего счетчика 55 генератора Г/ (фиг. 4в) . Элемент И 4В формирует напряжение сброса меток времени (фиг. 4ж), поступающее на входы сброса R первого, второго и третьего счетчиков 53-55 генератора 17 меток времени. После прекращения комбинации сброса начинают работать первый, второй и третий счетчики 5355 генератора 17, вырабатывая напряжения меток времени (фиг. 4в и г) Когда вычислительный блок 22 вырабатывает комбинацию Сдвиг (фиг. 4а), то это приводит к формированию куле-

вого уровня сигнала разрешения счета после прихода ближайшей следующей метки времени (фиг. 4в) . Счет импульсов сбоев прекратится, в элементе И-НЕ 40 будут сформированы синхро

импульсы (фиг. 4к), а в генераторе 42 пачек начнется формирование импульсов управления сдвигом информации в счетчиках (на фиг. 4л обозначены начальные моменты формирования

пачек) .

D-триггер 47 блока 19 устанавливается в состояние О последним импульсом меток времени (фиг. 4г) и в состояние I - первьм импульсом

меток (фиг. 4г) соответственно посла начала и окончания комбинации Сдвиг ,- Генератор 17 меток времени прекращает формирование импульсов меток времени на время действия импульса сброса

меток времени (фиг. 4ж) . Элемент И-НЕ 40 формирует синхроимпульсы (фиг. 4к) из импульсов запроса (фиг. 4и), по- ступаюсцих от вьтислительного блока 22. После прекращения комбинации

Сдвиг снимается напряжение сброса меток времени (фиг. 4ж), начинается формирование импульсов меток (фиг. 4в н г) , разреш.ается счет импульсов напряжением (фиг. 4з) в первом и в-вором

счетчиках 5 и 16 импульсов и в счетчике 18 меток времени.

Если RS-триггер 20 установлен в состояние Контроль по входу S напряжением с выхода дешифратора 39,

то первый и второй счетчики 15 и 16 считают метки времени с выходов первого и второго счетчиков 53 и 54 генератора 17 меток времени. Поскольку начало и конец генерации меток времени определяются блоком 21 формирования интервалов счета и синхронизированы с началом и окончанием интервала счета, то количество импульсов, накоп1

ленное -в счетчиках 15 и 16 и 18 стро - го. пропорционально коэффициентам деления счетчиков генератора 17. Так, если все счетчики десятичные, то отношение показаний счетчиков, полу- ценных в блоке 23 индикации, будет точно пропорционально числу 0 (или его степеням) .

Таким образом, по соотношению показаний счетчиков 15, 16, 18, получен ным на выходе блока 23 индикации, можно судить об исправности блоков 15-23 устройства. Контроль исправно-- сти может выполняться автоматически в процессе работы вычислительного блока 22,либо вручную путем задания адресной комбинации Контроль с пульта вычислительного блока 22 перед началом счета. Контроль исправности всего тракта выполняется, как обычно, 11утем генерации детерминированного сбоя в генераторе псевдослучайного сигнала передающей аппаратуры линии связи. Кратность интервала счета (фиг. Зз) периоду меток времени (фиг. 4в) гарантирует точность измерения интервала времени регистрации сбоев, что способствует повьш ению точности измерений, выполняемых предлагаемым устройством.

12

Формула изобретения

1. Устройство для контроля сбоев псевдослучайного испытательного сигнала, содержащее блок интегрирования генератор псевдослучайного сигнала, генератор тактовой частоты, входной коммутатор, блок управления, последовательно соединенные первый основной сумматор по модулю два и D-триг- гер, последовательно соединенные вторые основной сумматор по модулю два и D-триггер, последовательно соеди-- ненные первые блок задержки и дополнительный «сумматор по модулю два, последовательно соединенные вторые бло задержки и дополнительный сумматор по модулю два, п счетчиков, где п - число каналов обработки сигналов, последовательно соединенные генератор меток времени и счетчик меток времени, последовательно соединенные вычислительный блок и блок индикации причем первые сигнальные входы первого и второго основных сумматоров по модулю два соединены с соответствующими выходами генератора псевдослучайного сигнала, первый выход гене,

-)Q 15

20

25

, 3498512

ратора тактовой частоты подключен к

первому управляющему входу входного коммутатора и синхронизирующим вхо- дам генератора псевдослучайного сигнала, первого и второго D-триггеров и первого и второго блоков задержки, второй выход генератора тактовой частоты подключен к второму управляю щему входу входного коммутатора,;.первый выход которого подключен к второму сигнальному входу второго основного сумматора по модулю два и к сиг нальному входу второго блока задержки, второй выход входного коммутатора подключен к второму сигнальному входу первого основного сумматора по модулю два и к сигнальному входу первого блока задержки, выходы первого и второго D-триггеров подключены соответственно к вторым входам первого и второго дополнительных сумматоров по модулю два, выходы которых подключены к соответствующим входам генератора псевдослучайного сигнала, выход первого основного сумматора по модулю два подключен к входу блока интегрирования, выход которого подключен к входу сброса первого и второго D-триггеров, сигнальные входы счетчиков соединены с выходами соответствующих первого и второго D-триггеров, сдвигающие входы каждого последующего счетчика соединены со сдвигающими выходами каждого предыдущего счетчика, сдвигающий выход первого счетчика подключен к сдвигающему входу счетчика меток времени, сдвигающий выход которого подключен к сдвигающему входу последнего счетчика, адресный выход, выход запроса и вход приема синхроимпульса вычислительного блока соединены соответственно с адресным входом, входом запроса и выходом синхроимпульса блока управления, входы сброса и управления сдвигом счетчиков и счетчика меток в.ремени соединены соответственно с выходами сброса и управления сдвигом блока управления, вход запрета которого соединен с выходом блока интегрирования, синхронизирующие входы счетчиков соединены с первым выходом генератора тактовой частоты, а сигнальные выходы первого счетчика соединены с входами магистрали ввода информации вычислительного блока, отличающееся тем, что, с целью повышения точности контроля, введены RS-триггер и блок формирова-

30

35

40

45

50

55

.131

ния интервалов счета, при этом выходы управления работой и контролем блока управления соединены соответственно с R- и 8 входами КВ-триггера выход которого подключен к входам управления состояниями счетчиков, выход сдвига блока управления соединен с входом сдвига блока формиро- вания интервалов счета, выходы пере- полнения счетчиков и счетчика меток времени соединены с соответствующими входами переполнения блока формирования интервалов счета, выход прерьша ния5 выход разрешения счета и выход

сброса меток времени которого подклю- t5 полнения, элемент ИЛИ, RS-триггер

чены соответственно к входу прерыва- ния вычислительного блока, к входам разрешения счета счетчиков и счетчика меток времени и к входам сброса генератора меток времени и блока уп- равления, вход сброса, первый и вто- рой входы меток времени блока формн- рования интервалов счета соединены соответственно с выходом сброса блока управления и первым и вторым выходами генератора меток времени, второй и третий выходы которого подключены к входам контрольных частот соответствующих счетчиков.

2. Устройство по п. 1, о т л и чающееся тем, что блок уп- равления содержит элемент ИЛИ и последовательно соединенные денуифратор элемент И-НЕ и генератор пачек им-

пульсов, причем первый и второй выхо-,; установки RS-триггера привязки, пряды дешифратора являются соответственно выходами управления работой и контролем блока управления, третий вы ход -дешифратора, являющийся выходом сдвига блока управления, подключен к первому входу элемента И-НЕ., второй и третий входы которого являются соответственно входами запроса и сброса блока управления, выход элемента И-НЕ, являюнщйся выходом синхроимпульса блока управления, подключен к входу генератора пачек импульсов,

5

14

выход которого является выходом управления сдвигом блока управления, адресным входом которого является вход дешифратора, выход сброса которого подключен к первому входу элемента ИЛИ, второй вход и выход которого являются соответственно входом запрета и выходом сброса блока управления.

3. Устройство по п. 1, отличающееся тем, что блок формирования интервалов счета содержит последовательно соединенные первьй элемент И, RS-триггер фиксации пере,

привязки, D-триггер и второй элемент И, а также первый и второй элементы :ИЛИ-НЕ и элемент И-НЕ, причем первый и второй входы первого элемента ИЛИ- 20 НЕ соединены соответственно с первым и вторым входами элемента ИЛИ и являются соответственно входами сброса и сдвига блока формирования интервалов счета, выход первого элемента 25 ИЛН-НЕ подключен к входу сброса RS- триггера фиксации переполнения, инверсный выход которого является выходом прерывания блока формирования интервалов счета, первый вход эле- 30 мента И-НЕ, второй вход которого является первым входом меток времени блока формирования интервалов счета, соединен с выходом элемента ИЛИ, выход элемента И-НЕ подключен к входу

мои выход которого подключен к второму входу второго элемента И и к первому входу второго элемента ИЛИ- НЕ 5 второй вход которого соединен с

первым входом элемента ИЛИ, а выходы второго элемента И и второго элемента ИЛИ-НЕ и входы синхронизации D- триггера и первого элемента И являются соответственно выходами сброс;а и

разрешения счета, вторьЕМ входом меток времени и входами переполнения блока формирования интервалов счета.

фиг, 2

фиг,3

д е /к

Составитель В. Слепаков Редактор К. Волощук Техред И.Поповкч Корректор Е. Рогако

Заказ 2991/59 Тираж 624 . Подписное

ВНШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-тюлиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1981 |

|

SU1035822A1 |

| Устройство фазирования псевдослучайных последовательностей | 1986 |

|

SU1381726A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU942014A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1529459A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2276835C1 |

| Устройство для формирования случайных и псевдослучайных чисел | 1980 |

|

SU1012252A1 |

Изобретение относится к технике измерений в цифровых линиях связи. Повьшается точность контроля . Устр-во содержит г-р 1 псевдослучайного сигЛ. нала, г-р 2 тактовой частоты, входной коммутатор 3, блок 4 интегрирования, состоящий из фильтра 5 нижних частот и порогового эл-та 6, основные сумматоры (С) 7 и 9 по модулю два, D-триггеры (Т) 8 и 10, блоки задержки 11 и 13, дополнительные С 12 и 14 по модулю два, счетчики 15 и 16 импульсов, г-р 17 меток времени, счетчик 18 меток времени, блок 19 управления, RS - Т 20, блок 21 формирования интервалов счета, вычислительный блок 22, блок 23 индикации. Г-р 1 содержит тринадцать D-тригге- ров и два С по модулю два. Г-р 17 содержит кварцевый г-р и три счетчика. Блок 19 содержит дешифратор адреса, эл-т И-НЕ, эл-т ИЛИ, г-р пачек импульсов. Блок 21 содержит два э-та И, RS-T фиксации переполнения, эл-т с ю (Л Ю СО N со 00 СП

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1981 |

|

SU1035822A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-05-30—Публикация

1984-11-29—Подача