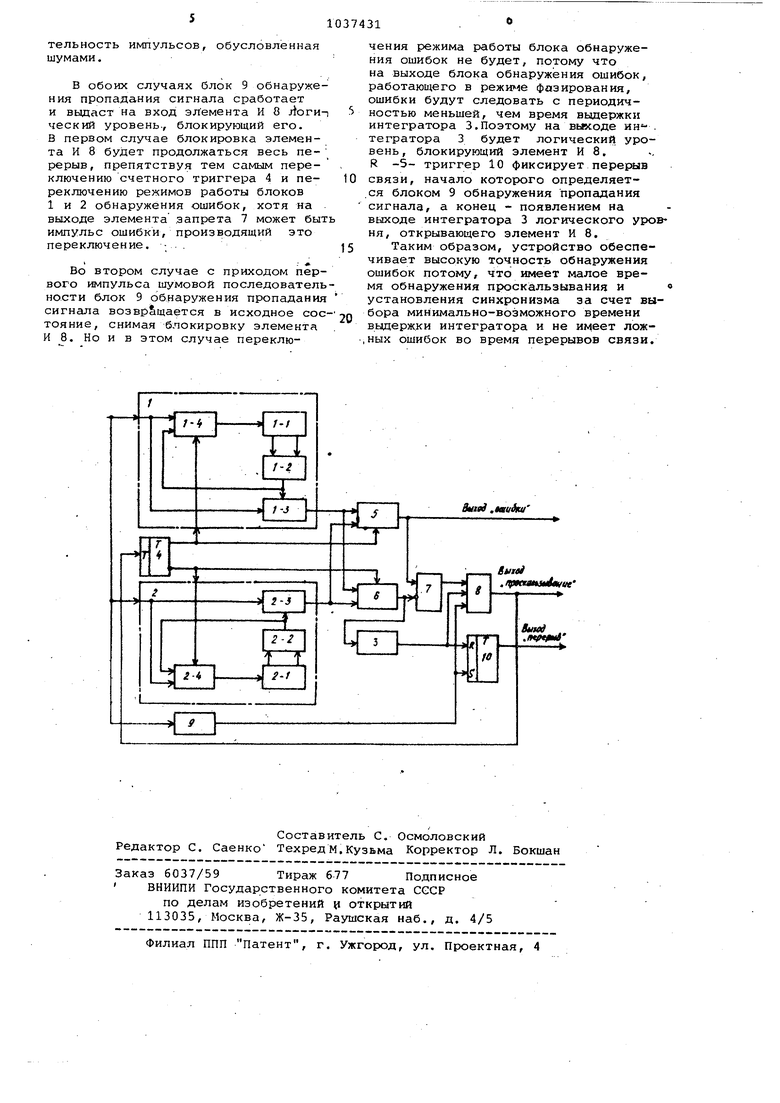

Изобретение относится к электросвязи и можетбыть использовано при передаче цифровых испытательных сигналов в виде псевдослучайных последовательлостей (ПСП). Известно устройство для синхрони зации контрольного и эталонного циф ровых сигналов, содержащее элемент НЕТ, блок выделениятактовой частоты, вход которого подключен к шине контрольного сигнала, первый выход блока выделения тактовой Частоты со динен с входом счетчика импульсов, вьлходы которого через дешифратор подключены к первым входам первого и второго элементов И, выход второг элемента И соединен с первым входом генератора эталонных сигналов, второй вход которого подключен к выходу блока выделения тактовой частот а также элемейт НЕ, R - 3 -триггер и блок несовпадений, выход которого соединен с первым входом элемента НЕТ, второй вход которого подключен к последнему разряду счетчика импульсов, а выход элемента ПЕТ соединен с первым входом R- S -триггера, к второму входу которого подключен второй выход дешифратора, причем выход Р- S -триггера соединен с вто рым входом второго элемента И Herloci редственно и через элемент НЕ с вторым входом первого элемента- И, выход которого подключен к третьему входу генератора эталонных сигналов выход которого соединен с первым входом блока несовпадений,- второй вход которого подключен к шине контрольного сигнала Cl 1. Однако устройство обладает низкой точностью обнаружения ошибок. Наиболее блйзким техническим решением к изобретению является устройство для обнаружения ошибок, содержащее последовательно соединенные переключатель, регистр сдвига, первый полусумматор, преобразова тель кода, второй полусумматор, и ин тегратор, выход которого подключен к управляющему входу переключателя, первый вход которого объединен с входом преобразователя кодов, а второй - с входом элемента задержки, выход которого соединен с вторым входом второго полусумматора L2. Недостаток известного устройства низкая точность обнаружения ошибок из-за отсутствия возможности отличат перерывы связи от проскальзываний и отдельных ошибок. Цель изобретения - повышение точности обнаружения ошибок, проскальз лваний и перерывов . связи. Поставленная цель достигается тем что в устройство для обнаружения ошибок, проскальзываний и перерывов связи, содержащее интегратор и первы блок обнаружения ошибок, состоящий из первого полусумматора и последовательно соединенных переключателя, peJгиcтpa сдвига и второго полусумматора, выход которого подключен к второму входу переключателя, причем первый вход переключателя является первым входом первого блока обнаружения ошибок, выходом которого .является выход первого полусумматора, введены второй блок .обнаружения ошибок, счетный триггер, третий и четвертый переключатели, элемент запрета, элемент И, блок обнаружения пропадания сигнала и f - S-триггер, при этом выходы вторых полусумматоров первого и второго блоков обнаружения, ошибок подключены к первым входам первых полусумматоров первого и второго блоков обнаружения ошибок, а вторые входы первых полусумматоров первого и второго блоков обнаружения ошибок объединены друг с другом и с первыми входами соответствующих переключателей первого и второго блоков обнаружения ошибок и являются входом устройства, причем выходы первого и второго блоков обнаружения ошибок подключены соответственно к первым . и вторым входам третьего и четвертого переключателей, к третьим входам которых подключены первый и второй выходы счетного триггера, выход третьего переключателя является выходом ошибки устройства и подключен к первому входу элемента запрета, к второму входу которого и к входу интегратора подключен выход четвертого переключателя, а выход интегратора подключен к первым входам (-5-триггера и элемента И, к второму входу которого подключен выход элемента запрета, выход элемента И является выходом проскальзывание устройства и подключен к входу счетного триггера, выходы которого подключены к третьим входам переключателей первого и второго блоков обнаружения ошибок, при этом вход устройства объединен с входом блока: обнаружения пропадания сигнала, выход кото- « рого подключен к третьему входу элемента Ник второму входу R-S-триггера, выход которого является выходом перерыв связи устройства. На,чертеже представлена структурная схема устройства для обнаружения ошибок, проскальзыв аний и перерывов связи. Устройство содержит первый блок 1 обнаружения ошибок, состоящий из регистра 1-1 сдвига, первого Г-2 и второго 1-3 полусумматоров, переключателя 1-4, второй блок 2 Обнаружения ошибок, состоящий из регистра 2-1 сдвига, первого 2-2 и второго 2-3 полусумматоров, переключателя 2-4, интегратор 3, счетный триггер 4, третий 5 и четвертый 6 переключатели, элемент запрета 7, элемент И 8, блок 9 обнаружения пропадания сигнала, R-S -триггер 10. Устройство работает следующим образом. Допустим, счетный триггер 4 находится в таком состоянии, что на его прямом выходе - логическая 1, а на инверсном - О. В этом случае переключатель 1-4 замыкает обратную связь с выхода первого полусумматора 1-2 на вход регистра 1-1 сдвига. Назовем такой регистр сдвига замкнутым регистром сдвига. На втором полусумматоре 1-3 происходит сравнение ПСП., формируемой в замкнутом регистре 1-1 сдвига, с ПСП, приходящей на вход устройства и выделяются ошибки. Третий переключатель 5, управляемый счетным триггерой 4, всегда пропускает сяаиб ки, выделенные полусумматором только при работе с тем регистром, который в данный момент является замк нутым. В данном случае он пропускае ошибки, выделенные вторым полусумма тором 1-3. В это время переключателем 2-4, управляемым счетным триггером 4, обратная связь с выхода второго полусумматора 2-2 на вход регистра 2-1 сдвига разомкнута. Через переключатель 2-4 производится заполнение регистра 2-1 сдвига |ПСП, приходящей на вход устройства, и происходит выделение ошибок на вт ром полусумматоре,2-3. Такой регист сдвига назовем разомкнутым регистром сдвига. Четвертый переключатель 6, управляемЕлй счетным триггером 4, всегда пропускает ошибки, выделенные полусумматором только при работе с тем регистром сдвига, кото рый в данный момент является разомк НУТЫМ.. (. Таким образом, первый блок 1 об наружения ошибок, состоящий КЗ регистра 1-1 сдвига, полусумматоров 1-2 и 1-3 и переключателя 1-4, работает в данный момент в режиме из мерения, а второй блок 2 обнаружения ошибок, состоящий из регисч ра 2-1 сдвига, полусумматоров 2-2 и 2 и переключателя 2-4, работает в ре жиме фазирования. В этом случае ошибки с выхода второго полусумматора 1-3, работeuo щего совместно с замкнутым регистром 1-1 сдвига, через третий переключатель 5 проходят на оши ки устройства и поступают На вход элемента запрета 1, на выход которого однако они не проходят, так к одновременно с каждым импульсом ошибки на запрещающий вход элемент ,3ёшрета 7 через четвертый переключатель 6 проходит импульс ошибки и с выхода второго полусумматора 2-3, работающего совместно с разомкнутым регистром 2-1 сдвига. Такое состояние устройства продолжается до тех пор, пбка не произойдет проскальзывание . При проскальзывании на втором полусум11аторе 1-3 зс1мкнутого регистра 1-1 сдвига, появляются ошибки, обусловленные этим проскальзыванием. .В этом случае, на выходе второго полусумматора 2-3 разомкнутого регистра 2-1 сдвига после его заполнения безошибочным отрезком ПСП, приходящим на вход устройства - отсутствие ошибок. Поэтому на выходе четвертого переключателя 6 нет ошибок и через время, определяемое временем выдержки интегратора 3, на втором входе элемента И 8 появится разрешающий логический уровень, и импульс ошибки, беспрепятственно прошедший через элемент запрета 7, проходит также через элемент И 8 и переключает счетный триггер 4 в противоположное состояние, так как на третьем входе элемента И 8 также разрешающий логический уровень, потому что на выходе блока 9 обнаружения пропадания сигнала запрещающий уровень появляется только тогда, когда отсутствует некоторое время сигнал на входе устройства. Импульс с выхода элемента И 8 поступает на выход проскальзывание устройства, сигнализируя о том, что было проскальзывание. После переключения счетного триггера 4 замкнутый регистр 1-1 сдвига размыкается и из режима измерения переходит в режим фазирования. Разомкнутый регистр 2-1 сдвига, заполненный безошибочным отрезксял ПСП, замыкается и начинает вырабатывать ПСП.идентичную принимаемой, т.е. из режима фазирования переключается в режгал измерения. В этом случае ошибки определяются на втором полусумматоре 2-3 и через третий переключатель 5 проходят на выход Саиибки устройства. Таким образом/ благодаря переключению режимов работы регистров сдвига уд 1ется определить появление проскальзывания в минимально короткое время, определяемое временем выдержки интегратора, которое однако не может быть меньше времени заполнения регистр сдвига. Перерыв связи в системах передачи может проявляться двояким рбраэом. В первом случае это сплошной нулевой промежуток. Во втором случае нулевой промежуток имеет место только в начале перерыва, а в остальное время перерыва за счет действия АРУ появляется случайная последовательность импульсов, обусловленная шумами.

В обоих случаях блок 9 обнаружения пропадания сигнала сработает и выдаст на вход элемента И 8 Логический уровень., блокирующий его. В первом случае блокировка элемента И 8 будет продолжаться весь парерыв, препятствуя тем самым переключению счетного триггера 4 и переключению режимов работы блоков 1 и 2 обнаружения ошибок, хотя на выходе элемента запрета 7 может быт импульс ошибки, производящий это переключение. - .

Во втором случае с приходом первого импульса шумовой последовательности блок 9 обнаружения пропадания сигнсша возвращается в исходное сое- Q тояние, снимая блокировку элемента И 8. Но и в этом случае переключения режима работы блока обнаружения ошибок не будет, потому что на выходе блока обнаружения ошибок, работающего в режиче фазирования, ошибки будут следовать с периодичностью меньшей, чем время выдержки интегратора 3.Поэтому на выходе ин . тегратора 3 будет логический уровень , блокирующий элемент И 8. R -5- триггер 10 фиксирует перерыв связи, начало которого определяется блоком 9 обнаружения пропадания сигнала, а конец - появлением на выходе интегратора 3 логического уроня, открывающего элемент И 8.

Таким образом, устройство обеспечивает высокую точность обнаружения ошибок потому, что имеет малое время обнаружения проскальзывания и установления синхронизма за счет выбора минимально-возможного времени выдержки интегратора и не имеет лож,ных ошибок во время перерывов связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения ошибок из цифрового испытательного сигнала | 1988 |

|

SU1626400A1 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU1010717A1 |

| Устройство измерения количества проскальзываний | 1983 |

|

SU1142897A1 |

| Обнаружитель ошибок | 1978 |

|

SU705692A1 |

| Генератор последовательности ошибок | 1982 |

|

SU1077044A1 |

| Устройство для обнаружения ошибок биполярного сигнала | 1981 |

|

SU1088143A2 |

| Устройство для исправления и обнаружения ошибок | 1984 |

|

SU1205312A2 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Способ обнаружения ошибок и устройство для его осуществления | 1989 |

|

SU1619412A1 |

| Устройство для исправления ошибок при итеративном кодировании | 1977 |

|

SU680061A2 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК, ПРОСКАЛЬЗЫВАНИЙ И ПЕРЕРЫВОВ .Связи, содержащее интегратор и первый блок обнаружения сшибок, состоящий из первого полусумматора и последователь.но соединенных переключателя, регистра сдвига и второго полусумматора, выход которого подключен к второму входу переключателя, причем первый вход переключателя является первым входом первого- блока обнаружения ошибок, выходом которого является выход первого полусумматора , отличающееся тем, что, с целью повышения точности обнаружения ошибок, проскальзываний и пере1извов связи, введены второй блок обнаружения ошибок, счетный триггер, третий и четвертый переключатели, элемент запрета, элемент И, блок обнаружения пропадания сигнала и R- S-триггерг приэтом выходы вторых полусумматоров первого и второго блоков обнаружения ошибок подключены соответственно к первым входам первых полусумг 1аторов первого и второго блоков обнаружения ошибок, а вторые входы первых полусумматоров лервого и второго блоков обнаружения ошибок объединены Д1зуг с другом и с первыми входами соответствукядих переключателей первого и второго блоков обнаружения ошибок и являются входом устройства, причем выходы первого и второго блоков обнаружения ошибок подключены соответственно к первым и BTopfcJM входам третьего и четвертого переключателей, к третьим входам которых подключены первый и второй выходы счетного триггера, выход третьего переключателя является выходом ошибки устройства и подключен к первому входу элемента запре со та, к второму входу которого и к входу интегратора подключен выход четвертого Лереключателя а выход интегратора подключен к nepBijjM входам R-S-триггвра и элемента И, к второму ts.. входу которого подключен выход элемента запрета, выход элемента И является выходом проскальзывание СО устройства и подключен к входу счетного триггера, выходы которого под ключены к третьим входам переключа4 телей первого и второго блоков обнаружения ошибок, при этом вход устройСО ства объединен с входом блока обнаружения пропадания сигнала, выход которого подключен к третьему входу элемента И и к второму входу iR-S-триг гера, выход которого является выходом перерыв связи устройства.

Aaei .ввоАш Svraf ./уют

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1976 |

|

SU598226A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Обнаружитель ошибок | 1978 |

|

SU705692A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| . | |||

Авторы

Даты

1983-08-23—Публикация

1982-04-09—Подача