1

Изобретение относится к элетстросвязи и может использоваться в приборах для определения коэффициента ошибок в линейных трактах цифровых систем передачи.

Известен обнаружитель оиибок, содержащий последовательно соединённые переключатель, регистр сдвига и первый полусумматор, выход которого подключен к второму входу переключателя, а также последовательно соединенные второй полусумматор и интегратор ошибок, выход которого подключен к управляющему входу переключателя 1.

Однако этот обнаружитель имеет недостаточную точность обнаружения ошибок.

Цель изобретения - повышение точности обнаружения ошибок. Для этого в обнаружитель ошибок, содержащий последовательно соединенные переключатель, регистр сдвига и первый полусумматор, выход которого подключен к второму входу riepe- ключателя, а также последовательно соединенные второй полусумматор и интегратор ошибок, выход которого подключен к управляющему входу переключателя, введены элемент задержки и преобразователь кода передачи, к входу которого подключен выход первого полусумматора, а выход преобразователя кодапередачи подключен к первому входу второго полусумматора, к второму входу которого подключен выход элемента задержки, вход которого подключен к входу обнару0жителя ошибок.

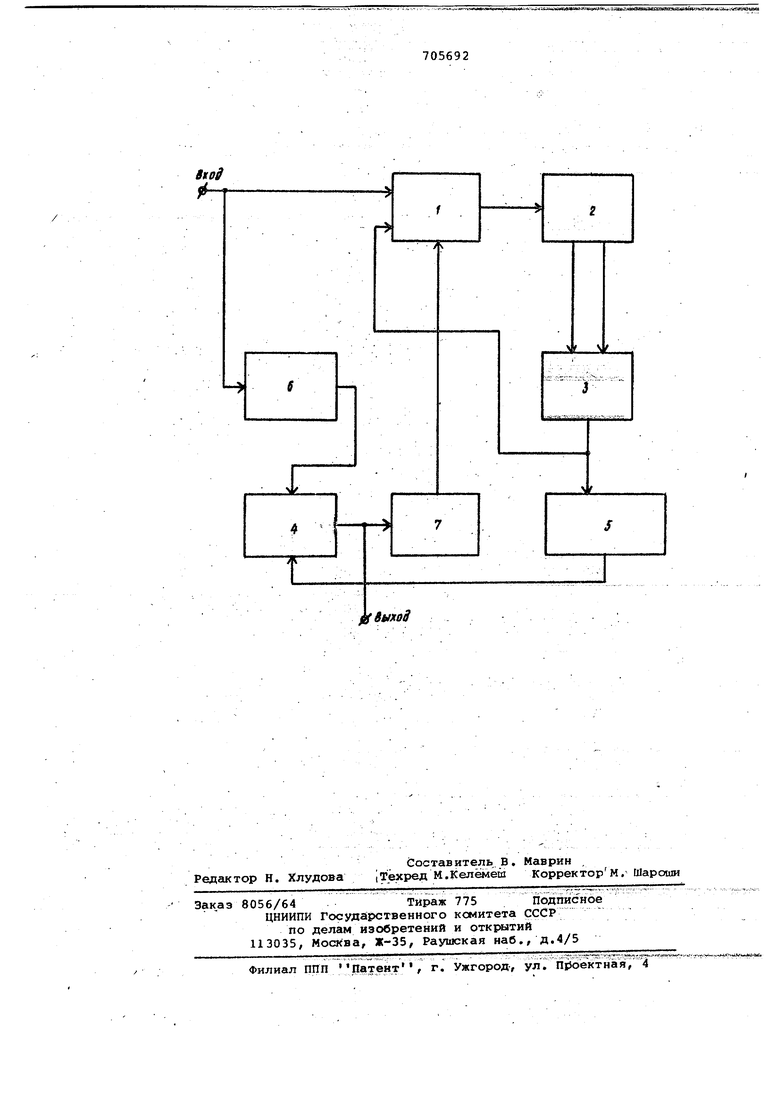

На чертеже приведена --структурная электрическая схема предлагаемого устройства.

Обнаружитель ошибок содержит

5 переключатель 1, регистр 2 сдвига, два полусумматора 3 и 4, преобразователь 5 кода передачи, элемент задержки 6, интегратор 7 ошибок. Устройство работает следующим

0 образом.

Обнаружитель ошибок в зависимости от состояния переключателя 1 может находиться в одном из двух режимов - режиме фазирования или ре5жиме измерения. В режиме фазирования входной сигнал поступает на вход регистра 2 сдвига, а цепь обратной связи между выходом первого полусумматора 3 и входом регистра 2

pa 3 OMK ну та , П ри появ л ё и и и 6; в х од н ом сЙгнале дос;татЬчно длинного отрез1 ау сврбоднсзгр от ошибок и не содержащего кодовых вставок (т.е. отрезка псевдослучайной последовательности (ПСИ), в котором отсутЪтвуют ксмбинации из.п+1 и более последовательных нулей) , на выходе первого пОЭТУСумматора 3 формируется этот же , свободный от кодовых вставок, dtpesbk riCri. Преобразователь 5 кода . передачи на протяжений этого :

J3Tpe3Ka не вводит в ПСП вега11Ш к;6 JEfa il йа ёхОдй вт6рого полусуймато- . ра 4 приходят идентичные и синфазные ПСП (задержка,вносимая преобразователем 5 кода передачи компенсгйруется ёле1йентом задержки б). При этом на выходе второго полусумматоре 4 импульсы ошибок отсутствуют и через время, определяемое постоянной В ремёнй йнтегратора 7 ошибок, переключатель 1 замкнет;цепь обратной

связи между йерйым полусумматором 3 и регистром 2 и отключит вход регистра 2 от входа обнаружителя ошибок. В образованном при этом генера-, торе ПСП будет продолжать формй р6вать он :ПСП, с и нфа 3 йа и с при нймаем.бй ПС П, но не сод ержащая кодовых вставок. При прявЛенин на выходе первого полусумматора 3 отрезков ПСП, содержащих п+1 и более последовательных

нулей, преобразователь 5 кода передачи вводит в эти отрезки кодовые ВеФггйК и, кШ Фйчййё в с т (йТШй:й ляющимся в эти же моменты времени

ё входном сигнале. Такити образом, при отсутствии ошибок в входном сигнале на второй полусумматор 4 поступают идентичные ПСП с идентичными крдовыми вставками и,следовательно, на выходе полусумматора 4 импульсы

отсутствуют/ - - - - Т - --- Появление каждой.ошибки в входном сигнале -вызывает появление ШНуЛьса

705(592

на вьоходе полус 7/1матора 4, являющегося выходом Обнаружители ошибок.

При йарутаёниях нормальной работы (перерыв связи, сбой сйнхЕ)онизации и т.п.) на выходе обнаружителя ошибок возникает пакет импульсов ошибок, переключатель 1, управляемый интегратором 7, переводит обнаружитель ошибок в режим фазирования до появления на входе обнаружителя ошибок Неискаженного сигнала, после чего ассмотренный процесс повторяется.

Формула изобретения ,

Обнаружители ошибок, содержащий последовательно соединенные переключатель, регистр сдвига- и первый полсумматор, выход которого подключен к второму входу переключателя, а также послёдрвдтельно соединенные второй полусумматор и интегратор ошибок, выход которого подключен к управляющему входу переключателя, отличающийс я тем, что, с целью увеличения точности обнаружния ршибок, введены элемент зедержки и преобразователь кода передачи, к входу которого подключен выход первого полусумматора, а выход преобразователя кода передачи подключен к первому входу второго полусумматора, к второму входу которого подключен выход элемента вход Которого подключен к входу обнаружителя ошибок.

Источники информации, принятые вр внимание при экспертизе

1. Гордон Ф.Г- , Нурмухамедов Л.Х О фазированйй датчиков испытательнйХтестов . ЁОпросы радиоэлектрониТехника проводной связи, вып.

ки

6, 1965 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок, проскальзываний и перерывов связи | 1982 |

|

SU1037431A1 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU1010717A1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| Устройство для контроля дуплексного канала связи | 1983 |

|

SU1231621A2 |

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Устройство для контроля дуплексного канала связи | 1982 |

|

SU1061280A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1981 |

|

SU1840033A1 |

| Устройство для определения достоверности передачи бинарной информации | 1984 |

|

SU1229970A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ КОМБИНИРОВАННОГО ПРИМЕНЕНИЯ ДВОЙСТВЕННОГО БАЗИСА ПОЛЯ GF(2) И ВЫДЕЛЕНИЯ "СКОЛЬЗЯЩЕГО ОКНА" С ОШИБКАМИ | 2014 |

|

RU2580806C2 |

| Устройство для обнаружения ошибок | 1974 |

|

SU517173A1 |

esrjir

ЧД -jL-tti - «fri : .

isfeiiii -.iiiiiii ; - - -™ - -.

Авторы

Даты

1979-12-25—Публикация

1978-07-14—Подача