нем с входами установки григгеров выход третьего ключевого злемента соединен со счетны - входом первого триггера j выход которого соеди,неп со счетным входом j3Toporo три.ггера. :з1м-- ход которого соединен с че вертым

входом первого ключевого элемента-. I

3. Устройство по п, 1 j о т л и -- чающееся тем, что обнаружения ошибок содержит буферный регистр, блок полусумматоров, регист синдрома, элемент 1-ШИ-11Е и диа элемента ИЛИд выход первого элемента ИЛИ соеди15ен с первым выходог) блоИзооретение относится к технике .связи и мол::ет быть использовано д.п.я автоматической коррекции ошибо -; при передаче дискретн1 х сооб1цопий

Цель изобретенная -- мовыпенисг быстродействия :

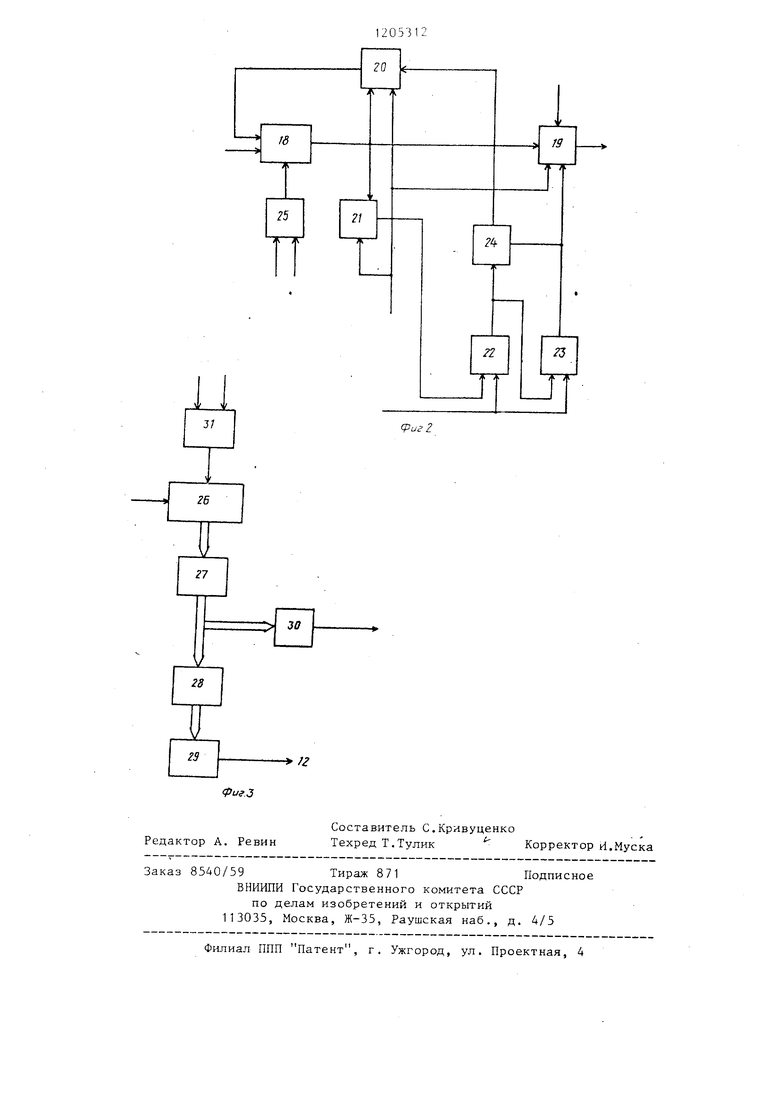

На . изображена с рукт;. рная схема пpeдJ aгaeмoг o устройстпа.; нп фиг, 2 - структурная схема блока формирозан.ия полииомоо .кбэк; п.а фиг, 3 - структурная схема З.нока обнаруже}1ия ош1 бс;к„

Устройство для испразлен ;я и обнаружения ошибок СОл1,ерКИ ОДНОПОрОГОВЫ

блок 1, двуХ11оро1 овый блок 2.буфер- ньй блок 3 памяти:, основной: б.)1о.к ч- памяти, полусумматор 5, первый к.лю- чевой элемент Ь, блок 7 формирс ванил полиномов ошибок, зпеилеит И.Ш Е бло:;; 9 обнаружения ошибок, синхрони:-:а- тор 10, перву:с 11, вт(5рую 12 и третью 13 зыходнью шины, блок 14 кра нения проверочного вектора, втсрой ключевой элемент 15, упраБл;гю1ц;::й триггер 16, коммутатор 17

Блок 7 формирозания иолиномсв оишбок содерлшт регистр 18 полинс:-- ма ошибкИ; кл очез; е элементы 19 21, триггеры 22 и 23, элементы FJlM 24 и 2.5.

Блок 9 обнаружения ошибок ссдар- жит буферный регистр 26, блок 27 полусумматоров, регистр 28 си.ндро- ма, элемент 29, элемепть:: ИЛИ 30 и 31,

51; 2

ка обнаружения ошибок, второй выход которого соединен с выходом элемента H.lil-iiEj входы которого соединены с выхо- г;ами регистре; синдрома , входы которого ;:)ij j.eii,HHeHbi с входами первого элемента ILIH и подключены к выходам блока полу- с .-7 :маторов, вход.ы которого соединены с .выходами буферного регистра, управля гадий вход которого подключен к вь ходу iivoporo элемента Ш1И, которого соединены соответственно с первым и EiTopwM управляющики входами блока обнаружения ошибок, информационный .зход которого соединен с входом буферного рех истра.

Усм ройсл во раоотает с.педуюшим „ |- -рг1аом.

В тродессс: приема слова с первогс м.;:чода СИ нх р О НИЗ а тора 10 подаются

:1 y.-ibcoj; сдви1 а на управляющий буфер-юг о блока 3 памяти, г;;: leijHbie управляющие входы блока 9 of-клрулсеяия ошибок и блока 14 хра- п . проверочного вектора и на уг(1;1аиляющий вход блока 7 форми- ;)оннния Г7о.:1инома ошибок. При этом с;гм1ш.;;|; принимаемого слова последо- ;; rejijj;::o проходя через однопорого- вый блок 1 ,, преобразуются в двоичный

и через буферный блок 3 памяти апигсь.шаютоя в основной блок 4 памя- s :-i, одновременно поступая с выхода : уферного блока 3 памяти через эле- ;-,ент ШШ 8 ка информадионный вход

;;.: ока 9 обнаружения ошибок з где за- м1:::Л;1ваются в буферный регистр 26 и .|;5:.У -у|-:ают на второй вход второго к.- ;оче;зого злемента 15, Одновременно

:.: )и;КОда ДВУХПОрОГОВО ГО 6jJOKa 2 в

;)i;:i-:cTp 18 полинома ошибки блока 7 ;:;и ;мирования полиномов ошибок запи- i::):::5a OTCK двоичные символы , ,«,,., , - 3brpa6aTbiBaeMj)ie двухпороговым бло- i-.jMv: 2 из принимаемых символов о..; , . ,

;.. ПС следу{эщему правилу: 1, С с.пи символ принят ненадежно, т.е. анплитуда соответствующего сиг- нилв имеет зкачение расположенное мекдУ двумя noporoBbttvOi уровнями. У- :: v aHOBneHHbii .ffl в двухпороговом блоке 2. Кроме того, с выхода буферного блока 3 памяти принятое двоичное слово записывается через элемент ИЛИ 8 в буферный регистр 26 блока 9 обнар окения ошибок. В ре- зультаЁте через п тактов в основном блоке 4 памяти оказывается записанным принятое слово, в регистре 18 полинома ошибок блока 7 формирования полиномов ошибок записан двоичный вектор, в котором единицы соответствуют ненадежно принятым символам, а в управляющем триггере 16, к счетному входу которого подключен выход второго ключевого элемента 15, записана величина скалярного произведения над полем QP принятого двоичног слова на проверочный вектор, записанный в блоке 14, представляющим собой регистр сдвига. Величина этого скалярного произведения равна О или 1 в зависимости от того, четное или нечетное число ошибок имеется в принятом слове на позициях, отмеченных единицами в проверочном векторе, который является элементом проверочного пространства используемого линеного кода. Кроме того, на выходе блока 27 полусумматоров в блоке 9 обнаружения ошибки формируется f -разрядный ( 1 - число проверочных символов в коде) синдром слова, записанного в буферном регистре 26 и если синдром равен нулю, то с выхода элемента ИЛИ 30 на ключевой элемент 19 в блоке 7 формирования полиномов ошибок поступает нулевой (запрещающий сигнал), отключающий выход блока 7 формировария полиномов ошибок от полусумматора, а для первого ключевого элемента 6 сигнал оказывается разрешагадим, подготавливая его к выдаче информации на первую выходную шину .11. Если же синдром отличен от нуля, то первый ключевой элемент 6 закрыт, а выход блока 7 формирования полиномов ошибок подключен к входу полусумматора 5.

На следующем этапе декодирования со второго выхода синхронизатора 10 п тактовых импульсов поступают на вторые управляющие входы блока 9 обнаружения ошибок основного блока 4 памяти и блока 14 хранения проверочного вектора, а также на третий управляющий вход блока 7 формирования полиномов ошибок. При этом, если сигнал на выходе блока 9 обнаружения ошибок равен нулю, то кодовая

0

5

0

5

л11Ь ; инация из основного блока 4 памяти через полусумматор 5 и первый ключевой элемент 6 поступает в последовательном коде на первую выходную iiinny 1 1 устройства, одновременно перезаписываясь через полусумматор 5 н основной блок 4 памяти, после чего ояа может быть считана в параллельном, коде на третью выходную шину 13 устройства.

Если же сигнал на выходе блока 9 обнархткения ошибок равен единице, то начинается процесс исправления ошибок. Этот процесс является многоэтапным, причем на очередном этапе с второго выхода синхронизатора 10 поступают h тактовых импульсов на вторые управляющие входы основного блока 4 памяти, блока 9 обнаружения ошибок и блока 14 хранения проверочного вектора, а также на третий управляющий вход блока 7 формирования полиномов ошибок, в результате чего на выходе полусумматора 5 образуется покомпонентная сумма по модулю два принятой комбинации и очередного полинома ошибки, которая записывается в основной блок 4 памяти, и через элемент ИЛИ 8 записывается в буферный регистр 26 блока 9 обнаружения ошибок, после чего на выходе блока 27 полусумматоров формируется сигнал, в зависимости от значения которого либо устройство подготавливается к йьщаче продекодированного слова, либо осуществляется переход к следующему ;зтапу исправления ошибок в принятой комбинации, для чего на четвертый управляющий вход блока 7 формирования полиномов ошибок с третьего выхода синхронизатора 10 поступает импульс, устанавливающий триггеры 22 и 23 в нулевое состояние.

При наличии в принятой комбинации обнар- хткенной, но неисправленной ошибки после завершения всех этапов исправления ошибки в регистре 28 синдрома записывается нулевое слово, в результате чего на выходе элемента ИЛИ-НЕ 29 формируется сигнал обнаружения ошибки, поступакщий на вторую выходную шину 12 устройства.

0

5

0

После окончания декодирования 55 принятой комбинации путем установки всех триггеров в исходное состояние устройство переходит в режим ожидания следующего слова.

s

При исправлении ошибки чис:ло этапов декодирования равно в среднем не половине числа ненаде)Е;ко при пятых символов, а оказывается: в ере. нем вдвое меньше. Это объясня ется тем, что при выполнении проверки Ь записанной в блоке 4 хранения проверочного вектора э в процессе деко-- дирования используются толькс поли- HOMbij соответствующие ненадежно принятым симво.аам, ке входящим Е проверку 1 J в противном случае испол зуются только полиномь, соответствующие ненадежно прршятым символам,, входящим в проверку h , Например о при использовании линейного кода (14.7) длины 14 с проверо1-;Ной матрицей

Н J-,,

в р;; честне проверочног о вектора 1может бь;ть выбран вектор h , рав- - ):й сумь1 е первых двух строк матрицы 1-ц т.е. h (10111001100000). Если при этом вектор, в котором единицы С оответствуют ненадежно принятым символам; имеет вид С (10011010001010), то в устройстве ;н процессе исправления ошибки будет 1:ос; едовательно формироваться либо :;.олиномь1 X X , Х , если скалярное г. роизведение принятой двоичной комби- }:ации на проверочный вектор i равно I ,. либо поликомы X , X , X в противном случае, т.е. число этапов декоди- рсаания ,в процессе исправления ошиб- K:i йудет в данном случае вдвое мень- , Так как одиночная ошибка может равновероятно располагаться на любой .сзиции принятой комбинации при ;аличии в проверочном векторе h ров- :;о половины единиц время декодировали;;: одного слова уменьщается примерно вдвое.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для исправления ошибок | 1986 |

|

SU1387202A2 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| Устройство для коррекции ошибок в блоках памяти | 1982 |

|

SU1086460A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Устройство декодирования линейногоциКличЕСКОгО КОдА | 1979 |

|

SU809568A1 |

Редактор А. Ренин

Составитель С.Кривуценко

Техред Т.Тулик Корректор И.Муска

8540/59Тираж 871Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

| Устройство для исправления ошибок в кодовой комбинации | 1976 |

|

SU599267A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-15—Публикация

1984-06-13—Подача