дом четвертого элемента И,м через третий элемент задержки с входом синхронизации регистра кода проверяемого участка, выходы поля первой и второй метки регистра микрокоманд соединены соответственно с вторым и .третьим входами четвертого элемента И, выход которого соединен с управляющим входом схемы сравнения,, выходы второго поля кода модификации адреса регистра микрокоманды и выходы регистра кода проверяемого участка микрокоманды соединены соответственно с первым и вторым информационными входами схемы сравнения, выход которой является управляющим выходом устройства, выходы счетчика соединены с входами деши(ратоj a, выходы которого соединены с управляющими входами коммутатора, информационные входы которого соединены с выходами поля микроопераций, поля кода проверяемых логических условий и первого поля кода модификации адреса регистра микрокоманд, выходы коммутатора соединены со счетными входа((и регистра кода проверяei«(x участков микрокоманды, выход элемента И первой группы сортветству- ющей микрооперации Конец микропрограммы через четвертый элемент задержки соединен с нулевыми входами регистра кода проверяемых участков микрокоманды, счетчика и регистра микрокоманд

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

Изобретение относится к вычислительной технике и может быть исполь зовано при проектировании устройств управления ЭВМ..

Известно микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, узел формирования адреса, схему выброса и элемент задержки С Недостатками этого устройства являются низкие экономичность, быстродействие и достоверность функционирования. Низкая экономичность устройства обусловлена большой избыточностью блока памяти микрокоманд. Низкое быстродействие устройства обусловлено тем, что до окончания проверки выполнения ждущего логического условия микропрограммное устройство управления простаивает и очередная микрокоманда с блока памяти микрокоманд не считывается. Низкая достоверность функционирования устройства обусловлена отсутствием контроля правильности считывания микрокоманд.

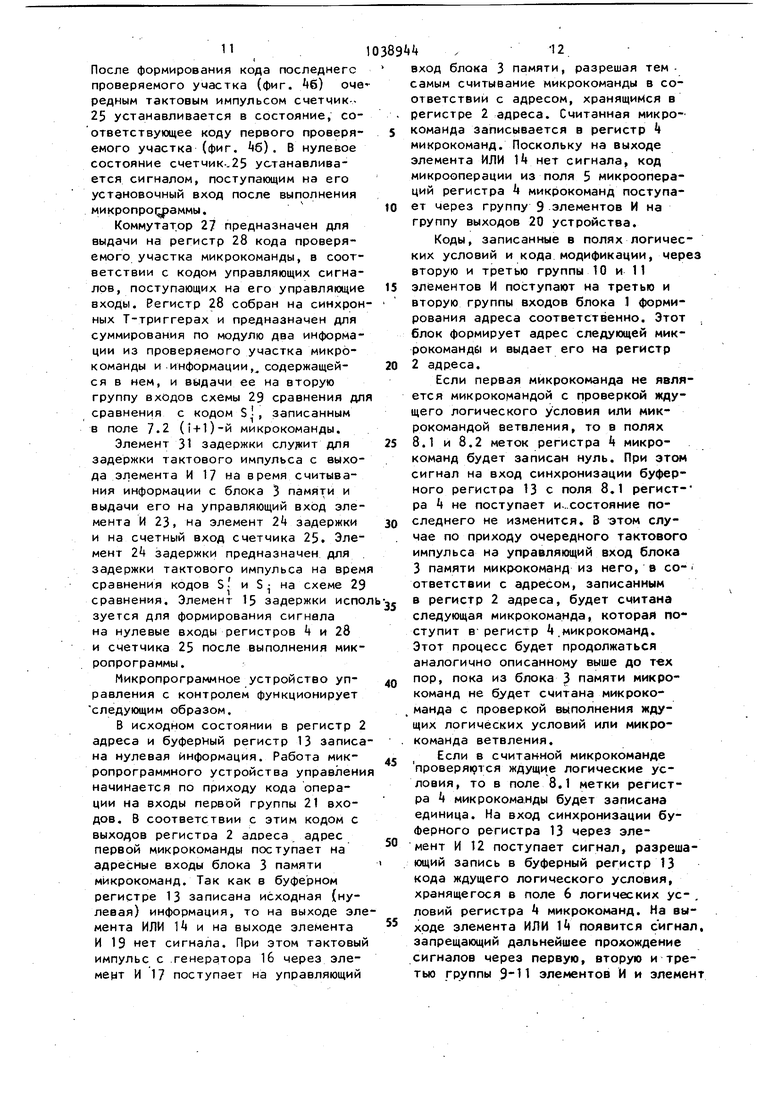

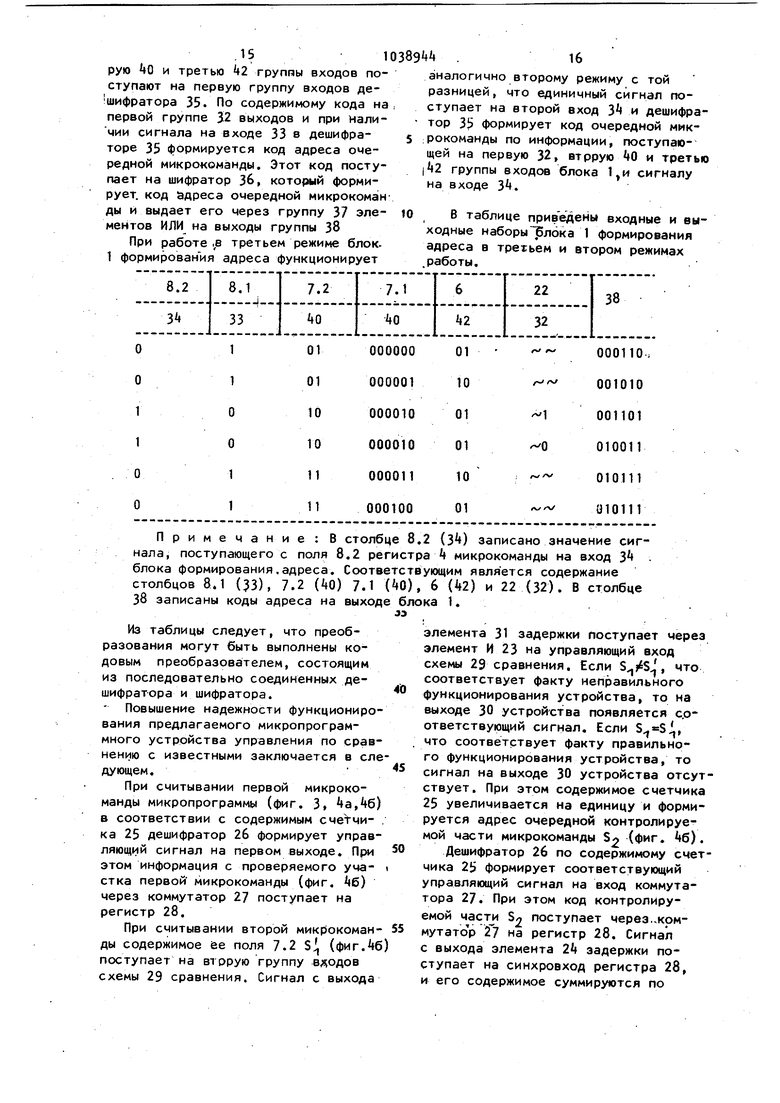

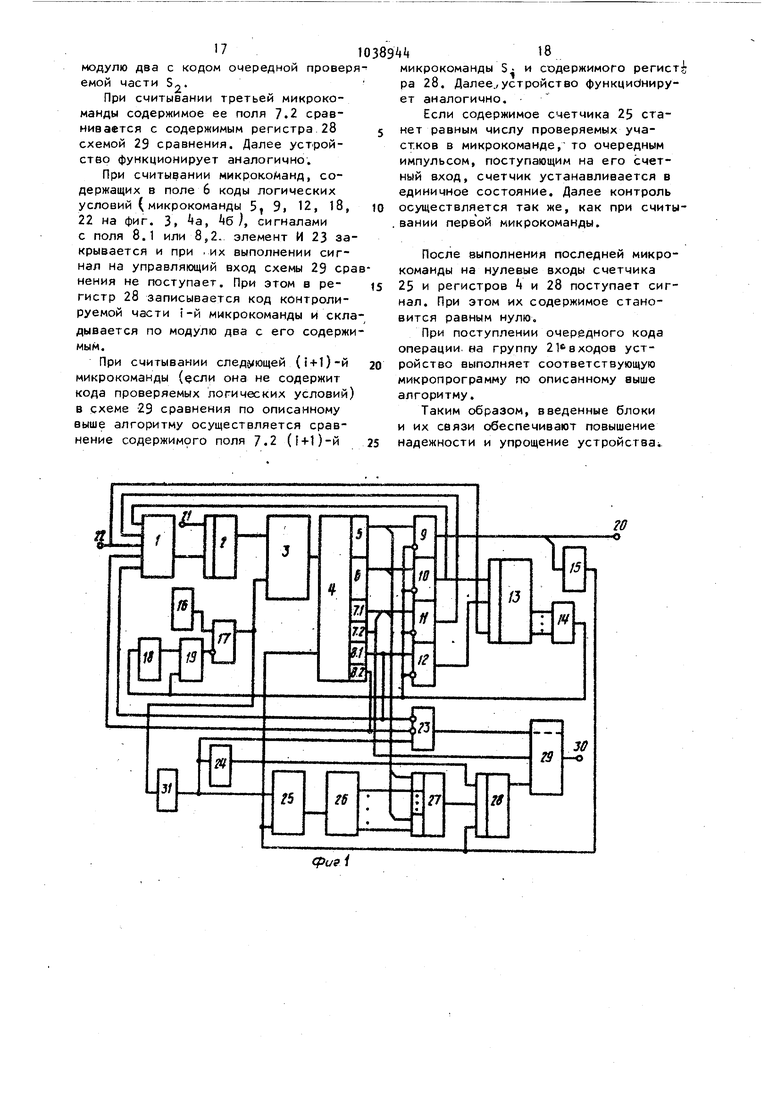

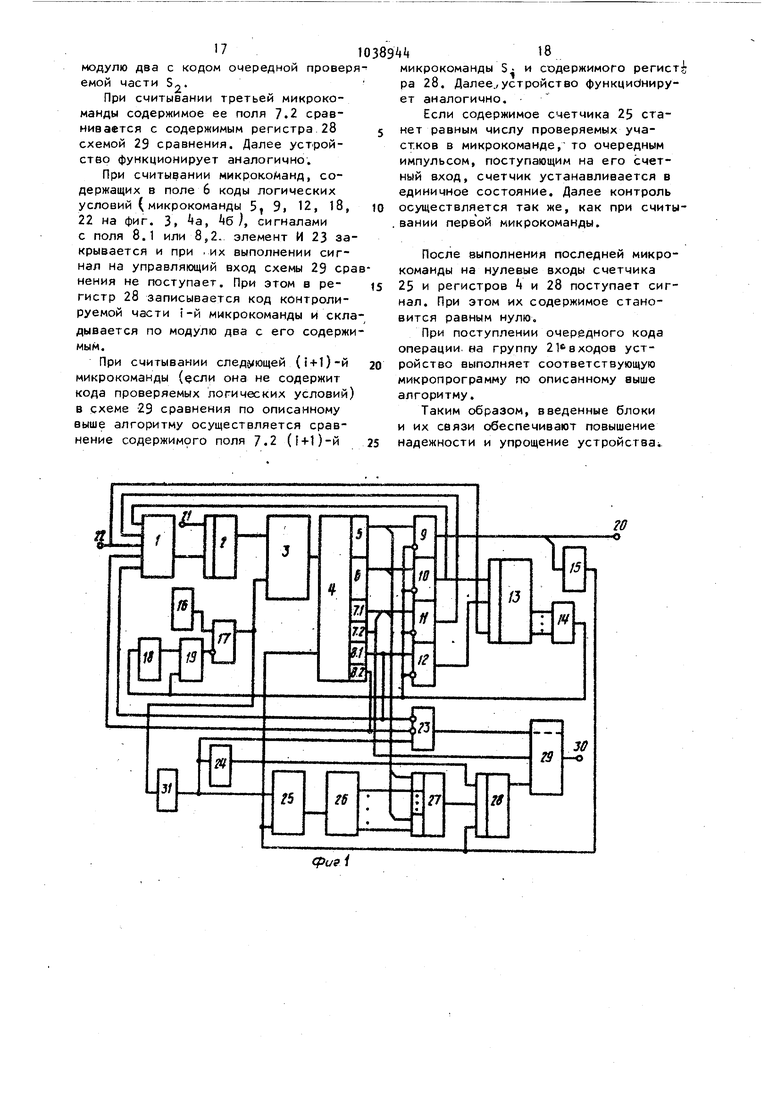

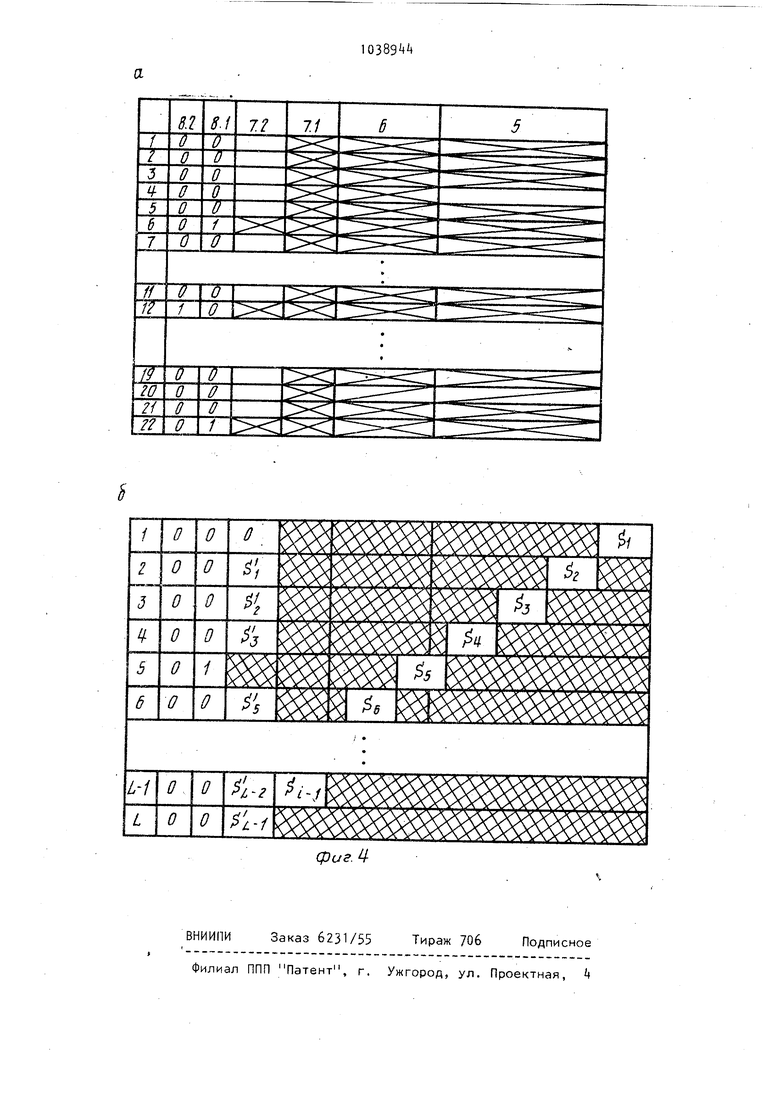

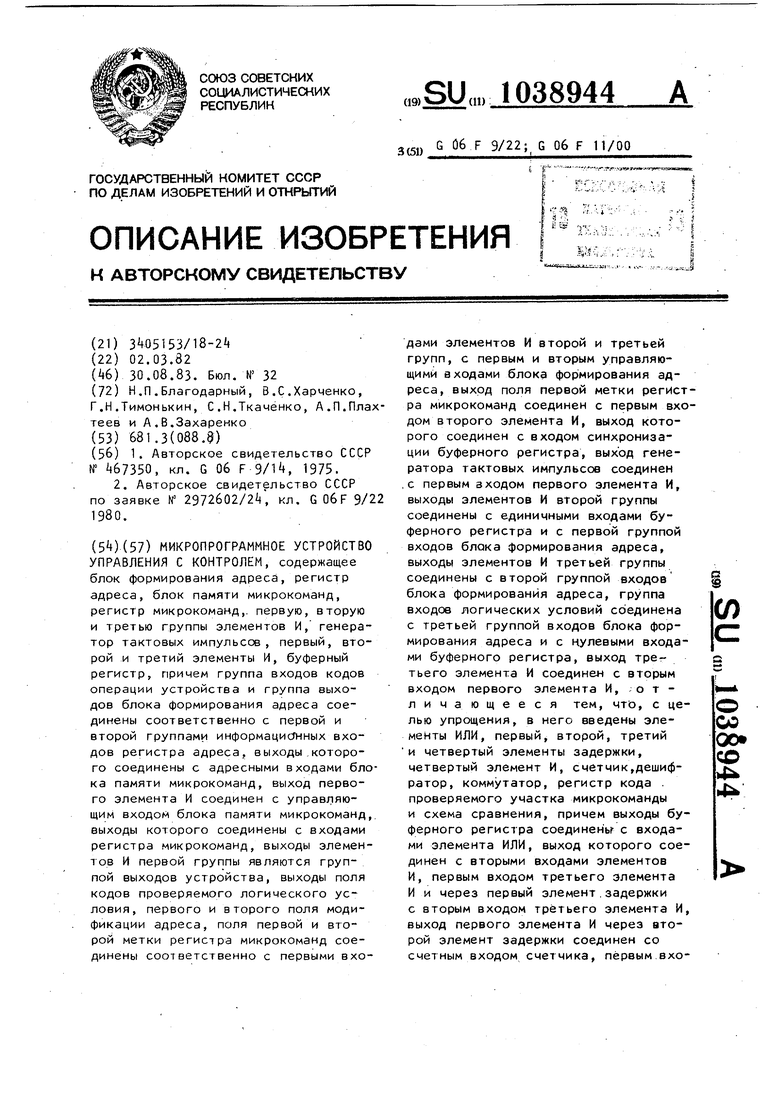

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является программное устройство управления, содержащее узел формирования адреса, регистр адреса, блок памяти микрокоманд, регистр микрокоманд, первую, вторую и третью группы элементов И, генератор тактовых импульсов, первый, второй и третий элементы И, буферный регистр, причем первая группа входов устройства соединена с первой группой входов регистра адреса, вторая группа входов которого соединена с выходами узла формирования адреса, а выходы - с адресными входами блока памяти микрокоманд, управляющий вход которого соединен с выходом первого элемента И, а выходы - с информационными входами .регистра микрокоманд, выходы поля мик рсопераций которого соединены с информационными входами первой группы элементов И,выходы поля кода проверяемого логического условия соединены с информационными входами второй группы элементов И, выходы первого и второго поля кода модификации адреса соединены с информационными входами третьей группы элементов И, выход поля первой метки соединен с первым входом второго элемента И и первым входом узла формирования адреса, выход,поля второй метки соединен с вторым входом узла фрмирования адреса, первая группа входов которого соединена с второй группой входов устройства и R-входами буферного регистра, вторая группа входов с выходами третьей группы элементов И, а третья группа входов - с выходами второй группы элементов И и S-входами буферного регистра, вход синхронизации которого соединен с выходом второго элемента И, выходы первой группы элементов И соединены с группой выходов устррй ства, выход генератора тактовых импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом третьего элемента И С2 . Недостатками известного устройства являются низкая надежность и аппаратурная избыточность. Аппаратурная избыточность обусловле на те что для придания устройству возмож ности реализации микропрограмм, со держащих микрокоманды со ждущими л гическими условиями, функциональная схема устройства содержит два элемента памяти. Кроме того, для о ределения момента выполнения ждущи логических условий используется сх ма формирования сигнала конца ожид ния, имеющая сложную внутреннюю ст туру. Низкая надежность устройства об словлена отсутствием контроля правильности считывания микрокоманд микропрограммным устройством управления и правильности перехода к данной микрокоманде от предыдущей. Указанные недостатки ограничива область применения устройства-прот типа и его функциональные возможности. Цель изобретения - повышение на дежности микропрограммного устройства управления с контролем и его упрощение. Поставленная цель достигается т что в микропрограммное устройство управления с контролем, содержащее блок формирования адреса, регистр адреса, блок памяти микрокоманд, регистр микрокоманд, первую, ётору и третью группы элементов И, генератор тактовых импульсов, первый, второй и третий элементы И, буферный регистр, причем группа входов кодов операции устройства и группа выходов блока формирования адре са соединены соответственно с перв и второй группами информационных входов регистра адреса, выходы торого соединены с адресными входами блока памяти микрокоманд, выход первого элемента И соединен с управляющим входом блока памяти микрокоманд, выходы которого соединены с входами регистра микрокоманд, выходы элементов И первой группы являются группой выходов устройства, выходы поля кодов проверяемого логического условия, первого и второго поля модификации адреса, поля первой и второй метки регистра микрокоманд соединены соответственно с первыми входами элементов И второй , тр§11)ей групп, с первым и вторым управляющими входами блока формирования адреса, выход поля первой метки регистра микрокоманд соединен с первым входом второго элемента И, выход которого соединен с вхо4 дом синхронизации буферного регистра, выход генератора тактовых импульсов соединен с первым входом первого элемента И, выходы элементов И второй группы соединены с единичными входами буферного регистра и с первой группой входов блока фор мирования адреса, %1ходы элементов И третьей группы соединены с второй группой входов блока формирования адреса, группа входов логических условий соединена с третьей группой входов блока формирования адреса и с нулевыми входами буферного регистра, выход третьего элемента И соединен с вторым входом первого элемента И, введены элемент ИЛИ, первый, второй, третий и четвертый элементы задержки, четвертый элемент И, счетчик, дешифратор, коммутатор, регистр кода проверяемого участка микрокоманды и сосема у сравнения, причем выходы буферного регистра соединены с входами элемента ИЛИ, выход которого соединен с вторыми входами элемептов И первой. второй и третьей групп, с вторым входом второго элемента И, с первым входом третьего элемента И и через первый элемент задержки с вторым входом третьего элемента И, выход первого элемента. И через второй элемент задержки соединен со счетным входом счетчика, первым входом четвертого элемента И и через третий элемент задержки с входом синхронизации регистра кода проверяемого участка, выходы поля первой и второй метки регистра микрокоманд соединены соответственно с вторым и третьим входами четвертого элемента И, выхо которого соединен с управляющим вхо дом схемы сравнения, выходы второго поля кода модификации адреса регист ра микрокоманд и выходы регистра ко да проверяемого участка микрокоманды соединены соответственно с первы и вторым информационными входами схемы сравнения, выход которой явля ется управляющим выходом устройства выходы счетчика соединены с входами дешифратора, выходы которого соединены с управляющими входами коммута тора, информационные входы которого соединены с выходами поля микроопер ций, поля кода проверяемых логических условий и первого поля кода модификации адреса регистра микрокоманд, выходы коммутатора соединены со счетными входами регистра кода проверяемых участков микрокоманды, выход элемента И первой группы соот ветствующей микрооперации Конец микропрограммы через четвертый эле мент задержки соединен с.нулевыми входами регистра кода проверяемых участков микрокоманды, счетчика и регистра микрокоманд. Сущность изобретения состоит а уменьшении аппаратурной избыточности микропрограммного устройства упрёвления путем упрощения его структуры при сохранении реализуемых им функций, а также в повышении надежности его функционирования путем проверки правильности выполнения устройством функций переходов и выходов в процессе работы. Благодаря использованию того, что второе поле кода модификации адреса занято полезной информацией только в точках ветвления микропрограммы и свобрдно при выполнении остальных микрокоманд, т.е. на линейных участках микропрограммы, в предлагаемом устройстве осуществляется контроль правильности выполнения фун ций переходов и выходов. При этом контролируемый участок i-и микрокоманды S- запоминается в регистре кода проверяемого участка микрокоманды на один такт. Во втором поле модификации адреса (+)-й микрокоманды записан код S ., который равен коду S-, При считывании (|+1)-й микрокоманды в схеме сравнения производится Сравнение кодов S| Есл микропрограммное устройство равления функционирует правильно, то . Если микропрограммное устройство управления искажает функцию переходов или функцию выходов, то схемой сравнения эти факты будут обнаружены. Введение элемента ИЛИ и обусловленных им связей позволяет формировать сигнал при нахождении в буферном perkicTpe ненулевой информации. Введение первого элемента задержки и обусловленных им связей позволяет осуществить задержку сигнала с выхода элемента ИЛИ на время, необходимое для подачи на управляющий вход блока памяти микрокоманд устройства одного тактового импульса. Соединение выхода элемента ИЛИ с управляющими входами элементов И первой, второй и третьей групп и вторым входом второго элемента И позво-. ляет управлять передачей информации с выходов регистра микрокоманд на остальные элементы устройства, Сое|динение выхода элемента ИЛИ с входом первого элемента задержки и входом третьего элемента И позволяет управлять выдачей тактовых импульсов через первый элемент И и на управляющий вход блока памяти микрокоманд. Введение второго элемента задержки позволяет задерживать тактовый импульс на время считывания микрокоманды из блока памяти и записи ее в регистр микрокоманд. Введение третьего элемента задержки позволяет формировать сигнал на выходе после исчезновения сигнала на выходе второго элемента задержки. Введение счетчика позволяет формировать код номера проверяемого участка считанной микрокоманды. Введение дешифратора и обусловленных им связей позволяет формировать по содержимому счетчика двоичный позиционный код номера проверяемого участка считанной микрокоманды и .выдачи его на управляющие входы коммутатора. Введение коммутатора и обусловленных им связей позволяет в соответствии с кодом на управляющих входах передавать информацию с проверяемого участка считанной микрокоманды на входы регистра кода проверяемого участка микрокоманды. Введение регистра кода проверяемого участка микрокоманды позволяет хранить код проверяемого участка микрокоманды. Вве-. дение схемы сравнения позволяет осуществлять сравнение кодов, поступающих на первую и вторую группу ее входов, и выдавать при их несравнеНИИ выходной сигнал на первый выход устройства. Введение четвертого эле мента задержки и обусловленных им связей позволяет формировать сигнал обнуления регистра микрокоманд, сче чика и регистра кода проверяемого участка микрокоманды после выполнения микропрограммы. На фиг. 1 представлена функционал ная схема микропрограммного устройства управления с контролем; на фиг функциональная схема блока формиров ния адреса; на фиг, 3 пример микррпрограммы, реализуемой устройством; на фиг. 4 - примеры заполнения полезной информацией микрокоманды (а) и организации контроля правильности выполнения микропрограммным устройством управления функций пере ходов и выходов (б). Устройство содержит (фиг. 1) бл 1 формирования адреса, регистр 2 ад реса, блок 3 памяти микрокоманд, регистр k микрокоманд ,с полем 5 мик роопераций, полем 6 логических усло вий, первым полем 7.1 кода модификации адреса, вторым полем 7.2 кода модификации адреса, полем 8.1 первой метки, полем 8.2 второй метки, первую группу 9 элементов И, вторую группу 10 элементов И, третью группу 11 элементов И, второй элемент И 12, буферный регистр .13, элемент ИЛИ 14, четвертый элемент 15 задержки, генератор 16 тактовых импульсов, первый элемент И 17, первый элемент 18 задержки, третий элемент И 19, группу 20 выходов микроопераций, первую группу 21 вхо дов, вторую группу 22 входов , четвер тый элемент И 23, третий элемент 2 задержки, счетчик 25, дешифратор 26, коммутатор 27, регистр 28 кода проверяемого участка микрокоманды, схему 29 сравнения, первый выход 30 устройства, а также второй элемент задержки. На фиг. 2 обозначены входы перво группы 32 входов, первый 33 и второй З входы блока, 1 формирования адреса, дешифратор 35, дешифратор З группа 37 элементов ИЛИ, группа 38 выходов блока формирования адреса, элемент ИЛИ 39, входы второй груплы 40 входов, первая группа 1 элеУ ентов И, входы третьей группы 42 входов и вторая группа 3 элементов И. На фиг. 3 обозначены содержимое поля 8.2 второй метки, поля 8.1 первой метки, второго поля 7.2 кода модификации адреса, первого поля 7.1 кода модификации адреса поля ,6 логических условий и поля 5 микроопераций считываемой микрокоманды соответственно, где AJ код адреса (+1)-й микрокоманды, А - базовый адрес очередной микрокоманды, выполняемой после i-й микрокоманды вет4 вления при проверке ждущего, логимеского условия. А,- базовый адрес очередной микрокоманды, выполняемой после i-и микрокоманды . ветвления при проверке неждущего логического условия, L -L-2 «оды микроопераций, формируемые при считывании микрокоманд, X , Хл проверяемые логические (ждущие и неждущие) условия. s обозначает контрольНа фиг. t записанный во втором поле ный код, 7.2 кода модификации адреса и используемый для проверки функций переходов и функции выходов при считывании после (-1)-й микрокоманды 1-й микрокоманды S - проверяемый участок i-й микрокоманды при считывании (+1)-й микрокоманды. Блок 1 формирования адреса предназначен для формирования адреса очередной микрокоманды в соответствии с содержимым поля 6 логического условия , полей 7.1 и 7.2 кода модификэции, регистра , сигналами логических условий, поступающими с группы 22 входов устройства и сигналами меток с первого 8.1 и второго 8.2 полей меток регистра 4. Регистр 2 адреса служит для хранения адреса микрокоманды, сформированного блоком 1 формирования адреса и выданного на адресные входы блока 3 памяти. Блок 3 памяти микрокоманд предназначен для хранения и выдачи микрокоманд в регистр 4 микрокоманд в соответствии с адресом, поступающим на его адресные .входы с регистра 2 при наличии тактового импульса на управляющем входе.. Регистр 4 микрокоманд используется для хранения микрокоманды, считанной из блока 3 памяти. При этом в поле 5 микроопераций хранится . 9 код микрооперации, в поле 6 логических условий хранится код логичес ких условий (в микрокомандах ветвле ния} или часть адреса очередной мик рокоманды, которая формируется после выполнения текущей, в первом поле 7.1 кода модификации адреса хранится ч стькода адреса, которая совместно с частью кода адреса, хранящегося в поле 6, составляет адрес очередной микрокоманды. Если микрокоманда не является ми рокомандой ветвления, то адрес следующей микрокоманды определяется непосредственно содержимым полем 6 и 7.1 регистра микрокоманды t. Ес ли микрокоманда является микрокомандой проверки ждущего логического условия, то в поле 8.1 первой метки записана единица (в остальных случаях ее содержимое нулевое), в поле 6 - код проверяемого логического условия, в полях 7.1 и 7,2 код базового адреса очередной микрокоманды. Если микрокоманда является микрокомандой ветвле ния (например, микрокоманда 12 на фиг.З) то в поле 6 записан код проверяемого неждущего логического условия (Х), в полях 7.1 и 7.2 - код базового адреса очередной микрокоманды а в поле 8.2 - единичный сигнал (в микрокомандах, не являющихся микрокомандами ветвления, в этом поле записан нуль). В поле 7,2 микрокоманд, не являющихся микрокомандами ветвления и проверки ждущих логических условий, записан код (фиг. ) . Первая группа 9 элементов И пред назначена для выдачи кода микроопераций на группу 20 выходов устройства только в том случае, ес ли на выходе элемента ИЛИ 1 нет сигнала. Вторая группа 10 элементов И служит для выдачи кода логических условий на блок 1 формирования адреса и кода ждущего логического условия на S-входы буферного регистра 13 только в том случае, ес ли на выходу элемента ИЛИ 1k нет сигнала. Третья группа 11 элементов И предназначена для выдачи кода модификации адреса с полей 7.1 и 7.2 регистра,4 микрокоманды на блок 1 формирования адреса только в том случае, если на выходе элемента ИЛИ И нет сигнала. 4 Элемент И 12 используется для выдачи сигнала о наличии ждущего элемента условия в данной микрокоманде на вход синхронизации буферного регистра 13 только в том случае, если на выходе элемента ИЛИ 1 нет сигнала. Буферный регистр 13 предназначен для хранения кода ждущих логических условий, а также информации об их выполнении ( путем стирания в соответствующих разрядах регистра 1.3, т.е. записи в них Q ), Элемент ИЛИ Н служит для выдачи сигнала в тех случаях, когда хотя бы в одном Ti3 разрядов буферного регистра 13 запис ана единица. Элемент 18 задержки предназначен :для задержки сигнала с выхода элемента ИЛИ I на время, необходимое для подачи на управляющий вход блока 3 памяти одного и только одного тактового импульса. Элемент И 19 используется для выдачи сигнала, разрешающего прохождение тактовых импульсов, только в тех случаях, когда хотя бы на одном из его входов нет сигнала. Элемент И 17 предназначен для разрешения прохождения тактовых импульсов с выхода генератора 16 только в том случае, если на выходе эле- мента И 19 нет сигнала. Первая группа 21 входов устройства служит для подачи в устройство кода операции. Группа 20 выходов устройства предназначена для выдачи кодов микроопераций на управляемые объекты. Вторая группа 22 входов устройства предназначена для подачи в устройство сигналов проверяемых логических условий. Генератор 16 тйктовых импульсов предназначен для подачи в устройство тактовых импульсов. Элемент-И 23 используется для формирования сигнала на управляющий вход схемы 29 соавнения. Схема 2 сравнения предназначена для сравнения кодов S- и S; (фиг. б)при выполнении i-й микрокоманды и при наличии сигнала на управляющем входе и выдачи сигнала на выход 30 при их несравнении. Счетчик 25 предназначен для формирования коданомера проверяемого участка 5 и выдачи его на дешифратор 26, который при этом формирует двоичный позиционный код номера проверяемого участка S- микрокоманды и выдает его на соответствующий управляющий вход коммутатора 27.

После формирования кода последнего проверяемого участка (фиг. 6) очв редным тактовым импульсом счетчик25 устанавливается в состояние, соответствующее коду первого проверяемого участка (фиг. б) . В нулевое состояние счетчик-.25 устанавливается сигналом, поступающим на его установочный вход после выполнения микpoпpoq.paммы.

Коммутатрр 27 предназначен для выдачи на регистр 28 кода проверяемого участка микрокоманды, в соответствии с кодом управляющих сигналов, поступающих на его управляющие входы. Регистр 28 собран на синхронных Т-триггерах и предназначен для суммирования по модулю два информации из проверяемого участка микрокоманды и информации, содержащейся в нем, и выдачи ее на вторую группу входов схемы 29 сравнения для сравнения с кодом S , записанным в поле 7.2 (1+1)-й микрокоманды.

Элемент 31 задержки служит для задержки тактового импульса с выхода элемента И 17 на время считывания информации с блока 3 памяти и выдачи его на управляющий вход элемента И 23, на элемент 2k задержки и на счетный вход счетчика 25. Элемент 2 задержки предназначен для задержки тактового импульса на время сравнения кодов S- и S на схеме 29 сравнения. Элемент 15 задержки испол зуется для формирования сигнала на нулевые входы регистров t и 28 и счетчика 25 после выполнения микропрограммы.

Микропрограммное устройство управления с контролем функционирует следующим образом.

В исходном состоянии в регистр 2 адреса и буферный регистр 13 записана нулевая информация. Работа микропрограммного устройства управления начинается по приходу кода операции на входы первой группы 21 входов. В соответствии с этим кодом с выходов регистра 2 адреса адрес первой микрокоманды поступает на адресные входы блока 3 памяти микрокоманд. Так как в буферном регистре 13 записана исходная (нулевая) информация, то на выходе элемента ИЛИ Н и на выходе элемента И 19 нет сигнала. При этом тактовый импульс с .генератора 16 через элемемт И 17 поступает на управляющий

вход блока 3 памяти, разрешая тем самым считывание микрокоманды в соответствий с адресом, хранящимся в регистре 2 адреса. Считанная микрокоманда записывается в регистр k микрокоманд. Поскольку на выходе элемента ИЛИ И нет сигнала, код микрооперации из поля 5 микроопераций регистра k микрокоманд поступает через группу 9 элементов И на группу выходов 20 устройства.

Коды, записанные в полях логических условий и кода модификации, чер вторую и третью группы 10 и 11 элементов И поступают на третью и вторую группы входов блока 1 формирования адреса соответственно. Этот блок формирует адрес следующей микрокомандб и выдает его на регистр

2адреса.

Если первая микрокоманда не является микрокомандой с проверкой ждущего логического условия или микрокомандой ветвления, то в полях 8.1 и 8.2 меток регистра k микрокоманд будет записан нуль. При этом сигнал на вход синхронизации буферного регистра 13 с поля 8.1 регистра не поступает и...состояние последнего не изменится, В этом случае по приходу очередного тактового импульса на управляющий вход блока

3памяти микрокоманд из него, в соответствии с адресом, записанным

в регистр 2 адреса, будет считана следующая микрокоманда, которая поступит в регистр .микрокоманд. Этот процесс будет продолжаться аналогично описанному выше до т«х пор, пока из блока 3 памяти микрокоманд не будет считана микрокоманда с проверкой выполнения ждущих логических условий или микрокоманда ветвления.

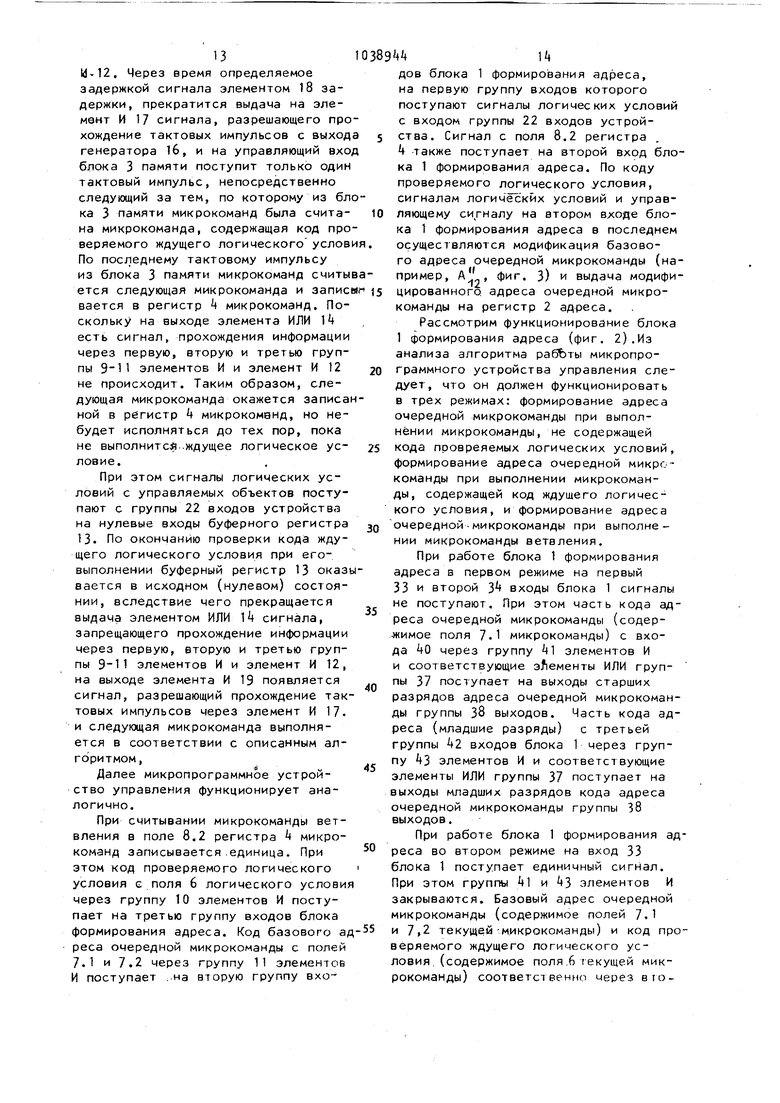

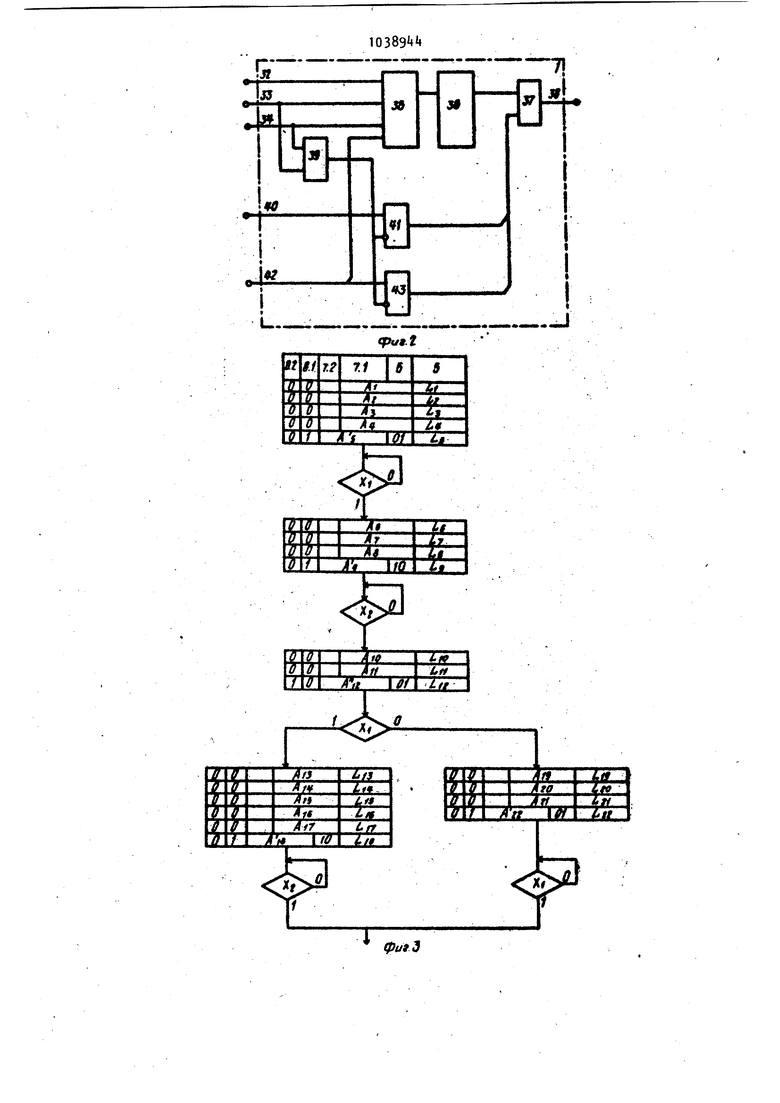

Если в считанной микрокоманде проверяются ждущие логические условия, то в поле 8.1 метки регистра Ц микрокоманды будет записана единица. На вход синхронизации буферного регистра 13 через элемент И 12 поступает сигнал, разрешающий запись в буферный регистр 13 кода ждущего логического условия, хранящегося в поле 6 логических условий регистра t микрокоманд. На выходе элемента ИЛИ I появится сигна запрещающий дальнейшее прохождение сигналов через первую, вторую и третью группы элементов И и элеме td-12. Через время определяемое задержкой сигнала элементом 18 задержки, прекратится выдача на элемент И 17 сигнала, разрешающего про хождение тактовых импульсов с выход генератора 1б, и на управляющий вхо блока 3 памяти поступит только один тактовый импульс, непосредственно следующий за тем, по которому из бл ка 3 памяти микрокоманд была считана микрокоманда, содержащая код про веряемого ждущего логическогоуслов По последнему тактовому импульсу из блока 3 памяти микрокоманд считы ется следующая микрокоманда и запис вается в регистр микрокоманд. Поскольку на выходе элемента ИЛИ 1 есть сигнал, прохождения информации через первую, вторую и третью группы 9-П элементов И и элемент И 12 не происходит. Таким образом, следующая микрокоманда окажется записа ной в регистр 4 микрокоманд, но небудет исполняться до тех пор, пока не выполните .ждущее логическое услоаие. При этом сигналы логических условий с управляемых объектов поступают с группы 22 входов устройства на нулевые входы буферного регистра 13. По окончанию проверки кода ждущего логического условия при еговыполнении буферный регистр 13 оказ вается в исходном (нулевом) состоянии, вследствие чего прекращается выдача элементом ИЛИ 14 сигнала, запрещающего прохождение информации через первую, вторую и третью группы 9-11 элементов И и элемент И 12, на выходе элемента И 19 появляется сигнал, разрешающий прохождение так товых импульсов через элемент И 17. и следующая микрокоманда выполняется в соответствии с описанным алгоритмом. Далее микропрограммное устройство управления функционирует аналогично. При считывании микрокоманды ветвления в поле 8.2 регистра микрокоманд записывается .единица. При этом код проверяемого логического условия с поля 6 логического условия через группу 10 элементов И поступает на третью группу входов блока формирования адреса. Код базового ад реса очередной микрокоманды с полей 7.1 и 7.2 через группу 11 элементов И поступает ..на вторую группу входов блока 1 формирования адреса, на первую группу входов которого поступают сигналы логических условий с входом группы 22 входов устройства. Сигнал с поля 8.2 регистра k также поступает на второй вход блока 1 формирования адреса. По коду проверяемого логического условия, сигналам логичё ких условий и управляющему си гналу на втором влоде блока 1 формирования адреса в последнем осуществляются модификация базового адреса очередной микрокоманды (например, А , фиг. 3) и выдача модифицированного адреса очередной микрокоманды на регистр 2 адреса. Рассмотрим функционирование блока 1 формирования адреса (фиг. 2).Из анализа алгоритма микропрограммного устройства управления следует, что он должен функционировать в трех режимах: формирование адреса очередной микрокоманды при выполнении микрокоманды, не содержащей кода провреяемых логических условий, формирование адреса очередной микрокоманды при выполнении микрокоманды, содержащей код ждущего логического условия, и формирование адреса очередной-микрокоманды при выполнении микрокоманды ветвления. При работе блока 1 формирования адреса в первом режиме на первый 33 и второй 3 входы блока 1 сигналы не поступают. При этом часть кода адреса очередной микрокоманды (содержимое поля 7.1 микрокоманды) с входа 40 через группу 41 элементов И и соответствующие э51ементы ИЛИ группы 37 поступает на выходы старших разрядов адреса очередной микрокоманды группы ЗЗ выходов. Часть кода адреса (младшие разряды) с третьей группы 42 входов блока 1 через группу 43 элементов И и соответствующие элементы ИЛИ группы 37 поступает на выходы младших разрядов кода адреса очередной микрокоманды группы 38 выходов, При работе блока 1 формирования адреса во втором режиме на вход 33 блока 1 поступает единичный сигнал, При этом группы 41 и 43 элементов И закрываются. Базовый адрес очередной микрокоманды (содержимое полей 7.1 и 7,2 текущей-микрокоманды) и код проверяемого ждущего логического условия, (содержимое поля .6 текущей микрокоманды) соответственно через в ю.151 рую 0 и третью +2 группы входов поступают на первую группу входов дешифратора 35. По содержимому кода на первой группе 32 выходов и при наличии сигнала на входе 33 в дешифраторе 35 формируется код адреса очередной микрокоманды. Этот код поступает на шифратор Зб, который формирует, код адреса очередной микрокомаи ды и выдает его через группу 37 элементов ИЛИ на выходы группы 38 При работе ,8 третьем режиме блок. 1 формирования адреса функционирует

Примечание: В столбце 8.2 (З) записано значение сигнала, поступающего с поля 8.2 регистра t микрокоманды на вход З блока формирования.адреса. Соответствующим является содержание столбцов 8.1 (33), 7.2 (40) 7.1 Ш}, 6 (k2} и 22 (32). В столбце 38 записаны коды адреса на выходе блока 1.. Из таблицы следует, что преобразования могут быть выполнены кодовым преобразователем, состоящим из последовательно соединенных дешифратора и шифратора. Повышение надежности функционирования предлагаемого микропрограммного устройства управления по сравнению с известными заключается в сле дующем. При считывании первой микрокоманды микропрограммы (фиг. 3 ,4б) в соответствии с содержимым счетчика 25 дешифратор 2б формирует управляющий сигнал на первом выходе. При этом информация с проверяемого участка первой микрокоманды (фиг. б) через коммутатор 27 поступает на регистр 28. При считывании второй микрокоманS; (фиг.46 ды содержимое ее поля 7.2 поступает на вторую группу вдодов схемы 29 сравнения. Сигнал с выхода .16 аналогично второму режиму с той разницей, что единичный сигнал поступает на второй вход 3 и дешифратор 35 формирует код очередной микрокоманды по информации, поступающей на первую 32, втррую tO и третью «2 группы входов блока сигналу на входе З. В таблице привёдены входные и выходные наборы Вл6ка 1 формирования адреса в третьем и втором режимах работы. элемента 31 задержки поступает через элемент И 23 на управляющий вход схемы 29 сравнения. Если , что соответствует факту неправильного функционирования устройства, то на выходе 30 устройства появляется с.оответствующий сигнал. Если , что соответствует факту правильного функционирования устройства, то сигнал на выходе 30 устройства отсутствует. При этом содержимое счетчика 25 увеличивается на единицу и формируется адрес очередной контролируемой части микрокоманды $2 (фиг. 4б). Дешифратор 26 по содержимому счет чика 25 формирует соответствующий управляющий сигнал на вход коммутатора 27. При этом код контролируемой части $2 поступает через.жрммутатор 27 на регистр 28. Сигнал с выхода элемента 24 задержки поступает на синхровход регистра 28, и его содержимое суммируются по 17 кодом очередной провер модулю два с емой части S При считывании третьей микрокоманды содержимое ее поля 7.2 сравнивается с содержимым регистра.28 схемой 29 сравнения. Далее устройство функционирует аналогично. При считывании микрокоманд, содержащих в поле 6 коды логических условий (микрокоманды 5, Э, 12, 18, 22 на фиг. 3, а, k5 ), сигналами с поля 8.1 или 8,2. элемент И 23 за крывается и при .их выполнении сигнал на управляющий вход схемы 29 ср нения не поступает. При этом в регистр 28 записывается код контролируемой части (-Й микрокоманды и скл дывается по модулю два с его содерж мым. При считывании след5/ющей ( + 1)-й микрокоманды (если она не содержит кода проверяемых логических условий в схеме 29 сравнения по описанному выше алгоритму осуществляется сравнение содержимого поля 7.2 (1+1)-и 418 микрокоманды S- и содержимого регистр ра 28. Далее.,устройство функцийнирует аналогично. Если содержимое счетчика 25 станет равным числу проверяемых участков в микрокоманде, то очередным импульсом, поступающим на его счетный вход, счетчик устанавливается в единичное состояние. Далее контроль осуществляется так же, как при считывании первой микрокоманды. После выполнения последней микрокоманды на нулевые входы счетчика 25 и регистров и 28 поступает сигнал. При этом их содержимое становится равным нулю. При поступлении очередного кода операции на группу 21«входов устройство выполняет соответствующую микропрограмму по описанному выше алгоритму. Таким образом, введенные блоки и их связи обеспечивают повышение надежности и упрощение устройства;

Q

a

71

ЕЙ90

n

l«i

L...

. Jrl....

pv.t

Авторы

Даты

1983-08-30—Публикация

1982-03-02—Подача