1

Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве управляющих устройств электронных вьлчислительных машин (ЭВМ) с микропрограммным управлением.

Известны устройства микропрограммного управления, содержащие два запоминающих блока, адресный и буферный регистры, дешифраторы, счетчики адресов и микрокоманд, генератор тактовых импульсов, логические элементы И, НЕ и элементы задержки Cll.

Недостатками указанных устройств являются, низкая экономичность запоминающих блоков операционных частей микрокоманд и большое время реализации заданной микропрограм лы.

Наиболее близким к предлагаемому является микропрограммноеустройство управления, содержащее два запоминающих блока, буферный регистр и регистр адреса, счетчик микрокоманд и счетчик адресов микрокоманд, первый и второй дешифраторы, генератор тактовых импульсов, первый и второй блоки элементов И, первый-четвертнй элементы И, первый и второй элементы задержки, элемент НЕ, причем первый выход первого запоминающего блока

соединен с первьлм входом счетчика микрокоманд, выходы которого соединены со входами первого элемента И, выход которого соединен с первыми входами второго и третьего элементов И, а через элемент НЕ с первьи входом четвертого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов и

10 через второй элемент задержки - со вторым входом третьего элемента И, а через первый элемент задержки со вторым входом четвертого элемента И, выход.которого соединен со

15 вторым входом второго блока элементов И, первый вход которого соединен с выходом буферного регистра, первый вход которого соединен с выходом первого блока элементов И, первый

20 зход которого соединен со входом логических условий устройства;второй вход буферного регистра соединен со вторым выходом первого запоминающего блока, третий выход которого соеди25нен со BTOpbff/i входом адресного регистра, первый вход которого соединен с выходом первого .блока элементов И, третий -вход - со входом кода операции устройства, а выход - с

30 tiepBHM входом первого дешифратора. выход которого соединен со входом первого запоминающего блока, четвер тый выход которого соединен с первым входом счетчика адресов микрокоманд, выход которого соединен с первым входом второго дешифратора, второй -вход которого соединен с вы-, ходом четвертого элемента И,а выход - со входом второго запоминающего блока t2j« Одним из недостатков указанного устройства является низкая экономич ность, обусловленная большой избыточностью второго запоминающего бло ка, который используется для хранения операционных частей микрокоман Выход второго запоминающего блок разбит на три поля: операционное по ле, поле логических условий,поле ме ки. В операционном поле -записываютс операционные части выполняемых микрокоманд. В поле логических условий код проверяемых логических условий. В поле метки записывается признак считывания операционной части микро когс.анды. Объем памяти второго запоминающе го блока определяется по формуле 2 oUMc+ y)-n1, (1) где N - общее число записанных опе рационных Частей микрокоманд ; Мд - разрядрость операционного поля; Ну - разрядность поля логически условий. . При выполнении микропрограммы,со держащей р ветвлений, при считывании операгсионных частей лишь в р микрокомандах в поле логических условий записываются коды проверяег-слх логических условий. Для этого необходимо рИх ячеек памяти. Остальные (Nop)Mx ячеек памяти для записи информации не используются. Ука:занный недостаток обуславливает также большую разрядность адресных микрокоманд, хранящихся в первом запоминающем блоке, в частности поля, где записывается число микрокоманд в очередной линейной последовательнос ти. Объем первого запоминакицёго блока оценивается выражением Мд(п,„+П4Й где N(1 - общее число адресньах микрокоманд;а разрядность поля числа микрокоманд; чм п - разрядность первого запоминающего блока. ; Тогда общий объеу запоминающих блоков ..вьиисляётся по формуле W. -«44 ( )No( Следовательно, рассмотренная организация хранения операционных частей выполняемых микрокоманд приводит к неэффективному использованию имеющегося объема памяти запоминающих блоков, а также к высокой их стоимости. Вторым недостатком указанного устройства является большое время выполнения микропрограммы в целом.. Работа схемы тактируется тремя импульсами, сдвинутыми по времени (И1 - импульс с выхода генератора тактовых импульсов; И2 - импульс с выхода второго элемента задержки; ИЗ - импульсс выхода первого элемента задержки) и предназначенными для считывания адреса со счетчика адреса и последующего считывания операционной микрокоманды из второго запоминающего блока (И1), установки в нуль буферного регистра и считывания адреса из адресного регистра (И2), записи адреса первой микрокоманды следующей линейной последовательности, записанной в буферный регистр, в адресный регистр (ИЗ). При реализации заданной последовательности импульсы И2 и ИЗ для считывания операционных частей микрокоманды не используются. Считывание информации со второго запоминающего блока осуществляется импульсом И1.. И1 появляется на выходе генератора тактовых импульсов через время , Сг-i за время задержек элементов задержки. Время выполнения микропрограммы, содержащей N. микрокоманд определяется по формуле к. Т,-.2И- (Т,,,2.-«-ДСН(к+)(, где ДСГ-время между импульсами ИЗ и И1, причем у ja. лт частота генератора иг пульсов;k - число линейных последовательностей в микропрограмме;п. - число микрокоманд в каждой i последовательностиJ . Таким образом, считывание опера 1ионных частей микрокоманд со второго запоминающего блока, но только по импульсам И1, обусловливает большое время вьшолнения микропрограммы, а следовательно низкое быстродействие известного устройства. Кроме того, после выполнения очередной линейной последовательности и обнуления счетчика микрокоманд, импульс И2 должен быть пропущен,так как обнуление буферного регистра должно произойти после передачи информации в адресный регистр, осуществляемый по импульсу ИЗ. Это приводит к необходимости точного согласования времен задержки т и tTo. и времени считывания из второго запоминающего блока и снижает устойчивость функционирования.

Цель изобретения - повышение экономичности устройства микропрограммного управления и сокращение времени выполнения микропрограмм.

Поставленная цель достигается тем что в устройство микропрограммного управления, содержащее первый и второй блоки элементов И, буферный регистр, регистр адреса, первый и второй дешифраторы, первый и второй запоминающие блоки, счетчик микрокоманд, первый, второй, третий и чет.вертый элементы И, первый и второй элементы задержки, счетчик адресов микрокоманд, генератор тактовых им пульсов и первый элемент НЕ,причем |первый вход первого блока элементов И является входом логических условий -устройства, а выход первого блока элементов И соединен с первым входом буферного регистра, выход которого соединен с первым входом второго блока элементов И, выход которого соединен с первым входом регистра адреса, выход которого соединен с информационным входом первого дешифратора, выход которого соединен со входом первого запоминающего блока, первый, второй, третий и четвертый выходы которого соединены соответственно со входом счетчика микрокоманд, со вторым входом буферного регистра, со вторым входом регистра адреса и с первым входом счетчика адресов микрокоманд, второй вход и выход которого соединены соответственно с выходом первого элемента задержки и первым входом второго дешифратора , выход которого соединен со входом второго запоминающего блока, выходы счетчика микрокоманд соединены со входами первого элемента И выход которого соединен с первым входом второго элемента И, второй вход и выход которого соединены соот- . ветственно с выходом первого элёмента задержки и со вторым входом второго блока элементов И, третий вход регистра адреса является входом кода операции устройства, вход первого элемента задержки соединен с выходом второго элемента задержки., вход которого соединен с выходом генератора тактовых импульсов, первый и второй входы третьего элемента задержки соединены соответственно с первым входом второго элемента И и выходом вто рого элемента задержки, вход первого элемента НЕ соединен с первым входом третьего элемента И, а выход - с первым входом четвертого элемента И,второй вход и выход которого соединены

соответственно с выходом генератора тактовых импульсов и вторым входом второго дешифратора, введены триггер управления, регистр команд,второй элемент НЕ, третий, четвертый и пятый блоки элементов И, блок элементов ИЛИ, пятый, шестой и седьмой элементы И и.элемент ИЛИ, причем вход установки в нуль буферного регистра соединен со входом запуска первого дешифратора, входами установки в нуль счетчика адреса и триггера управления и выходом пятого элемента И, первый и второй входы которого соединены соответственно с единичным и нулевым входами триггера управления, единичный вход которого соединен с выходом второго элемента И, второй вход первого блока элемента И соединен с выходом третьего блока элементов И, первый, второй и третий входцл которого соединены соответственно с первым и вторыгл выходами регистра микрокоманд и выходом второго элемента задержки второй вход счетчика микрокоманд соединен с выходом элемента ИЛИ,выход второго запоминающего блока соединен с информационным входом регистра микрокоманд, первый выход которого соединен со входом второго элемента НЕ, выход которого соединен с первым входом четвертого блока элементов И, второй и .третий входы которого соединены соответственно со вторым выходом регистра микрокоманд и входом установки в нуль регистра микрокоманд, выходом первого элемента задержки и первым входом шестого элемента И, второй вход которого соединен с выходом второго элемента НЕ, третий и четвертый выходы регистра микрокоманд соединены соответственно с первыми входами пятого блока элементов И и седьмого элемента И, выхо которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, второй вход и выход пятого блока элементов И соединены соответственно со вторым входом седьмого элемента И и выходом второго элемента задержки и с первым входом блока элементов ИЛИ, второй вход которого соединен с выходом четвертого блока элементов И, выход блока элементов ИЛИ является выходом устройства, выход третьего элемента И соединен со вторым входом пятого элемента И.

Формат микрокоманд, хранящихся во втором запоминающем блоке, разделен на четыре поля. Первое поле предназначено для записи метки при выполнении микрокоманды ветвления; второе для записи логических условий в микрокомандах ветвления (при выполнении микрокоманд, не являющихся микрокомандами .ветвления в нем записывается операционная часть второй , микрокоманды выполняемой пары микрокоманд) ; третье поле - для записи операционной части первой микрокоманды выполняемой пары микрокоманд и четвертое поле - для записи метки при считывании операционной части микрокоманда: с четвертого поля.

В первом поле регистра микрокоманд при считьгаании микрокоманд ветвления записывается единица. Б-л всех остальных случаях в нем записывается нуль.

Во втором поле при выполнении микрокоманд ветвления записывается код проверяемьох логических условий. Во всех остальных случаях в нем записываются операционные части вторых микрокоманд выполняемых пар.

В третьем поле записываются операционные части одиночных микрокоманд при считывании микрокоманд ветвлений и первых микрокоманд выполняемых пар при считывании других микрокоманд последовательности.

(В четвертом поле записывается единица (признак считывания) для все считываемых микрокоманд.

Таким образом, в предлагаемом устройстве для хранения операционных микрокоманд используется не только операционное поле, но и поле логических условий, свободное для всех микрокоманд, кроме микрокоманд ветвления. Это, с одной стороны, позволяет повысить экономичность устройства благодаря использованию естественней избыточности для хранения полезной информации, а с другой повысить быстродействие за счет одновременного считывания пары микрокоманд И передачи их на объект управления с большой частотой.

Введение регистра микрокоманд и соединение его входа с выходом второго запоминающего блока позволяет хранить код считанной микрокоманды и код проверяемых логических условий выполняемых микрокоманд до очередного считывания.

Введение третьего блока элементов И и соединение его первого входа с выходом первого поля регистр.а микрокоманд, второго входа - с выходом второго поля регистра микрокоманд, третьего входа - с выходом второго элемента задержки, а выхода - со вторым входом первого блока элементов И предназначено для передачи ко.да проверяемых логических условий в буферный регистр с целью модификации адреса очередной последовательности микрокоманд значениями проверяемых логических условий.

Четвертый блок элементов И введен для передачи операционной части исполняемой, микрокоманды, записанного во вторам поле регистра микрокоманды, на второй вход блока элементов ИЛИ.

Соединение первого входа четвертого блока элементов И через второй элемент НЕ; с выходом первого регистра микрокоманд предназначено для поддержания элементов И этого блока в открытом состоянии при считывании из второго запоминающего блока операционных частей микрокоманд, не являющихся микрокомандами ветвления.

Соединение второго входа четвертого блока элементов И со вторым выходом регистра микрокоманд служит для подачикода операционной части второй микрокоманды выполняемой пары микрокоманд со второго поля регистра микрокоманд на второй вход четвертого блока элементов ИЛИ.

Соединение третьего входа четвертого блока элементов И с выходом первого элемента задержки предназначено для считывания кода операционной части микрокомандам из второго поля регистра микрокоманд по третьему тактовому импульсу.

Введение блока элементов ИЛИ и соединение его первого входа с выходом пятого блока элементов И, второго входа - сВЫХОДОМ четвертого блока элементов И, а выхода - с выходом устройства, необходимо для передачи операционных частей выполняемых микрокоманд, поступающих со второго и третьего полей регистра микрокоманд на выход устройства.

Введение шестого элемента И и обусловленных им связей служит для формирования признака считывания операционной части из второго поля регистра микрокоманд.

Введение седьмого элемента И и обусловленных им связей предназначено для формирования признака считывания операционной части микрокоманды при считывании информации с четвертого поля регистра микрокоманд.

Введение элемента ИЛИ и соединение его первого входа с выходом седьмого элемента И, второго входа с выходом шестого элемента И, а выхода - со вторым входом счетчика микрокоманд необходимо для передачи признака считывания выполненных микрокоманд по признакам считывания операционных частей выполняемых микрокоманд, фopмиpye ыx шестым и седьмым элементами И.

Введение триггера управления и пятого элемента И, а также обусловленных ими связей предназначено для управления операциями считывания информации из адресного регистра и обнуления буферного регистра и счетчика адресов микрокоманд для записи в них информации. Введение этих элементов позволяет исключить прохождения сигнала на обнуление буферного

регистра до перезаписи информации и него в адресный регистр.

Соединение единичного входа триггера управления с выходом второго элемента И служит для установки его в единичное состояние по сигналам, разрешающим запись адреса микрокоманды из буферного регистра в регис адреса.

Соединение нулевого входа триггера управления с выходом пятого элемента И предназначено для возвращения в исходное состояние триггера управления по сигналам считывания информации из адресного регистра.

Выход первого злемента задержки соединен со вторым входом счетчика адресов микрокоманд и входом установки в нуль регистра микрокоманд для.увеличения содержимого счетчика адресов микрокоманд на единицу по сигналам считывания операционных частей микрокоманд и установки в нуль регистра микрокоманд после счи тывания информации со второго его поля.

Таким образом, введение регистра микрокоманд, третьего-пятого блоков элементов И, пятого - седьмого элементов -И, второго злемента НЕ, блока элементов ИЛИ, элемента ИЛИ, триггера управления и обусловленных ими связей позволяет сократить время выполнения микропрограмм и повысить экономичность устройства за счёт хранения во втором запоминающем блоке парных операционных микрокоманд путем использования поля логических условий и передачи микрокоманд на выход устройства с большей частотой Кроме того, повышение экономичности достигается за счет снижения разрядности адресных микрокоманд, храниr/tux в первом запоминающем блоке.Снижение разрядности обусловлено уменьшением длины поля, в котором записывается «исло микрокоманд в очередной линейной последовательности. Это,в свою очередь, приводит к уменьшений разрядности счетчика Микрокоманд.

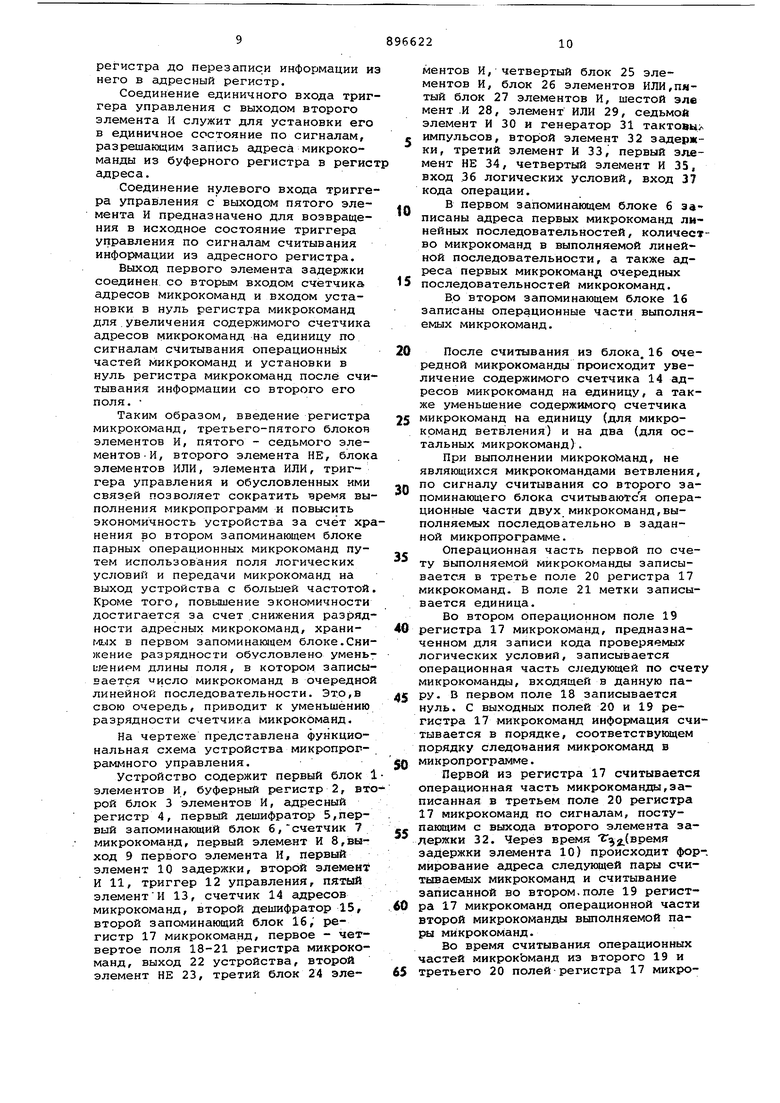

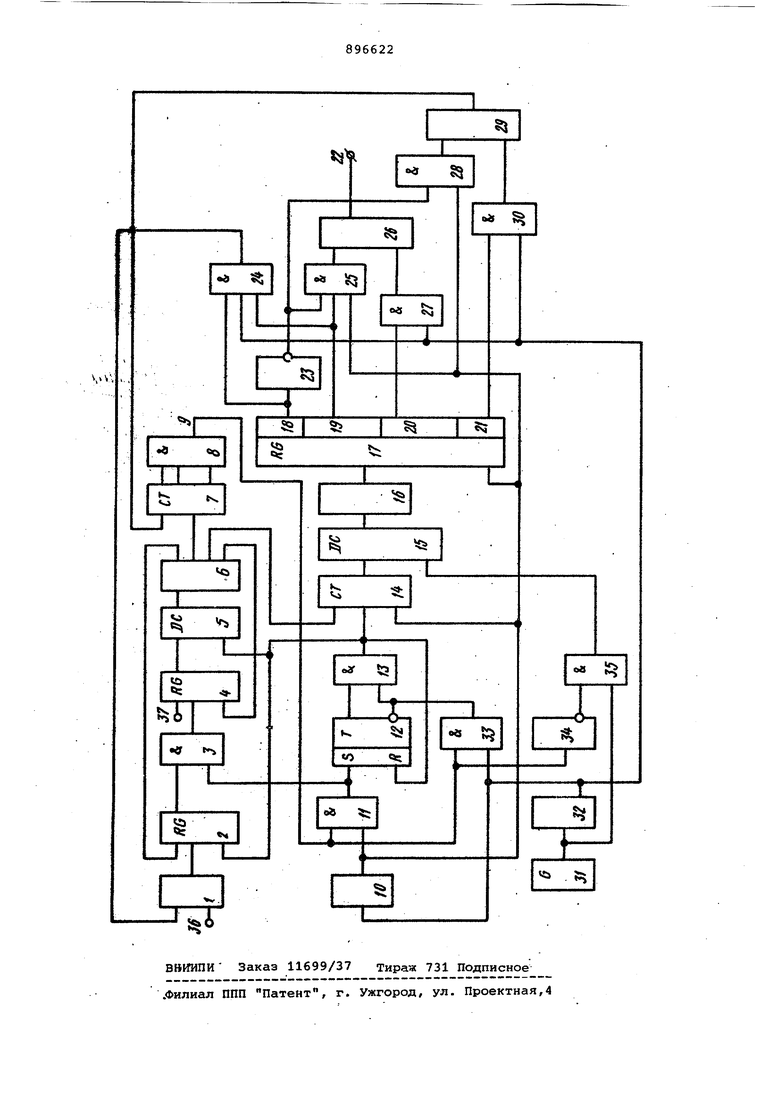

На чертеже представлена функциональная схема устройства микропрограммного управления.

Устройство содержит первый блок 1 элементов И, буферный регистр 2, второй блок 3 элементов И, адресный регистр 4, первый дешифратор 5,первый запоминающий блок б,счетчик 7 микрокоманд, первый элемент И 8,выход 9 первого элемента И, первый элемент 10 задержки, второй элемент И 11, триггер 12 управления, пятый элементИ 13, счетчик 14 адресов микрокоманд, второй дешифратор 15, второй запоминающий блок 16, регистр 17 микрокоманд, первое - четвертое поля 18-21 регистра микрокоманд, выход 22 устройства, второй элемент НЕ 23, третий блок 24 элементов И, четвертый блок 25 элементов И, блок 26 элементов ИЛИ,пятый блок 27 элементов И, шестой эле мент .И 28, элемент ИЛИ 29, седьмой элемент И 30 и генератор 31 такто8ь импульсов, элемент 32 задержки, третий элемент И 33, первый элемент НЕ 34, четвертый элемент И 35, вход 36 логических условий, вход 37 кода операции.

В первом запоминакидем блоке 6 за0писаны адреса первых микрокоманд линейных последовательностей, количество микрокоманд в выполняемой линейной последовательности, а также адреса первых микрокоманд очередных

5 последовательностей микрокоманд.

Во втором запоминающем блоке 16 записаны операционные части выполняемых микрокоманд.

0

После считывания из блока 16 очередной микрокоманды происходит увеличение содержимого счетчика 14 адресов микрокоманд на единицу, а также уменьшение содержимого счетчика микрокоманд на единицу (для микро5команд ветвления) и на два (для остальных микрокоманд).

При выполнении микрокоманд, не являющихся микрокомандами ветвления, по сигналу считывания со второго за0поминающего блока считываются операционные части двух микрокоманд,выполняемых последовательно в заданной микропрограмме.

Операционная часть первой по счету выполняемой микрокоманды записывается в третье поле 20 регистра 17 микрокоманд. В поле 21 метки записывается единица.

Во втором операционном поле 19

0 регистра 17 микрокоманд, предназначенном для записи кода проверяемых логических условий, записывается операционная часть следующей по счету микрокоманды, входящей в данную пару. В первом поле 18 записывается нуль. С выходных полей 20 и 19 регистра 17 микрокоманд информация считывается в порядке, соответствующем порядку следования микрокоманд в микропрограмме.

Первой из регистра 17 считывается операционная часть микрокоманды,записанная в третьем поле 20 регистра 17 микрокоманд по сигналам, поступающим с выхода второго элемента за5держки 32. Через время .(время задержки элемента 10) происходит фор-, мирование адреса следукмцей пары считываемых микрокоманд и считывание записанной во втором.поле 19 регистра 17 микрокоманд операционной части второй микрокоманды выполняемой пары микрокоманд.

Во время считывания операционных частей микрокоманд из второго 19 и третьего 20 полей-регистра 17 микрокоманд формируются сигналы на аыходе элемента ИЛИ 29 и сигналы микроопераций на выходе блока элементов ИЛИ 26, которые поступают на выход 22 устройства.

Если выполняется микрокоманда ветвления, информация в регистре 17 микрокоманд записывается следующим образом.

В четвертом поле 21 записывается единица.

В третьем поле 20 записывается операционная часть микрокоманды.

Во втором поле 19 записывается код проверяемых логических условий.

В первом поле 18 записывается единица - признак записи кода проверяемых логических условий во второе поле 19.

Порядок считывания операционной части, записанной в третьем поле 20 и кода логических условий, записанного во втором поле 19 следующий.

Первой считывается информация с третьего поля 20 регистра 17 микрокоманд, где записана операционная часть микрокоманды ветвления. При этом формируется признак считывания операционной части одной микрокоманды в виде единичного сигнала,который поступает на счетный вход вычитающего счетчика 7 микрокоманд и уменьшает при этом его содержимое на единицу. При этом микрооперации в виде единичных сигналов поступают на выход 22 устройства с выхода блока элементов ИЛИ 26.

Затем считывается код проверяемых логических условий со второго поля 19 регистра 17 микрокоманд,который поступает на первый вход элементов И первого блока 24 и далее на второй вход элементов И первого блока 1, изменяя, в соответствии со значением проверяемых логических условий, адрес первой микрокоманды очередной последовательности микро-команд, хранящийся в буферном регистре 2.

Предлагаемое устройство микропрограммного управления работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии Счетчики микрокоманд 7 и адресов микрокоманд 14 обнулены.

Код операции поступает на третий вход 37 регистра 4 адреса.

Первый тактовый импульс с выхода генератора 31 тактовых импульсов подается на второй элемент 32 задержки и на второй вход четвертого элемента И 35, на первый вход которого поступает нулевой сигнал через первый элемент НЕ 34 с выхода первого элемента И 8. Через время ZTv сигнал с выхода второго элемента 32 задерж ки поступает нэ вход первого элемента 10 задержки и на второй вход

третьего элемента И 33, открытый единичным сигналом с выхода 9 первого элемента И 8. Единичный сигнал с выхода третьего элемента 33 подается на второй -вход пятого элемента И 13, на первый вход которого поступает нулевой сигнал с единичного выхода триггера 12 управления.

Через время ТГ. на второй вход второго элемента И 11 поступает сигнал с выхода первого элемента 10 задержки, которым производится установка в единицу триггера 12 управления.

Следующий тактовый импульс поступает на второй вход третьего элемента И 33, который находится в открытом состоянии.

Единичный сигнал с выхода третьего элемента И 33 поступает на второй вход пятого элемента И 13, который поддерживается в открытом состоянии триггеров 12 управления. В результате формируется сигнал,который производит считывание и дешифрацию записанного в регистр 4 адреса кода операции. Одновременно происходит подтверждение нулевого состояния буферного регистра 2, счетчика адресов 14 микрокоманд и установки в нуль триггера 12 управления.

Через время, равное времени считывания информации с первого запоминающего блока 6, с выхода первого запоминающегр блока 6 считываются и записываются косвенный адрес первой микрокоманды очередной линейной последовательности в буферный регистр 2, адрес первой микрокоманды выполняемой последовательности в счетчик адресов 14 микрокоманд, количество пар микрокоманд в выполняемой последовательности в счетчик 7 микрокоманд.

Сигналом с третьего выхода первого запоминающего блока 6 происходит установка а нуль регистра 4 адреса.

После того, как информация о количестве выполняемых микрокоманд в последовательности записывается в счетчик 7 микрокоманд, сигнал на выходе первого элемента И 8 становится единичным. Этот сигнал поступает на первый вход второго элемента И 11 и блокирует его. Этим же сигналом через первый элемент НЕ 34 четвертый элемент И 35 поддерживается в открытом состоянии до тех пор пока не будет выполнена последняя микрокоманда последовательности,т.е не произойдет обнуление счетчика 7 микрокоманд.

Тактовый импульс с выхода генератора тактовых импульсов поступает на входы второго элемента 32 задержки и на второй вход четвертого элемента И 35, который находится в открытом состоянии. Единичный сигнал

с его выхода поступает на второй вх дешифратора 15, после чего осуществляется считывание операционных частей первой пары микрокоманд- в регистр 17 по адресу, записанному в счетчике адресов 14 микрокоманд.

В первом поле 18 записывается ну если последовательность содержит более одной микрокоманды.

Во втором поле 19 записывается операционная часть второй по счету микрокоманды первой пары.

В третьем поле 20 - операционная часть микрокоманды, первой по счету в паре микрокоманд.

В четвертом поле 21 записывается единица..

По сигналу с выхода второго элемента 32 задержки происходит фО1 лирование сигнала считывания информа,ции на выходе седьмого элемента И 3 На первый его вход поступает сигнал метки с четвертого поля 21 регистра 17 микрокоманд, на второй вход - сигнал с выхода второго элемента 32 задержки. Одновременно происходит считывание операционной части микрокоманды с третьего поля 20 регистра 17 микрокоманд через элементы И пятого блока 27. На первый вход этого блока элементов И поступают сигналы с выхода третьего , а на второй вход - сигналы с выхода второго элемента 32 задержки. Записанные в операционном поле регистра 17 микрокоманд микрооперации поступают на входы блока элементов ИЛИ 26 и далее на выход 22 устройства.

Признак считывания микроопераций с четвертого поля 21 регистра 17 микрокоманд через седьмой элемент И 30 поступает на первый вход элемента ИЛИ 29 и далее на второй вход счетчика 7 микрокоманд уменьшая его содержимое на единицу.

Затем сигналом с выхода первого элемента 10 задержки происходит формирование адреса очередной пары микрокоманд в счетчике 14 адресов микрокоманд путем увеличения его содержимого на единицу. Одновременно этот сигнал поступаетна третий вход четвертого блока элементов И 25,на второй вход которого поступают сигналы Микроопераций со второго поля 19 регистра 17 микрокоманд, а на первый вход - разрешающий сигнал свыхода первого поля 18 через второй элемент НЕ 23..

Сигналы микроопераций с выхода элементов И четвертого блока 25 поступают на входы блока элементов ИЛИ 26 и- далее на выход 22 устройства.

Признак считывания операционной части микрокоманды с выхода шестого элемента И 28 поступает на второй вход элемента ИЛИ 29 и далее на второй вход счетчика 7 микрокоманд,

уменьшается его содержимое на единицу.

Следующий тактовый импульс с выхода генератора 31 тактовых импульсов поступает на второй вход четвертого элемента И 35, который находится в открытом состоянии и производит дешифрацию адреса пары микрокоманд, который записан в счетчике 14 адреса микрокоманд. Если считываемые микрокоманды не являются микрокомандами ветвления, то работа устройства аналогична описанной выше.

Если количество микрокоманд в выполняемой микропрограмме, исключая Микрокоманду ветвления нечетно, то считывание информации со второго запоминающего блока 16 не отличается от описанного, выше, за исключением микрокоманды, предшествующей микрокоманде ветвления. При считывании ее операционной части во втором поле 19 регистра 17 микрокоманд записываются нули.

Считывание информации с выхода регистра 17 микрокоманд при выполнении микрокоманд ветвления не отличается от считывания обычных микрокоманд линейной последовательности. Разница состоит лишь в тем, что в поле 19 логических условий регистра 17 микрокоманд записывается код проверяемых логических условий. В первое поле 18 записывается единица признак выполнения микрокоманды ветвления. В результате разрешается передача кода логических условий через блок элементов И 24 по сигналу с элемента 32 задержки. Поскольку в микрокоманде ветвления содержится только одна операционная часть, то признак-считывания элементом ИЛИ 29 формируется только по сигналу с выхода элемента И 30.

После считывания операционной части микрокоманды ветвления по сигналу признака считывания микрокомандам,поступающему с выхода элемента ИЛИ 29 на второй вход счетчика микрокоманд 7, происходит его обнуление.

На выходе 9 первого элемента И 8 устанавливается единичный сигнал.

Череэ время по сигналу с выхода первого 10 задержки регистр 17 микрокоманд устанавливается в нулевое состояние, триггер J.2 управления - в единичное состояние, а в адресный регистр 4 записывается содержимое буферного регистра 2.

Очередной импульс с выхода генератора 31 тактовых импульсов через третий элемент И 33,-на первый вход которого поступает единичный сигнал с выхода 9 первого элемента ИЗ, поступает на второй вход пятого элемента И 13, на первый ВХС1Д которого поступает единичный сигнал с единичного выхода триггера 12 управления. В результате происходит обнуление счетчика 14 адресов микрокоманд буферного регистра 2 и установка в нулевое состояние триггера 12 управ ления, а также считывание очередной адресной микрокоманды из первого за поминающего блока 6. В дальнейшем работа предлагаемог микропрограммного устройства управления аналогична описанной выше. Время выполнения микропрограммы для предлагаемого устройства микропрограммного управления определяетс по формуле к я./ Ч %. ,, ) + 2 + (-1)Сс:з +г:зг- -д7:), если количество микрокоманд в Г-й линейной последова тельности нечетно; если количество ми рокоманды в i-и ли нейной последовател ности четно. 1. « 2. видно, что Т 7 Tj и. следователь йТ Т - О при всех значениях Объем памяти второго запоминающего блока в предлагаемом устройст определяется по формуле (2Мд+2) - N°(2M +2) где ( если NQ - нечетно оА °° (NeA+f если М0д - четно. количество микрокоманд в микропрограмме, за исключением микрокоманд ветвления; N - количество микрокоманд вет вления в микропрограмме. Объем памяти первого запоминающего блока Определяется выражением Следовательно, разница в объеме запоминакнцих блоков пЕ ф1лагаемого и известного устройств равна .. () Очевидно, 4TOb., так как N ON о- Выигрыш UW растет при реа лизации микропрограмм с многонаправ ленными ветвлениями,. когда My Таким образом, устройство микроnporpsiMMHoro управления обладает повышенным быстродействием и более экономичными 3апоминаняцйми блоками. Формула I изСбретения Устройство микропрограимного управления, содержащее первый и второ блоки элементов И, буферный регистр, регистр адреса, первый и второй дешифраторы, первый и второй запоминающие блоки, счетчик микрокоманд,первый, второй, третий и четвертый элементы И, первый и второй элементы задержки, счетчик адресов микрокоманд, генератор тактовых импульсов и первый элемент НЕ, причем первый вход первого блока элементов И является входом логических условий устройства, а выход первого блока элементов И соединен с первым входом буферного регистра, выход которого соединен с первым входом второго блока элементов И, выход которого соединен с первым входом регистра адреса,выход которого соединен с информационным входом первого дешифратора, выход которого соединен .со входом первого запоминающего блока, первый, второй, третий и четвертый выходы которого соединены соответственно со входом счетчика микрокоманд, со вторым входом буферного регистра, со вторым входом регистра адреса и с первым входом счетчика адресов микрокоманд, второй вход и выход которого соединены соответственно с выходом первого элемента задержки и первым входом второго дешифратора, выход которого соединен со входом второго запоминакнцего блока, выходы счетчика микрокоманд соединены со входами.первого элемента И, выход которого соединен с первым входом второго элемента И, второй вход и выход которого соединены соответственно с выходом первого элемента задержки и со вторым входом второго блока элементов И, третий вход регистра адреса является входом кода операции устройства, вход первого элемента задержки соединен с выходом второго элемента задержки, вход которого соединен с выходом генератора тактовых импульсов, первый и второй входы третьего элемента задержки соединены соответственно с первыгл входом второго элемента И и выходом второго элемента задержки, вход первого элемента НЕ соединен с первым входом третьего элемента И, а выход с первым входом четвертого элемента И, второй вход и выход которого соединены соответственно с выходом генератора тактовых импульсов и вторым входом второго дешифратора, отличающееся тем, что, с целью повышения быстродействия, в него введены триггер управления, регистр команд, второй элемент НЕ, третий, четвертый и пятый блоки элементов И,блок элементов ИЛИ, пятый, шестой и седьмой элементы И и элемент ИЛИ, причем вход установки в нуль буферного регистра соединен со входом запуска первого дешифратора, входами установки в нуль счетчика адреса и триггера

управления и выходом пятого элемента И, первый и второй входы которого соединены соответственно с единичным и нулевым входами триггера управления, единичный вход которого соединен с выходом второго элемента И, второй вход первого блока элемента И соединен с выходом третьего блока элементов И, первый, второй и третий входы которого соединены соответственно с первым и вторым выходами регистра микрокоманд и выходом второго элемента задержки, второй вход счетчика микрокоманд соединен с выходом элемента ИЛИ, выход второго запоминакяцего блока соединен с ин формационным входом регистра микрокоманд, первый выход которого соединен со входом второго элемента НЕ, выход которого соединен с первым входом четвертого блока элементов И, второй и третий входы которого соединены соответственно со вторым выходом регистра микрокоманд и входом установки в нуль регистра микрокоманд, -выходом первого элемента задержки и первым входом шестого элемента И, второй вход которого соединен с выходом второго элемента НЕ, третий и четвертый выходы регистра микрокоманд соединены соответственно с первыми входами пятого блока элементов И и седьмого элемента И, е выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, второй вход и выход пятого блока элементов И соединены

Q соответственно со вторым входом седьмого элемента И и выходом второго элемента задержки и с первым входом блока элементов ИЛИ, второй вход которого соединен с выходом четвертого блока элементов. И, выход блока элементов ИЛИ является выходом устройства, выход третьего элемента И соединен со входом пятого элемента И.

) Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 419893, кл. G 06 F 9/16, 1974.

2.Авторское свидетельство СССР 5 482744, кл. G 06 F 9/16, 1975

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1980 |

|

SU903877A1 |

| Микропрограммное устройство управления | 1980 |

|

SU943728A1 |

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1161941A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Микропрограммное устройство управления | 1981 |

|

SU999052A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

Авторы

Даты

1982-01-07—Публикация

1980-04-28—Подача