Изобретение относится к вычислительной технике и может быть использовано при проектировании управляю- щих устройств ЭВМ и вычислительных. систем с микропрограммным управлением.

Известны микропрограммные устройства управления, содержащие блок памяти микрокоманд, узел формирования адреса, регистр микрокоманд, регистр адреса, дешифратор С1 и Г23.

Недостатком указанных устройств является избыточность блока памяти микрокоманд.

Этот недостаток обусловлен тем что в формате микрокоманд, хранимых в блоке памяти микрокоманд, присутствует поле кодов проверяемых логических условий, размерность которого определяется числом всех логических условий, которые могут проверяться при функционировании устройства.

Наиболее близким к предлагаемому является микропрограммное устройство управления, содержащее регистр адреса, первый дешифратор, блок памяти, регистр микрокоманд, блок проверки логических условий, формирователь адреса, генератор тактовых -импульсов причем входы кода операции устройства соединены с первыми информационными входами регистра адреса, выходы которого соединены с входами первого дешифратора, выходы которого соединены с информационными входами блока памяти, первый и второй выходы генератора тактовых импульсов соединены соответственно с управляющим входом регистра адреса и управляющим входом блока памяти, выходы которого соединены с входами, регистра микрокоманд, выходы микроопераций, немодифицируемой части адреса, модифицируемой части адреса и некоммутйруемых логических условий регистра микрокоманд, соединены соответственно с выходами микроопераций устройства,с входами немодифицируемой части адреса вторых входов регистра адреса, адресными входами формирователя адреса, с первыми входами блока проверки логических условий, входы значений логических условий устройства соединены с вторыми входами блока проверки логических условий устройства, выходы блока проверки логических условий соединены с управляющими входами фор мирователя адреса С33«

Недостатком, прототипа является большая избыточность блока памяти,

В прототипе разрядность поля логических условий формируемых микрокоманд определяется: общим количеством проверяемых логических условий, хотя при выполнении каждой конкретно микропрограммы проверяются не все, а «вяоляе определенное количество логи(ческих условий, существенно меньшее общего чисЛа логических условий, проверяемых устройством в процессе функционирования. Следовательно, для хранения информации об этих логи.ческих условиях необходима существенно меньшая разрядность поля логических условий в формате микрокоманд, формируемых устройством,

Таким образом, избыточная разрядность полей логических условий обусловливает большой объем .оборудования устройства.

Цель изобретения - сокращение объема оборудования устройства.

Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее регистр адреса, первый дешифратор, блок памяти, регистр дикpoкoмaнд, блок проверки логических условий, сумматор по модулю два, генератор тактовых импульсов, причем выходы кода операций устройства соединены с первой группой инфор-.мационных входов регистра адреса, выходы которого соединены с входами первого дешифратора, выходы первого дешифратора соединены с адресными входами блока памяти, первый и второй выходы генератора тактовых импульсов соединены соответственно с управляющим входом регистра адреса и управляющим входом блока пагляти, выходы которого соединены с входами регистра микрокоманд, выходы микроопераций не.модифицируемой части адреса, модифи. цируемой части адреса и неко1 « тируемых логических условий регистра микрокоманд соединены соответственно с группой выходов микроопераций устройства, с входами немодифицируемой части адреса -информационных входов второй группы регистра адреса, первой группой входов сумматора по модулю два с первой группой входов блока проверки логических условий, входы логических условий устройства соединены с второй группой входов блока проверки логических условий, выходы которого соединены с вторыми входами сумматора по модулю два, дополнительно введены буферный регистр, второй дешифратор, коммутатор и триггер пуска, причем входы кода операций устройства соединены с входами буферного регистра, выходы которого соединены с входами второго дешифратора, выходы второго дешифратора соединены с управляющими входами коммутатора, выходы которого соединены с третьей группой входов блока проверки логических условий, выходы коммутируемых логических условий и выход микроопераций Конец операций регистра микрокоманд соединены соответственно с информационными входами коммутатора и нулевым входом триггера пуска, выxofi которого соединен с управляющим входом генератора, вход запуска устройства соединен с единичным входом триггера, выходы сумматора по модулю два соединены с йходами модифицируемой части адреса второй группы информационных входов регистра адреса.

Введение буферного регистра и обусловленных им связей позволяет хранить код операции в течение выполнения соответствующей ему микропрограммы.

Введение второго дешифратора и обусловленных им связей позволяет управлять работой коммутатора.

Введение коммутатора и обусловленных им связей обусловлено необходимостью коммутации части логических условий в соответствии с содержимым .буферного регистра.

Сущность изобретения состоит в уменьшении объема оборудования путем сокращения поля логических условий.

Разрядность формируемых устройством-прототипом микрокоманд является суммой Ч множества логических условий , которые проверяются при выполнении каждой микрокоманды, а суммирование распространяется на число микропрограмм, реализуемых устройством.

Так как при. выполнении j-й микропрограммы п роверяется только часть логических условий, то для их хранения необходимо поле Ч меньшей разрядности, чем для выполнения- всех микропрограмм. Тогда необходимая разрядность поля логических условий, а следовательно, и формат микрокоманд, уменьшится..

Так как разрядность поля меньше разрядности поля . , то для идентификации кода проверяемого логд1ческого условия необходимо осуществись отображение поля разрядностью на поле разрядностью,.

В качестве оператора отображения выби ается код операции. Это вызвано тем, что код операции определяет наборы кодов и проверяемых логических условий при выполнении соответствующей ему микропрограммы.

С целью уменьшения сложности коммутатора логические условия, которые проверяются в большинстве микрокоманд, относятся к классу некоммутируемых, а остальные логические условия - к классу коммутируемых логических условий. Код некоммутируемых логических условий поступает с поля некоммутируемых логических условий регистра микрокоманд непосредственно на блок проверки логических,условий, а код коммутируемых логических условий с поля коммутируемых логических условий поступает в этот блок через : коммутатор.

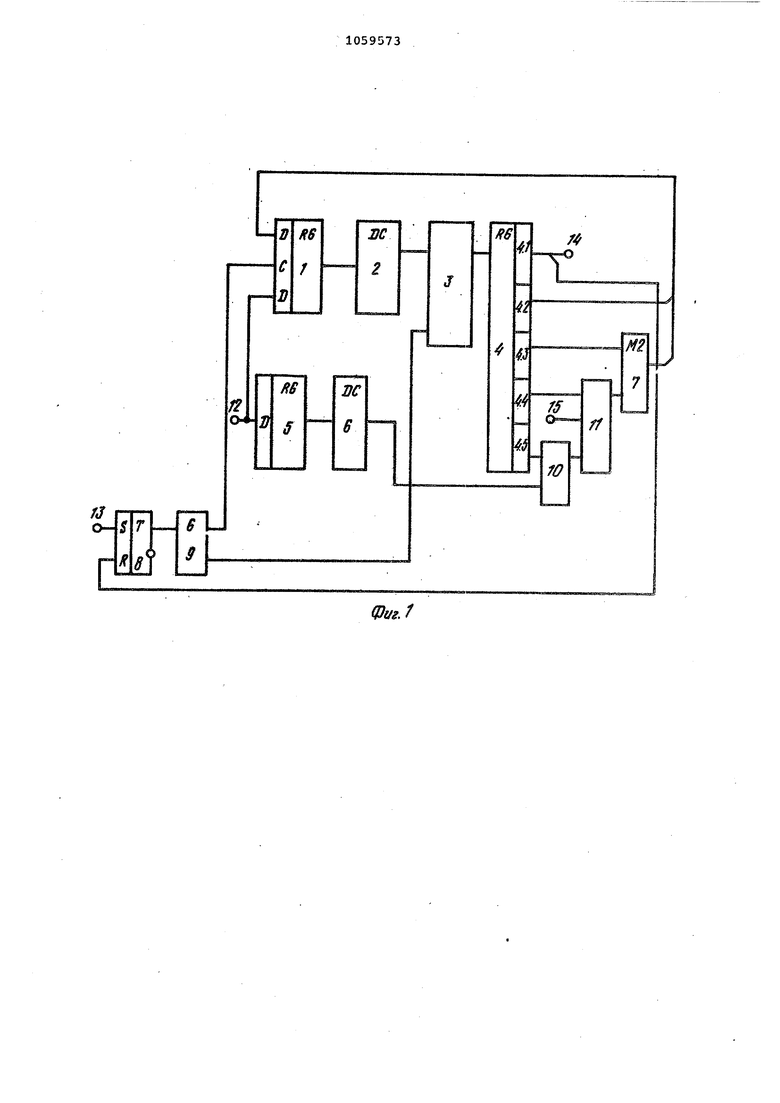

На фиг.1 приведена функциональная схема устройства; на фиг.2 - фрагмент функциональной схемы, на которой -приведены пример реализации коммутатора и блока проверки логических 5 условий на уровне стандартных элементов.

Функциональная схема устройства (фиг.1 состоит из регистра 1 адреса, первого дешифратора 2, блока 3 памя10 ти, регистра 4 микрокоманд с полями: 4.1. - микроопераций, 4.2. немодифицируемой части адреса,4.3. модифицируемой части адреса, 4.4. некоммутируемых логических условий,

5 4.5. - коммутируемых логических условий , буферного регистра 5, второго дешифратора 6, формирователя 7 адреса сумматора по модулю два, триггера 8 пуска, генератора 9, коммутатора

0 10, блока 11 проверки логических условий 11. Кроме того, на фиг.1 позициями 12-15 обозначены входы кода операций, вход пуска, выходы микроопераций, входы значений логических усло25 ВИЙ устройства соответственно. Коммутатор 10 (фиг.2 состоит из первого шестого элементов И 16-21. Позициями 22-25 обозначены входы коммутатора . 10, 26-31 - выходы коммутатора 10,

0 32-34 - выходы некоммутируемых логических условий поля 4.4. регистра 4 микрокоманд. Блок 11 проверки логических условий (фиг.2/ состоит из седьмого - пятнадцатого элементов И

г 35-43 соответственно. Кроме того, позициями 44-52 обозначены шины сигналов логических условий .

Назначение основных узлов устройства состоит в следующем. Регистр 1 0 адреса служит для хранения адреса очередной микрокоманды.

Первый дешифратор 2 служит для выбора линейки при обращении к блоку

3памяти, который предназначен для 5 хранения микрокоманд. Считывание информации из него синхронизированно тактовыми импульсами, поступающими с первого выхода генератора 9. Регистр

4микрокоманд с полями 4.1. - 4.5.

0 предназначен для хранения микрокоманд, считанных из блока 3 памяти.

Буферный регистр 5 служит для идентификации выполняемых микропрограмм (хранения кода операции, соот5 ветствующего выполняемой микропрограмме ). Второй дешифратор 6 предназначен для управления коммутатором 10. Сумматор 7 по модулю два выполняет функцию модификации адресной части

0 очередной микрокоманды. Триггер 8 предназначен, для управления пуском и остановом устройства. Генератор 9 служит для обеспечения синхронизации записи информации в регистр 1 и счи5 тывания микрокоманд из блока 3 памяти.

Коммутатор 10 предназначен для коммутации логических условий в соответствии с кодом операции, преобразуемым дешифратором 6. Блок 11 проверки логических условий.используется для маскирования значений логических условий (выделения значений требуемых логических условий, пришедших на входы 15 в зависимости от значений кода логических условий ).

В исходном состоянии все элементы памяти находятся в нулевом состоянии. После прихода на вход 13 сигнала Пуск триггер 8 разрешает выдачу тактовых импульсов от генератора 9. По первому импульсу код (номер операции через вход 12 поступает на регистр 1 и задаёт начальный адрес соответствующей линейки в блок 3 памяти. Преобразованный в дешифраторе 2 код операции возбулодает шину соответствующей линейки блока 3 памяти. По второму тактовому импульсу, пришедшему с генератора 9, микрокоманда считывается из блока 3 памяти и записывается в регистр 4 микрокоманд. На выходы 14 с поля 4.1 поступает код (микрооперации. Немодифицируемая часть адреса, хранимая в поле 4.2, подается на регистр 1, а модифицируемая часть .адреса с поля 4.3 подается на сумматор 7 по модулю два. С поля 4.4 в блок 11 проверки логических условий поступает код некоммутируемых логических условий. Код коммутируемых логических условий,содержащийся в поле 4.5, поступает на коммутатор 10. Одновременно с записью в регистр 1 код операции асинхронно записывается в буферный регистр 5. Этот код затем возбуждает определенную выходную шину дешифратора 6, связанную с соответствующим управляющим входом коммутатора 10, и последний на время выполнения одной микропрограммы коммутирует разряды кода, хранимого в поле 4,5, на требуемые входы блока 11, задавая таким образом код-маску оставшихся (коммутируемых / логических условий. Значения логических условий, поступающих на вход 15, маскируются в блоке 11 объединенным кодом, состоящим из двух частей, поступающих с поля 4.4 и выхода коммутатора 10. Выделенные Б блоке 11 значения логических условий модифицируют затем переменную часть.адреса, например, путем сгуммирования по модулю два в блоке 7. Модифицированная и немодифицируемая части адреса записываются по очередному тактовому импульсу в регистр 1, а по сдвинутому на время записи информации в регистр 1 импульсу с первого выхода генератора 9 из блока 3 считывается очередная микрокоманда. Дале.е устройство функционирует аналогичрю рассмотренному выше алгоритму. После считывания последней микрокоманды данной микропрограммы : сигналом Конец операции производится обнуление триггера 8, который запрещает выдачу импульсов генератором 9 до прихода очередного кода операций.

Рассмотрим пример конкретного выполнения блоков 10 и 11 на уровне стандартных элементов и алгоритм их работы при выполнении арифметических операций.

В табл,1 приведены данные о логических условиях, которые проверяются в микрокомандах сложения, вычитания, умножения и деления. Всего в этих четырех микропрограммах встречается 9 логических условий . Звездочками отмечены логические условия,проверяемые при выполнении соответствующих операций.

Таблица 1

Сложение

|Вычитание f

Умножение

Гс « -S ч -5

Деление

fi:

Таблицу Логических условий с целью минимизации схемы коммутатора преобразуют по следующей методике.

В таблице логические усло: ия расставляются следующим образом; в первый столбец вписывается логическое условие, которое в процессе выполнения всех микропрограмм проверяется максимальное число раз, во второй столбец записывается логическое условие, которое проверяе1ся в процесс выполнения всех микропрограмм меньше максимального числа раз, но больше всех остальных и т.д.

Отыскивается микропрограмма, в которой проверяется наибольшее число логических условий. В преобразованной согласно п таблице выбираются п первых стол Остальные логические условия носятся в h первых столбцов, при необходимо, чтобы число коммутир столбцов было минимальньм. В соответствии с этим алгорит преобразуют табл.1 в табл.2. .Таблица Сложение Вычитание Умножение Деление Для этого столбцы табл.1 пер ляют в порядке убывания число з дочек в столбцах слева-направо. этом слева сгруппируются стрлбцы ответствующие логическим услови , Xj, X , которые наиболе то встречаются в микропрограммах Звездочки, соответствующие логич условиям х,Хд,и Xj, Хд, перен в третий и второй столбцы соотве венно (эта операция показана на лицах стрелками )/В результате получают табл.3 Т а- б 71 и ц Сложение - Вычитание ;« Умножение (%) (V) j . Деление (. этой таблице пунктирными стрелками показан порядок коммутации разрядов при выполнении операции умножения и деления. Таким образом, вместо 9-разрядного кода логических условий, в предлагаемом устройстве,хранится 5-разрядныйкод. Разряды, соответствующие нeкo 1мyтиpyeмым логическим условиям X X 5 X -,, группируются в поле 4.4. (выходы 32-34 соответственно , а разряды, соответствующие логическим условиям Х2гХ, ХдИ Х,Х,Ха ГРУППИРУЮТСЯ в поле 4.5. (выходы 22 и 23 соответственно ). Выходы 32-34 поля некоммутируемых логических условий подключаются к входам элементом И блока 11 проверки логических условий, на информационные входы которых поступают значения логических условий X X , X с входа 15 через шины 50-52 соответственно. Выходы поля 4,5 коммутируются в зависимости от кода операции.Если выполняются операции сложения или вычитания, то сигналы на выходах 24 и 25 дешифратора 6 равны нулю, а первый и второй разряды кода из поля 4.5 проходят через элементы И 18 и 19 на входы элементов И 40 и 41 соответственно. Вторые входы этих элементов 48 и 47 подключены к входам логических условий Х2 и х . В результате.происходит маскирование этих логических условий на элементах И 40, 41. Если выполняется операция умножения, то на выходе 24 дешифратора 6 (входе коммутатора 10J появляется единичный сигнал, который в течение всей микропрограммы умножения разрешает прохолодение информации через элементы И 16, И 21. Поэтому первый разряд кода поля 4,5 через элемент И 16 поступает на элемент И 38, соответствующий логическому условию х,, а второй разряд - через элемент И 21 - на элемент И 43, соответствующий логическому условию хд. Следовательно, при выполнении микропрограммы умножения в поле 4.5 задается код маска логических условий xg,X4. При выполнении операции дедения единичный сигнал присутствует на входе 25 коммутатора 10, открывая элементы И 17, 20, которые разрешают прохождение кода маски логических условий XQ и Xg соответственно. Этот код затем поступает на элементы и 39, 42, на информационные входы которых подаются значения логических условий х и Xg с входа 15. Таким образом, благодаря многоразовому использованию поля 4.5, длина микрокоманды (поля логических условий) сокращается на четыре разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1365082A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержа Щее регистр адреса, первый дешифратор, блок памяти, регистр микрокоманд, блок проверки логических условий, сумматор по модулю два, генератор тактовых импульсов , причем выходы кода операций устройства соединены с первой Группой информационных входов регистра адреса, выходы которого соединены с входами первого дешифратора, выходы первого дешифратора соединены с адресными входами блока памяти, первый и второй выходы генератора тактовых импульсов соединены соответственно с управляющим входом регистра адреса и управляющим входом блока памяти , выходы которого соединены с входами регистра микрокоманд, выходы микроопераций немодифицированной части адреса, модифицируемой части адреса и некоммутируемых логических условий регистра микрокоманд соединены соответственно с группой выходов микроопераций устройства, с входами немодифицируемой части адреса информационных входов второй группы регистра адреса, первой группы входов сумматора по модулю два, группы входов проверки логических условий, входы логических условий соединены с второй группой входов блока проверки логических условий, выходы которого соединены с второй группой входов сумматора по модулю два, отличающееся тем, что, с целью сокращения объема оборудования, в него введены буферный регистр, .второй дешифратор, коммутатор и триггер пуска, причем входы кода опера- sg ций устройства соединены с входами (Л буферного регистра, выходы которого соединены с входс1ми второго дешифратора, выходы второго дешифратора соединены с управляющими входами ком мутатора, выходы которого соединены 5 с третьей группой входов блока проверки логических условий, выходы коммутируемых логических условий и выходы микроопераций Конец операции ел регистра микрокоманды соединены со сд ответственно с информационными вхрдами коммутатора и нулевым входом триггера пуска, выход которого соеди s| нен с управляющим входом генератора, go вход запуска устройства соединен с единичным входом триггера, выхода сумматора по модулю два соединены с входами модифицируемой части адреса второй группы информационных входов-регистра адреса.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-07—Публикация

1982-07-08—Подача