сравнения, первый выход блока поразрядного сравнения соединен с вторым входом второго элемента И и третьим входом третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ и вторым входом первого элемента ИЛИ, выход первого элемента ИЛИ через элемент задержки соединен с вторым входом третьего блока элементов И, выход которого соединен с информационным входом регистра логических условий, одиннадцатый выход блока управления соединен с вторым входом третьего элемента И, выход которого соединен с управляющим входом, дешифратора, выход дешифратора соединен с первым информационным входом второго коммутатора и с управляющим входом первого коммутатора, выход которого соединен с информационным входом регистра признаков, выход регистра признаков соединен с вторым информационным, входом второго коммутатора, выход которого соединен с информационным входом триггера, двенадцатый выход блока управления соединен с управляюш,им входом второго коммутатора, тринадцатый выход блока управления соединен с входом установки в «О регистра признаков, первая группа разрядов группы информационных входов устройства соединена с группой информационных входов первого блока памяти, вторая группа разрядов группы информационных входов устройства соединена с группой информационных входов второго блока памяти, выход изменяемых логических условий которого соединен с третьим входом третьего блока элементов И, второй выход блока поразрядного сравнения соединен с третьим входом четвертого элемента И, выход которого соединен с вторым входом второго элемента И и третьим входом первого элемента ИЛИ, причем блок управления содержит генератор импульсов, триггер управления, регистр адреса, счетчик микрокоманд, блок памяти, триггер обработки, триггер выдачи, элемент задержки и три элемента И, причем вход блока соединен с входами установки в «О и в «1 триггера управления, с входом режима регистра адреса и с D-входом счетчика микрокоманд, группа выходов которого соединена с группой входов первого элемента И, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом логических условий блока памяти, выход косвенного адреса которого соединен с адресным входом регистра адреса, вход логических условий которого соединен с выходом второго элемента И, выход регистра адреса соединен с информационным входом блока памяти, управляющий вход которого соединен с выходом третьего элемента И и через элемент задержки - с первым выходом блока, первый и второй входы третьего элемента И соединены соответственно с выходом генератора импульсов и единичным выходом триггера управления, вход данных которого соединен с выходом микроопераций блока памяти с второго по четвертый и с шестого по одиннадцатый и с тринадцатым выходами блока, с единичными и нулевыми входами триггеров обработки и выдачи, счетный вход счетчика микрокоманд соединен с четвертым выходом блока, единичные выходы триггеров обработки и выдачи соединены соответственно с пятым и двенадцатым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

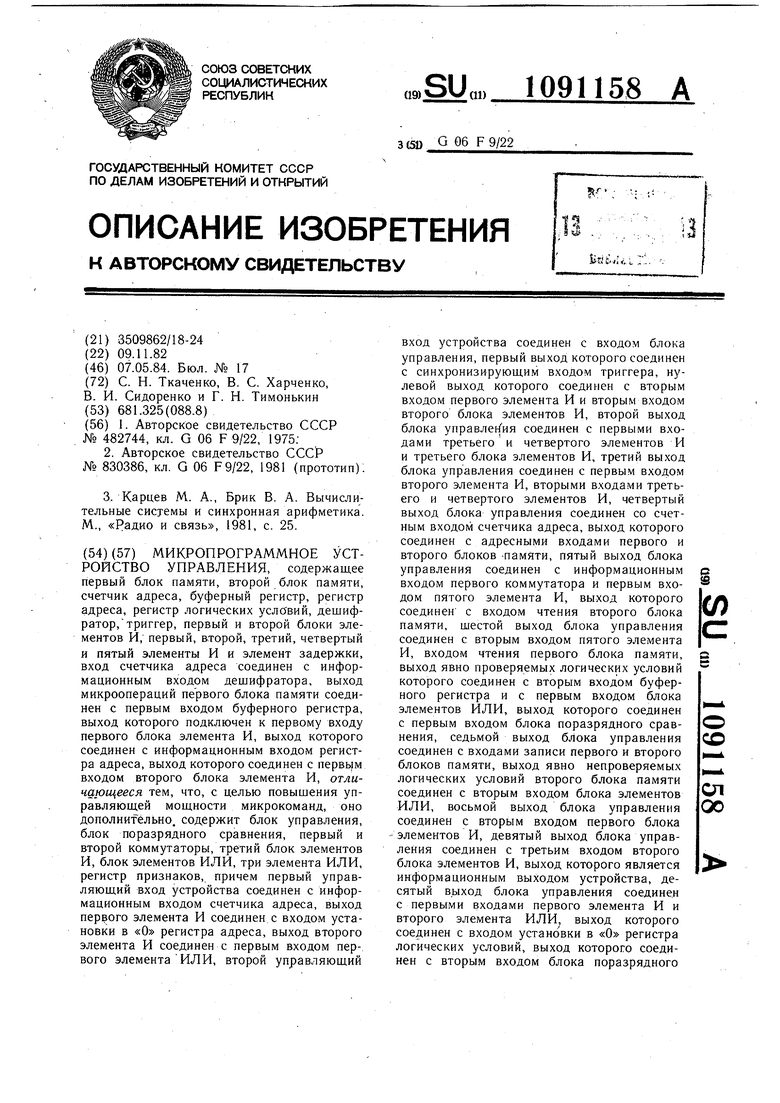

/ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый блок памяти, второй блок памяти, счетчик адреса, буферный регистр, регистр адреса, регистр логических условий, дешифратор,триггер, первый и второй блоки элементов И, первый, второй, третий, четвертый и пятый элементы И и элемент задержки, вход счетчика адреса соединен с информационным входом дешифратора, выход микроопераций первого блока памяти соединен с первым входом буферного регистра, выход которого подключен к первому входу первого блока элемента И, выход которого соединен с информационным входом регистра адреса, выход которого соединен с первцм входом второго блока элемента И, отличающееся тем, что, с целью повышения управляющей мощности микрокоманд, оно дополнительно, содержит блок управления, блок поразрядного сравнения, первый и второй коммутаторы, третий блок элементов И, блок элементов ИЛИ, три элемента ИЛИ, регистр признаков, причем первый управляющий вход устройства соединен с информационным входом счетчика адреса, выход первого элемента И соединен с входом установки в «О регистра адреса, выход второго элемента И соединен с первым входом первого элементаИЛИ, второй управляющий вход устройства соединен с входом блока управления, первый выход которого соединен с синхронизирующим входом триггера, нулевой выход которого соединен с вторым входом первого элемента И и вторым входом второго блока элементов И, второй выход блока управления соединен с первыми входами третьего и четвертого элементов И и третьего блока элементов И, третий выход блока управления соединен с первым входом второго элемента И, вторыми входами третьего и четвертого элементов И, четвертый выход блока управления соединен со счетным входом счетчика адреса, выход которого соединен с адресными входами первого и второго блоков -памяти, пятый выход блока управления соединен с информационным s входом первого коммутатора и первым входом пятого элемента И, выход которого соединен с входом чтения второго блока памяти, шестой выход блока управления соединен с вторым входом пятого элемента И, входом чтения первого блока памяти, выход явно проверяемых логических условий которого соединен с вторым входом буферного регистра и с первым входом блока элементов ИЛИ, выход которого соединен с первым входом блока поразрядного сравсо нения, седьмой выход блока управления соединен с входами записи первого и второго блоков памяти, выход явно непроверяемых логических условий второго блока памяти ел соединен с вторым входом блока элементов оо ИЛИ, восьмой выход блока управления соединен с вторым входом первого блока элементов И, девятый выход блока управления соединен с третьим входом второго блока элементов И, выход которого является информационным выходом устройства, десятый выход блока управления соединен с первыми входами первого элемента И и второго элемента ИЛИ, выход которого соединен с входом установки в «О регистра логических условий, выход которого соединен с вторым входом блока поразрядного

1

Изобретение относится к вычислительной технике и может быть использовано при проектировании микропрограммных устройств и систем (МПУ и МПС).

Известно устройство микропрограммного управления, содержащее блок управления, блок памяти микропрограмм, счетчик адреса, регистр, дешифратор, элементы И и ИЛИ 1.

Недостатки указанного устройства - низкие управляющая мощность- микрокоманд и быстродействие.

Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является устройство, содержащее блок памяти микропрограмм, блок памяти дополнительной информации, счетчик адреса, буферный- регистр, регистр адреса, регистр

2

признаков, регистр логических условий, дешифратор, триггер, первый и второй блоки элементов И, первый, второй, третий, четвертый и пятый элементы И и элемент.задержки, причем выходы счетчика адреса соединены с первой группой входов дешифратора, группа выходов микроопераций блока памяти дополнительной информации соединена с первой группой входов буферного

регистра, выходы которого подключены к первым входам соответствующих элементов И первого блока элементов И, выходы элементов И первого блока элементов И соединены с соответствующими информационными входами регистра адреса с первым входом

первого элемента ИЛИ, выход которого соединен с управляющим входом дешифратора, нулевой выход триггера разрешения выдачи подключен к первому входу элементов И первого блока элементов И, выход которого является информационным выходом устройства 2.

В известном устройстве задача повышения управляюш,ей мощности микрокоманд не решается, чем обусловлены низкие экономичность и управляюш.ая мощность микрокоманд.

Цель изобретения - повышение управляющей мощности микрокоманд.

Указанная цель достигается тем, что в микропрограммное устройство управления, содержащее первый блок памяти, второй бло.к памяти, счетчик адреса, буферный регистр, регистр адреса, регистр логических условий, дешифратор, триггер, первый и второй блоки элементов И, первый, второй, третий, четвертый и пятый элементы И, элемент задержки, причем вход счетчика адреса соединен с информационным входом дешифратора, выход микроопераций первого блока памяти соединен с первым входом буферного регистра, выход которого подключен к первому входу первого блока элементов И, выход которого соединен с информационным входом регистра адреса, выход которого соединен с первым входом второго блока элемента И, дополнительно введены блок управления, блок поразрядного сравнения, первый и второй коммутаторы, третий блок элементов И, блок элементов ИЛИ, три элемента ИЛИ, регистр признаков, причем первый управляющий вход устройства соединен с информационным входом счетчика адреса, выход первого элемента И соединен с входом установки в «О регистра адреса, выход второго элемента И соединен с первым входом первого элемента ИЛИ, второй управляющий вход устройства соединен с входом блока управления, первый выход которого соединен с синхронизирующим входом триггера, нулевой выход которого соединен с вторым входом первого элемента И и вторым входом второго блока элементов И, второй выход блока управления соединен с первыми входами третьего и четвертого элементов И и третьего блока элементов И, третий выход блока управления соединен с первым входом второго элемента И, вторыми входами третьего и четвертого элементов И, четвертый выход блока управления соединен со счетным входом счетчика адреса, выход которого соединен с адресными входами первого и второго блоков памяти,- пятый выход блока управления соединен с информационным входом первого коммутатора и первым входом пятого элемента И, выход которого, соединен с входом чтения второго блока памяти, шестой выход блока управления соединен с вторым входом пятого элемента И, входом чтения первого блока памяти, выход

явно проверяемых логических условий которого соединен с вторым входом буферного регистра и с первым входом блока элементов ИЛИ, выход которого соединен с первым 5 входом блока поразрядного сравнения, седьмой выход блока управления соединен с входами записи первого и второго блоков памяти, выход явно непроверяемых логических условий второго блока памяти соединен с вторым входом блока,элементов ИЛИ, восьмой выход блока .управления соединен с вторым входом первого блока элементов И, девятый выход блока управления соединен с третьим входом второго блока элементов И, выход которого является инфор5 мационным выходом устройства, десятый выход блока управления соединен с первыми входами первого элемента И и второго элемента ИЛИ, выход которого соединен с входом установки в «О регистра логических , условий, выход которого соединен,с вторым

0 входом блока поразрядного сравнения, первый выход блока поразрядного сравнения соединен с вторым входом второго элемента И и третьим входом третьего элемента И, выход которого соединен с первым входом

5 третьего элемента ИЛИ и вторым входом первого элемента ИЛИ, выход первого элемента ИЛИ через элемент задержки соединен с вторым входом третьего блока элементов И, выход которого соединен с информационным входом регистра логических

0 условий, одиннадцатый выход блока управления соединен с вторым входом третьего элемента И, вь1ход которого соединен с управляющим входом дешифратора, выходы дешифратора соединены с первым информационным входом второго коммутатора и

5 с управляющим входом первого коммутатора, выход которого соединен с информационным входом регистра признаков, выход регистра признаков соединен с вторым информационным входом второго коммутатора, выход

которого соединен с информационным входом триггера, двенадцатый выход блока управления соединен с управляющим входом второго коммутатора, тринадцатый выход блока управления соединен с входом установки в «О регистра признаков, первая

5 группа разрядов группы информационных входов устройства соединена с группой информационных входов первого блока памяти, вторая группа разрядов группы информационных входов устройства соединена с группой информационных входов второго блока памяти, выход изменяемых логических условий которого соединен с третьим входом третьего блока элементов И, второй выход блока поразрядного сравнения соединен с третьим входом четвертого элемента И,

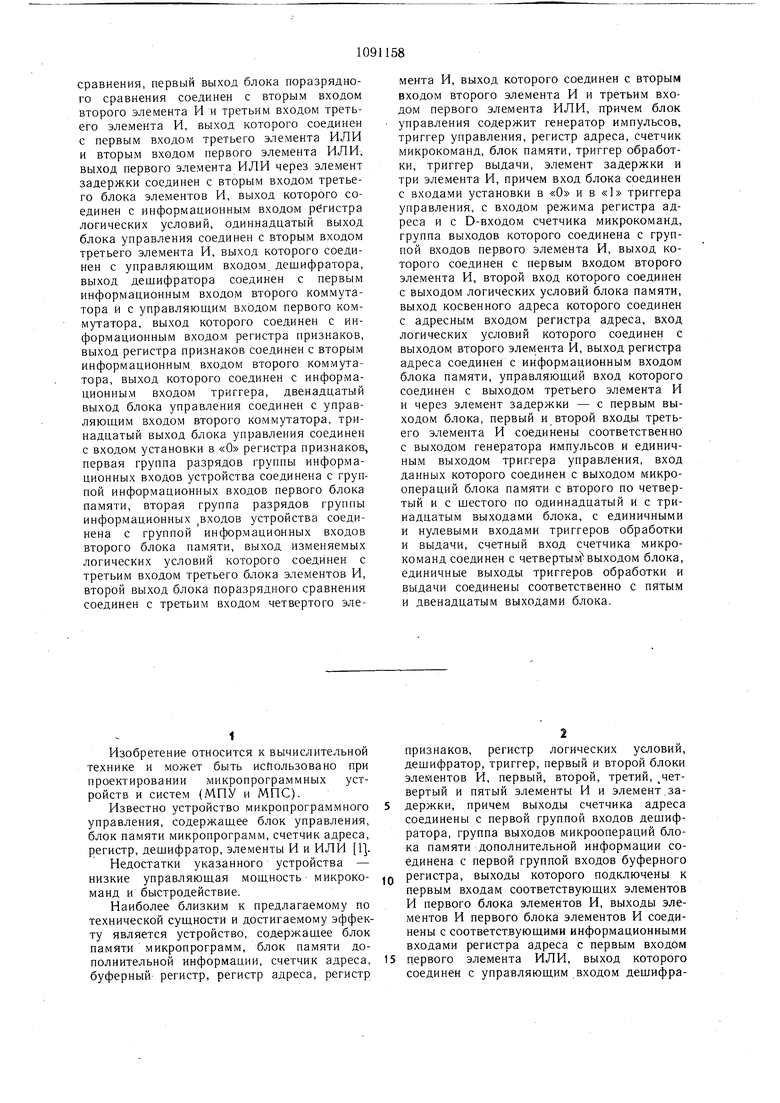

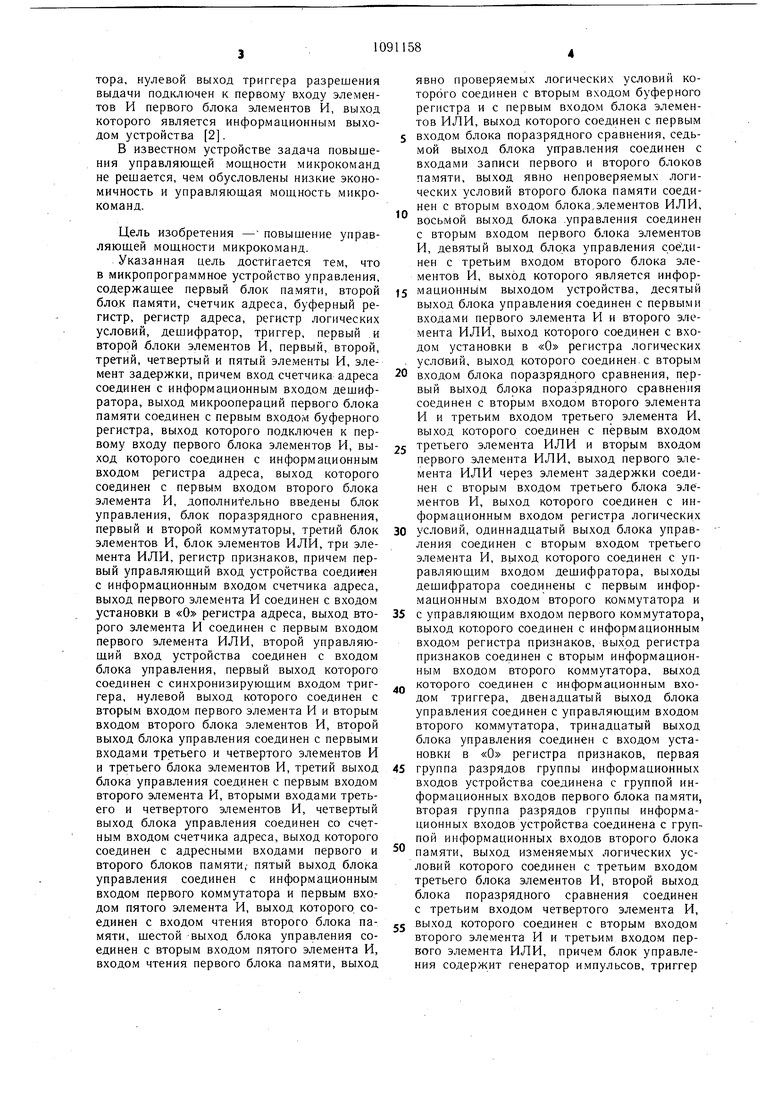

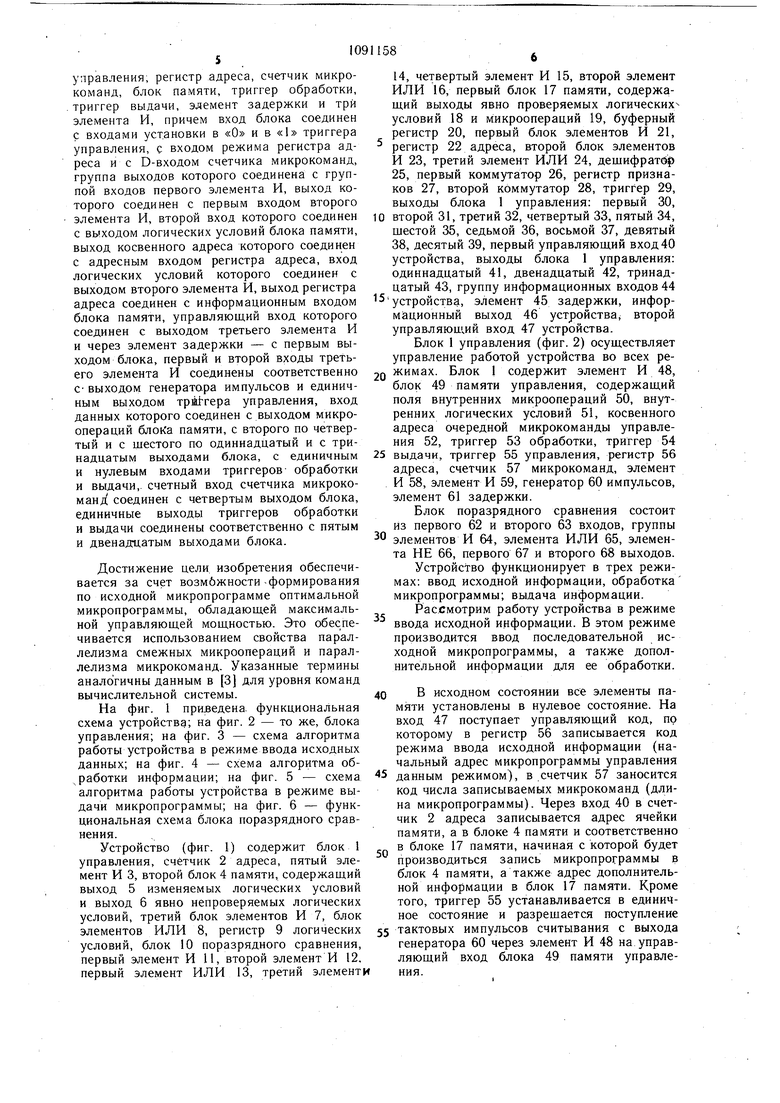

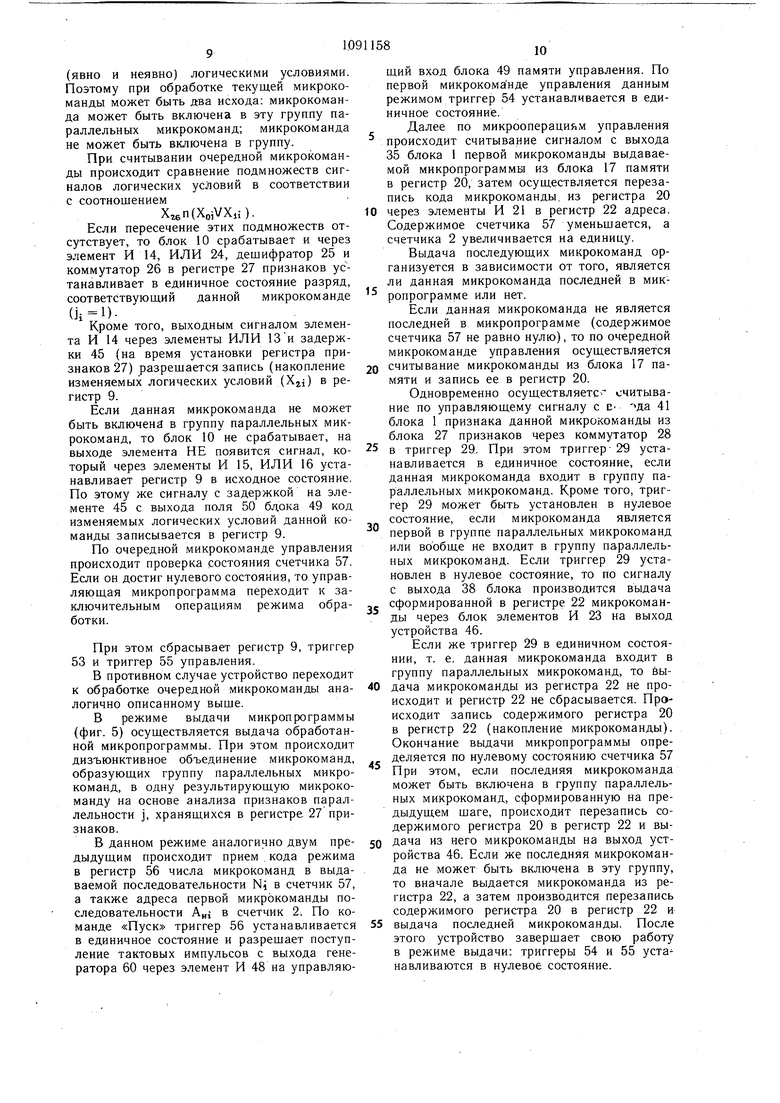

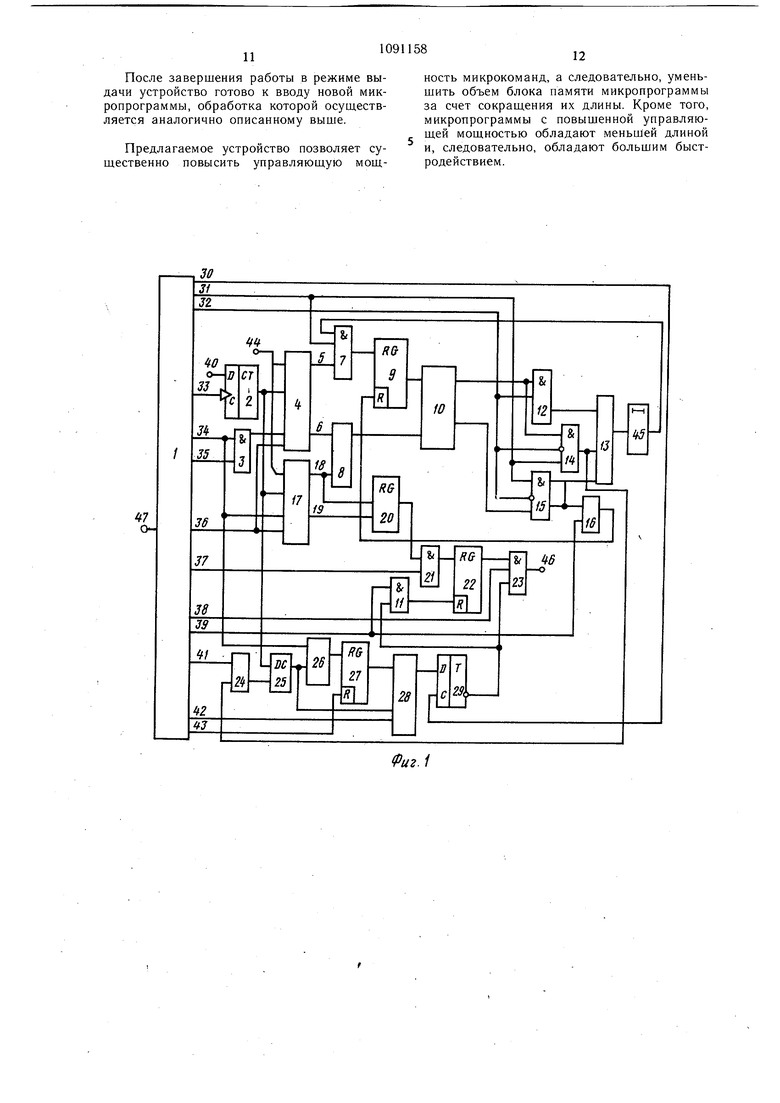

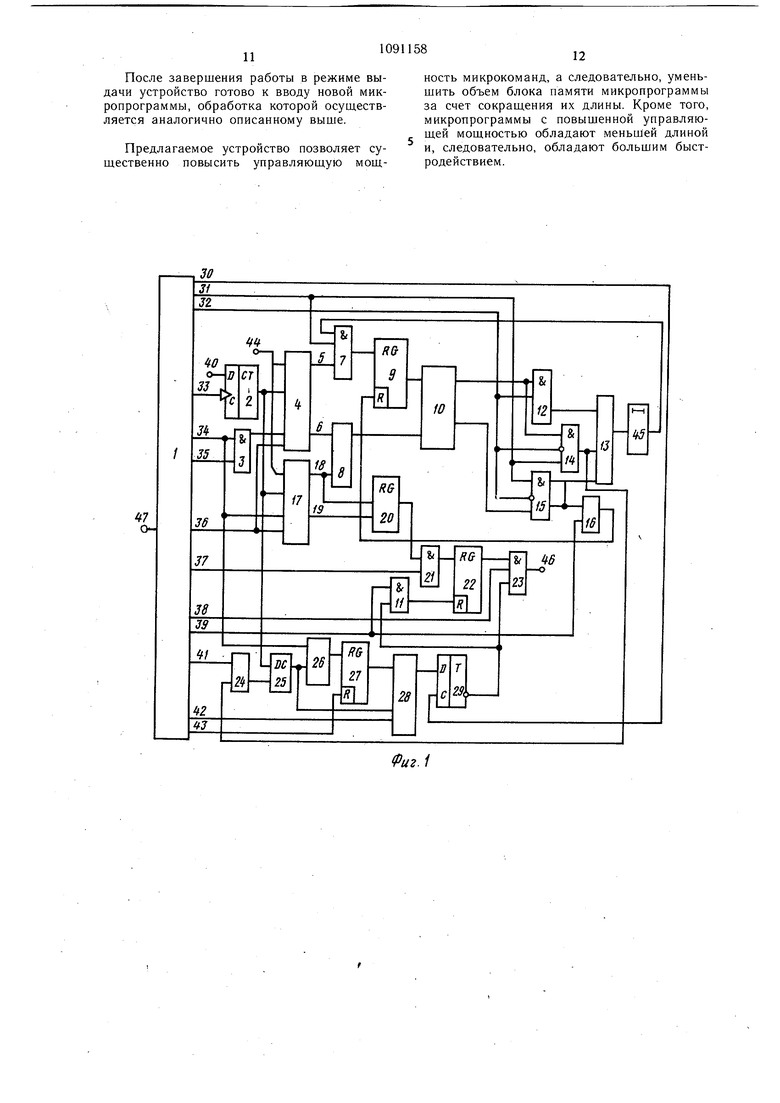

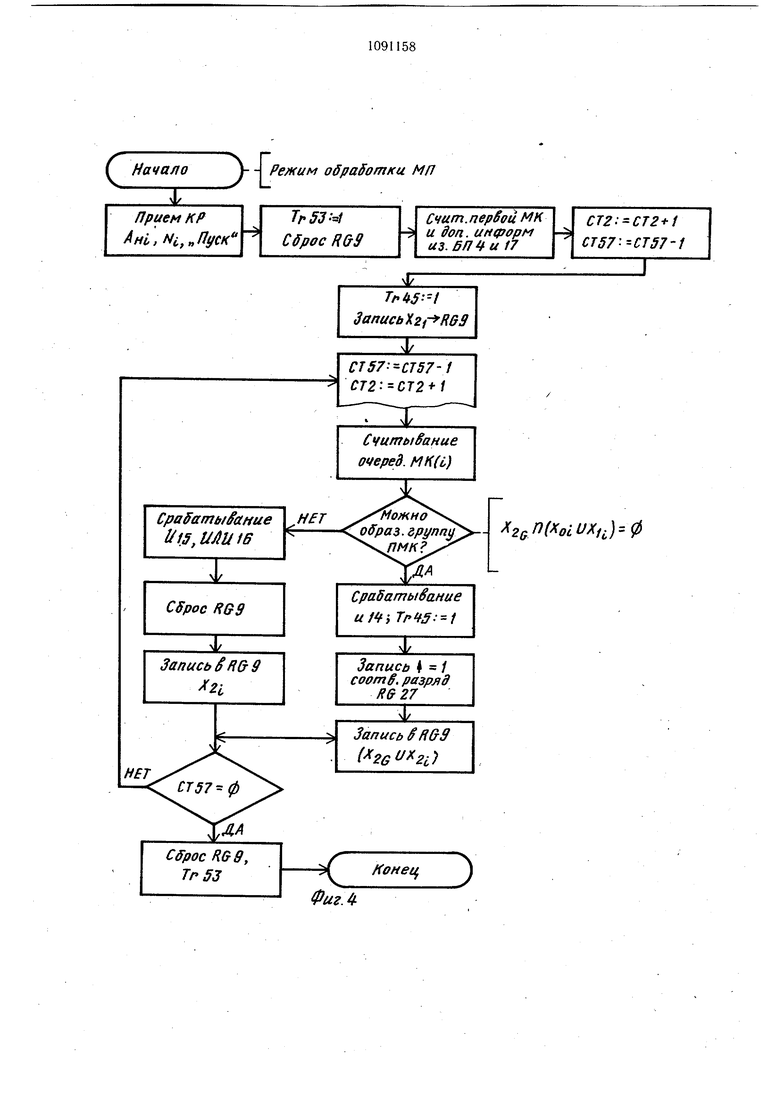

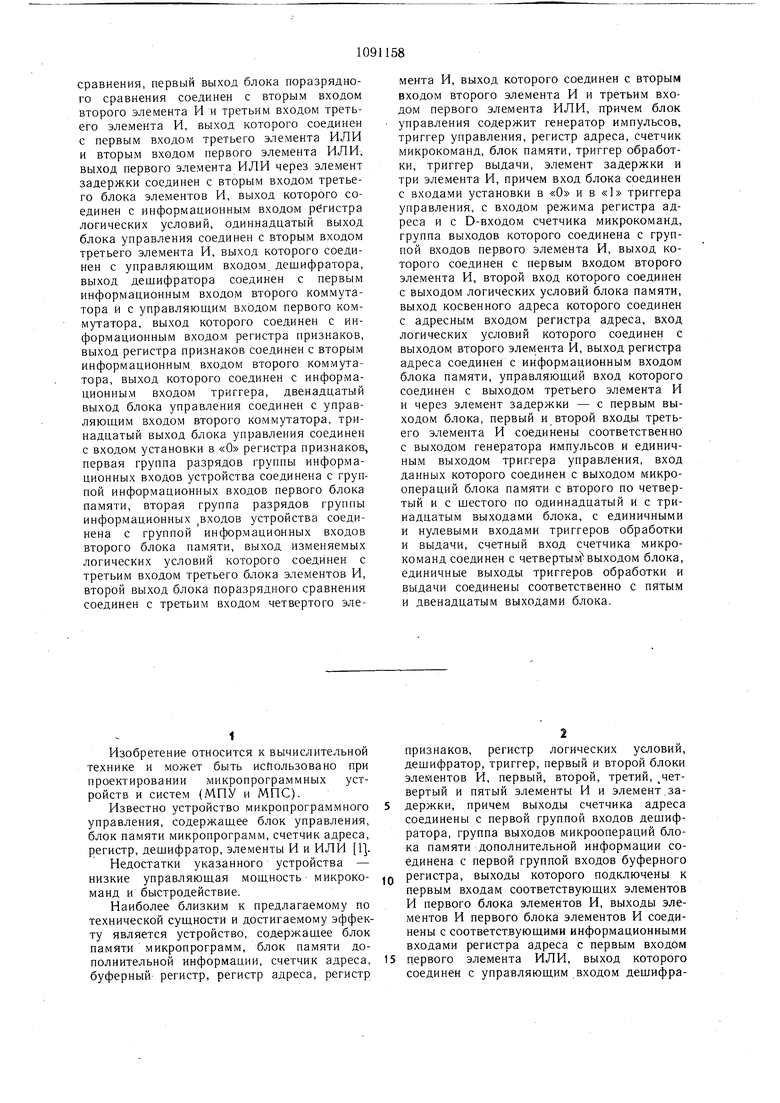

5 выход которого соединен с вторым входом второго элемента И и третьим входом первого элемента ИЛИ, причем блок управления содержит генератор импульсов, триггер управления, регистр адреса, счетчик микрокоманд, блок памяти, триггер обработки, . триггер выдачи, элемент задержки и три элемента И, причем вход блока соединен с входами установки в «О и в «1 триггера управления, с входом режима регистра адреса и с D-входом счетчика микрокоманд, группа выходов которого соединена с группой входов первого элемента И, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом логических условий блока памяти, выход косвенного адреса которого соединен с адресным входом регистра адреса, вход логических условий которого соединен с выходом второго элемента И, выход регистра адреса соединен с информационным входом блока памяти, управляющий вход которого соединен с выходом третьего элемента И и через элемент задержки - с первым выходом блока, первый и второй входы третьего элемента И соединены соответственно с- выходом генератора импульсов и единичным выходом трй1тера управления, вход данных которого соединен с выходом микроопераций блока памяти, с второго по четвертый и с шестого по одиннадцатый и с тринадцатым выходами блока, с единичным и нулевым входами триггеров- обработки и выдачи, счетный вход счетчика микрокоманд соединен с четвертым выходом блока, единичные выходы триггеров обработки и выдачи соединены соответственно с пятым и двенадцатым выходами блока. Достижение цели изобретения обеспечивается за счет возмбжности-формирования по исходной микропрограмме оптимальной микропрограммы, обладающей максимальной управляющей мощностью. Это обеспечивается использованием свойства параллелизма смежных микроопераций и параллелизма микрокоманд. Указанные термины аналогичны данным в 3 для уровня команд вычислительной системы. На фиг. 1 приведена- функциональная схема устройства; на фиг. 2 - то же, блока управления; на фиг. 3 - схема алгоритма работы устройства в режиме ввода исходных данных; на фиг. 4 - схема алгоритма обработки информации; на фиг. 5 - схема алгоритма работы устройства в режиме выдачи микропрограммы; на фиг. 6 - функциональная схема блока поразрядного сравнения. Устройство (фиг. 1) содержит блок 1 управления, счетчик 2 адреса, пятый элемент И 3, второй блок 4 памяти, содержащий выход 5 изменяемых логических условий и выход 6 явно непроверяемых логических условий, третий блок элементов И 7, блок элементов ИЛИ 8, регистр 9 логических условий, блок 10 поразрядного сравнения, первый элемент И 11, второй элемент И 12. первый элемент ИЛИ 13, третий элементи 14, четвертый элемент И 15, второй элемент ИЛИ 16, первый блок 17 памяти, содержащий выходы явно проверяемых логических условий 18 и микроопераций 19, буферный регистр 20, первый блок элементов И 21, регистр 22 адреса, второй блок элементов И 23, третий элемент ИЛИ 24, дешифратор 25, первый коммутатор 26, регистр признаков 27, второй коммутатор 28, триггер 29, выходы блока 1 управления: первый 30, второй 31, третий 32, четвертый 33, пятый 34, шестой 35, седьмой 36, восьмой 37, девятый 38, десятый 39, первый управляюш,ий вход 40 устройства, выходы блока 1 управления: одиннадцатый 41, двенадцатый 42, тринадцатый 43, группу информационных входов 44 устройств а, элемент 45 задержки, информационный выход 46 устройства; второй управляющий вход 47 устройства. Блок 1 управления (фиг. 2) осуществляет управление работой устройства во всех режимах. Блок 1 содержит элемент И 48, блок 49 памяти управления, содержащий поля внутренних микроопераций 50, внутренних логических условий 51, косвенного адреса очередной микрокоманды управления 52, триггер 53 обработки, триггер 54 выдачи, триггер 55 управления, регистр 56 адреса, счетчик 57 микрокоманд, элемент И 58, элемент И 59, генератор 60 импульсов, элемент 61 задержки. Блок поразрядного сравнения состоит из первого 62 и второго 63 входов, группы элементов И 64, элемента ИЛИ 65, элемента НЕ 66, первого 67 и второго 68 выходов. Устройство функционирует в трех режимах: ввод исходной информации, обработка микропрограммы; выдача информации. Рассмотрим работу устройства в режиме ввода исходной информации. В этом режиме производится ввод последовательной исходной микропрограммы, а также дополнительной информации для ее обработки. В исходном состоянии все элементы памяти установлены в нулевое состояние. На вход 47 поступает управляющий код, по которому в регистр 56 записывается код режима ввода исходной информации (начальный адрес микропрограммы управления данным режимом), в счетчик 57 заносится код числа записываемых микрокоманд (длина микропрограммы). Через вход 40 в счетчик 2 адреса записывается адрес ячейки памяти, а в блоке 4 памяти и соответственно в блоке 17 памяти, начиная с которой будет производиться запись микропрограммы в блок 4 памяти, а также адрес дополнительной информации в блок 17 памяти. Кроме того, триггер 55 устанавливается в единичное состояние и разрешается поступление тактовых импульсов считывания с выхода генератора 60 через элемент И 48 на управляющий вход блока 49 памяти управления. По каждому очередному тактовому импульсу осуществляется считывание управляющей микрокоманды с выходов блока 49 памяти. При этом микропрограмма управления режимов ввода исходной информации работает в цикле. В этом цикле по каждому тактовому импульсу выдаются с выхода поля 50 микроопераций управления устройством через выход 37 на входы управления записью блоков 4 и 17 памяти сигналы разрещения записи исходной микропрограммы и соответствующей ей дополнительной информации в блоки 4 и 17 памяти соответственно. Информация в эти блоки поступает через их информационные входы с информационного входа 44 устройства. При этом адрес записи задается по адресным входам блоков 4 и 17 памяти с выхода счетчика 2. Приращение (уменьщение) содержимого счетчика 2 (57) производится по управляющим сигналам, которые поступают с выхода 50 на выход 33 блока 1 управления (вход С счетчика 57).. Кроме того, в каждом такте записи осуществляется проверка достижения счетчиком 57 нулевого состояния, свидетель, ствующего об окончании записи информации. Для этого по сигналу с выхода 51 проверяется на элементе И 59 состояние счетчика 57. Если счетчик достиг нуля то срабатывает элемент И 58 и элемент И 59 выработаег сигнал, по которому микропрограмма управления режимом ввода исходной информации прекращает подачу сигналов записи на блоки 4 и 17 памяти, а также устанавливает все элементы памяти в нулевое состояние. После этого устройство готово перейти к реализации режима обработки информации. По окончании режима ввода информации в блоке 16 памяти записана исходная последовательная микропрограмма, которая состоит из линейных последовательностей. Эти последовательности при реализации микропрограммы могут выбираться в заданном порядке путем определяемым начальным адресом линейной последовательности AHJ и числом микрокоманд в ней N,-. В режиме обработки информации осуществляется обработка линейных последовательностей микропрограммы с целью выявления микрокоманд, которые могут выполняться ггараллельно. Для этого с управ-, ляющего входа 47 устройства в блок 1 управления поступает управляющий код, по которому в регистр 56 адреса (фиг. 2) поступает код режима обработки, в счетчик 57 записывается код числа микрокоманд N{. С входа 40 в счетчик 2 адреса записыБается начальный адрес А„( обрабатываемой линейной последовательности микрокоманд, триггер 55 устанавливается в единичное состояние, разрещая поступление тактовых импульсов с выхода генератора 60 через элемент И 48 на вход разрещения считывания блока 49 памяти микрокоманд управления. По микрокоманде управления триггер. 55 блока 1 устанавливается в единичное состояние, задавая режим обработки. По сигналу с выхода 39 блока 1 регистры 9 и 22- устанавливаются в нулевое состояние. По сигналу с выхода 36 блока 1 осуществляется считывание дополнительной информации (Xji, Xii) из блока 4 памяти и микрокоманды, содержащей код микроопераций, и явно проверяемых логических условий (Xoi), из блока 17 памяти. Коды явно непроверяемых логических условий Xii с выхода 6 блока 4 памяти и явно проверяемых логических условий Xoi с выхода 18 блока 17 памяти через блок элементов ИЛИ 6 поступают на вход блока 10. Па другой вход блока 10 с выхода регистра 9 логических условий поступает нулевой код. Далее обработка первой микрокоманды линейной последовательности отличается от порядка обработки других микрокоманд. Если обрабатывается первая микрокоманда, то поскольку в регистре 9 логических условий записан первоначально нулевой код, а с выхода блока элементов ИЛИ 8 поступает ненулевой К9Д, то появляется сигнал на выходе элемента ИЛИ. Затем с выхода 32 блока 1 управления выдается сигнал - признак обработки первой микрокоманды линейной последовательности. В этом случае срабатывает элемент И 12, выходной сигнал которого через элемент ИЛИ 13 устанавливает в единичное состояние триггер 45. По очередной микрокоманде управления блоком 1 выдается сигнал разрец1ения сравнения с выхода 32, сигнал увеличения на единицу содержимого счетчика 2 адреса с выхода 33 и сигнал уменьщения на единицу значения счетчика 57 микрокоманд. Далее осуществляется считывание очередной, в данном случае - второй микрокоманды обрабатываемой микропрограммы. Обработка второй и последующих микрокоманд производится следующим образом (фиг. 4). По сигналу микрооперации управления с выхода 35 блока 1 управления производится считывание очередной микрокоманды из блока 4 памяти и дополнительной информации из блока 17 памяти. Если микрокоманды, обрабатываемые на предыдущих шагах, образовали, группу параллельных микрокоманд, то в регистре 9 происходит накопление изменяемых логических условий и образование подмножества этой группы. Триггер 45 установлен в единичное состояние ввиду отсутствия пересеченной между изменяемыми и проверяемыми

(явно и неявно) логическими условиями. Поэтому при обработке текущей микрокоманды может быть два исхода: микрокоманда может быть включена в эту группу параллельных микрокоманд; микрокоманда не может быть включена в группу.

При считывании очередной микрокоманды происходит сравнение подмножеств сигналов логических условий в соответствии с соотношением

(XoiVXi;).

Если пересечение этих подмножеств отсутствует, то блок 10 срабатывает и через элемент И 14, ИЛИ 24, дешифратор 25 и коммутатор 26 в регистре 27 признаков устанавливает в единичное состояние разряд, соответствуюш,ий данной микрокоманде

(Ji l)Кроме того, выходным сигналом элемента И 14 через элементы ИЛИ 13 и задержки 45 (на время установки регистра признаков 27) разрешается запись (накопление изменяемых логических условий () в регистр 9.

Если данная микрокоманда не может быть включена в группу параллельных микрокоманд, то блок 10 не срабатывает, на выходе элемента НЕ появится сигнал, который через элементы И 15, ИЛИ 16 устанавливает регистр 9 в исходное состояние. По этому же сигналу с задержкой на элементе 45 с выхода поля 50 бдока 49 код изменяемых логических условий данной команды записывается в регистр 9.

По очередной микрокоманде управления происходит проверка состояния счетчика 57. Если он достиг нулевого состояния, то управляюш,ая микропрограмма переходит к заключительным операциям режима обработки.

При этом сбрасывает регистр 9, триггер 53 и триггер 55 управления.

В противном случае устройство переходит к обработке очередной микрокоманды аналогично описанному выше.

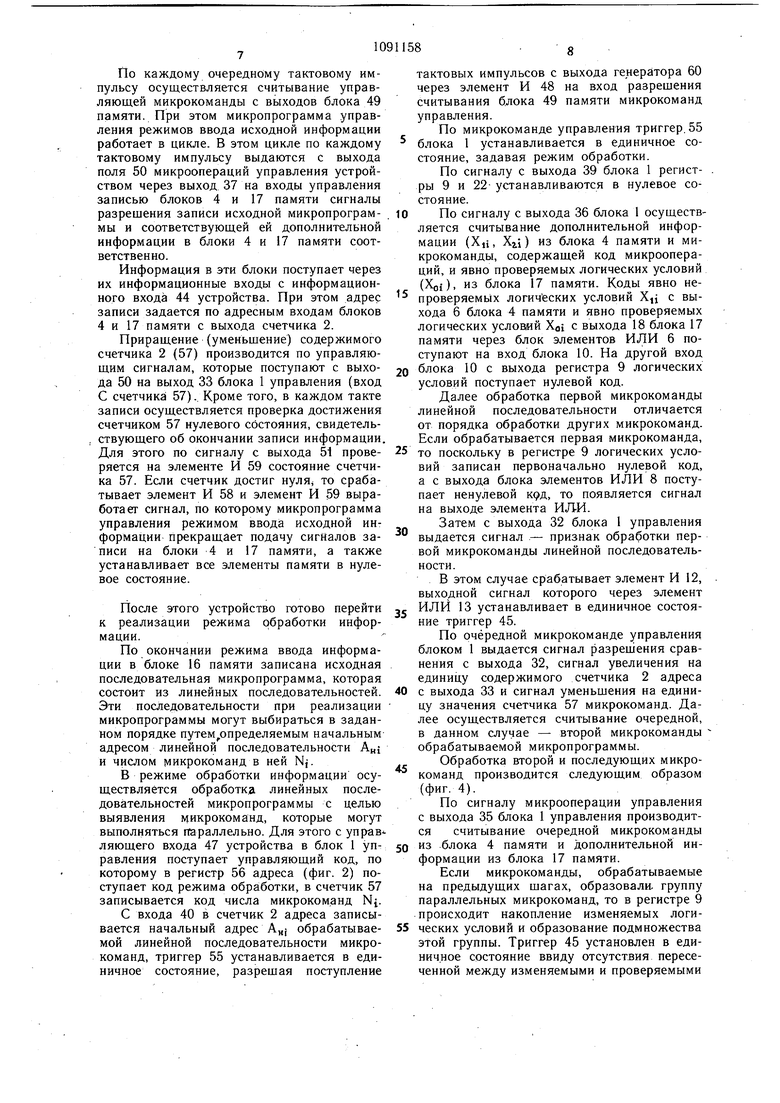

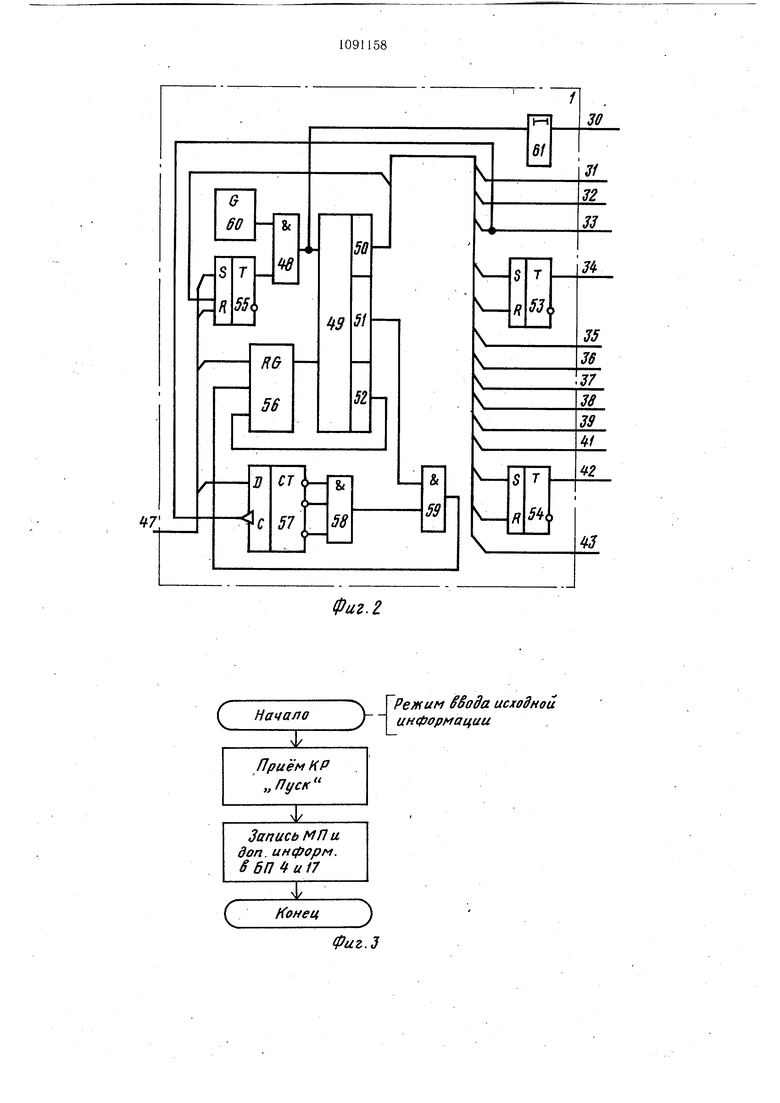

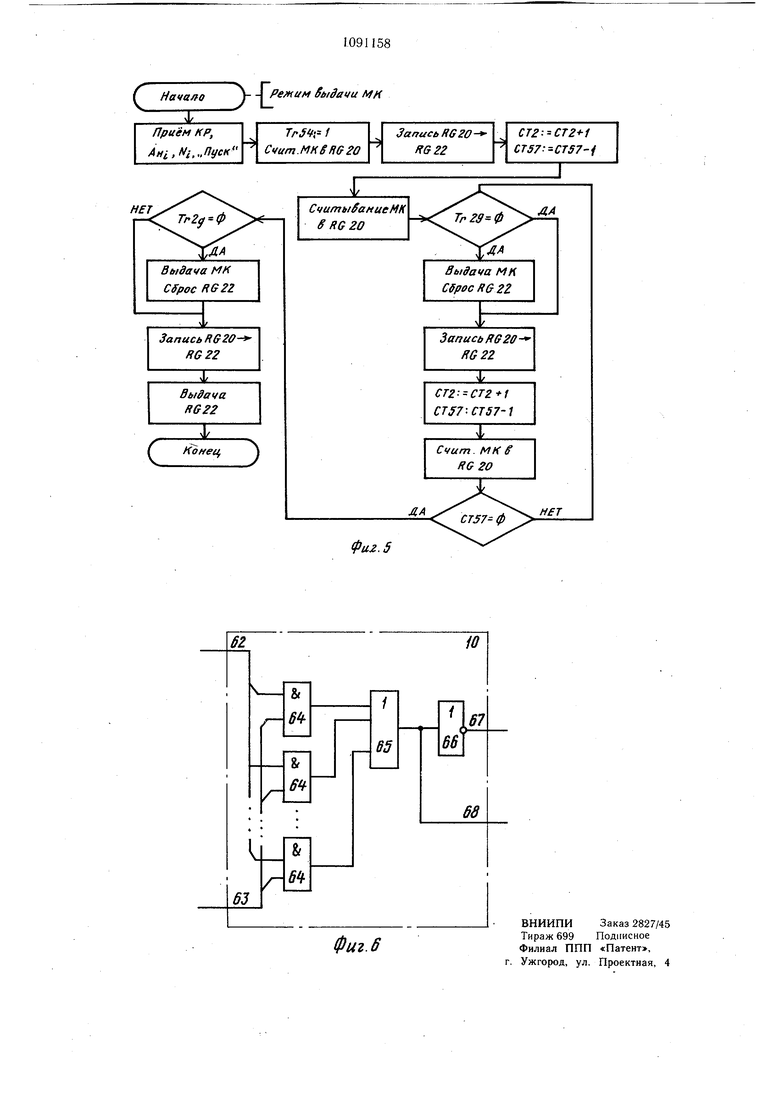

В режиме выдачи микропрограммы (фиг. 5) осуш,ествляется выдача обработанной микропрограммы. При этом происходит дизъюнктивное объединение микрокоманд, образующих группу параллельных микрокоманд, в одну результирующую микрокоманду на основе анализа признаков параллельности J, хранящихся в регистре 27 признаков.

В данном режиме аналогично двум предыдущим происходит прием , кода режима в регистр 56 числа микрокоманд в выдаваемой последовательности Ni в счетчик 57, а также адреса первой микрокоманды последовательности А„{ в счетчик Ч. По команде «Пуск триггер 56 устанавливается в единичное состояние и разрешает поступление тактовых импульсов с выхода генератора 60 через элемент И 48 на управляющий вход блока 49 памяти управления. По первой микрокоманде управления данным режимом триггер 54 устанавливается в единичное состояние.

Далее по микрооперациям управления происходит считывание сигналом с выхода 35 блока 1 первой микрокоманды выдаваемой микропрограммБ из блока 17 памяти в регистр 20, затем осуществляется перезапись кода микрокоманды, из регистра 20

0 через элементы И 21 в регистр 22 адреса. Содержимое счетчика 57 уменьшается, а счетчика 2 увеличивается на единицу.

Выдача последующих микрокоманд организуется в зависимости от того, является ли данная микрокоманда последней в мик ропрограмме или нет.

Если данная микрокоманда не является последней в микропрограмме (содержимое счетчика 57 не равно нулю), то по очередной микрокоманде управления осуществляется

0 считывание микрокоманды из блока 17 памяти и запись ее в регистр 20.

Одновременно осуществляете- считывание по управляющему сигналу с С да 41 блока 1 признака данной микрокоманды из блока 27 признаков через коммутатор 28

5 в триггер 29.. При этом триггер-29 устанавливается в единичное состояние, если данная микрокоманда входит в группу параллельных микрокоманд. Кроме того, триггер 29 может быть установлен в нулевое состояние, если микрокоманда является первой в группе параллельных микрокоманд или вообще не входит в группу параллельных микрокоманд. Если триггер 29 установлен в нулевое состояние, то по сигналу с выхода 38 блока производится выдача сформированной в регистре 22 микрокоманды через блок элементов И 23 на выход устройства 46.

Если же триггер 29 в единичном состоянии, т. е. данная микрокоманда входит в группу параллельных микрокоманд, то выдача микрокоманды из регистра 22 не происходит и регистр 22 не сбрасывается. Происходит запись содержимого регистра 20 в регистр 22 (накопление микрокоманды). Окончание выдачи микропрограммы определяется по нулевому состоянию счетчика 57 При этом, если последняя микрокоманда может быть включена в группу параллельных микрокоманд, сформированную на предыдущем шаге, происходит перезапись содержимого регистра 20 в регистр 22 и вы0 дача из него микрокоманды на выход устройства 46. Если же последняя микрокоманда не может быть включена в эту группу, то вначале выдается микрокоманда из регистра 22, а затем производится перезапись содержимого регистра 20 в регистр 22 и выдача последней микрокоманды. После этого устройство завершает свою работу в режиме выдачи: триггеры 54 и 55 устанавливаются в нулевое состояние.

После завершения работы в режиме выдачи устройство готово к вводу новой микропрограммы, обработка которой осуществляется аналогично описанному выше.

Предлагаемое устройство позволяет существенно повысить управляющую мощность микрокоманд, а следовательно, уменьшить объем блока памяти микропрограммы за счет сокращения их длины. Кроме того, микропрограммы с повышенной управляю щей мощностью обладают меньшей длиной и, следовательно, обладают большим быстродействием.

Фиг. г

С

Начало

Приём HP

„ПyCK

Запись МП и доп информ. SбП иП

г

С

Конец

Фиг.З

Режим исходной

информации

{

С

Режим обраёотки МП

Начало

СТ57-- С757-1 + 1

Считывание oveped. MK(L)

Сраёаты ание 1/15.Ши1В

Сброс FtQ9

Запись §R& 9 21

Запись 4 / CoomS. разряд Ке27

Запись fffl&9 ()

Cfpoc R&9,

sT Нонец J Т г 53

ФигЛ

/ Начало V StiSanu МН

Приём кр,

TrStf t Счит.МКбП(г20 AHi,Ni.,.nycK

СТ2-

Запись RGZOCTS7: CT57-iKG22

Выдача МК Cfpoc KG 22

Запись KG20RG22

Выдача aG22

( КонецJ

Выдача МК серое Я&22

Запись Я020ffG22

СГ2-- СТ2- 1 СТ57-П57-1

Счит. МК g KG 20

фи..5

| I | |||

| Устройство микропрограммного управления | 1972 |

|

SU482744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| А., Брик В | |||

| А | |||

| Вычислительные системы и синхронная арифметика | |||

| М., «Радио и связь, 1981, с | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

Авторы

Даты

1984-05-07—Публикация

1982-11-09—Подача