второго элемента ИЛИ, выход которого соединен с первыми управляющими входами третьего и четвертого блоков элв ментов И, выход поля второй метки регистра микрокоманд соединен с вторым входом первого элемента ИЛИ и первым входом первого элемента И, выход которого соединен с входом синхронизации регистра адреса возврата, выходы которого соединены с информационными входами четвертого блока элементов И выходы четвертого блока элементов И соединены с второй группой входов блока элементов ИЛИ, первый выход блока контроля соединен с вторым управляющим входом второго блока элементов И и первым управлякщим входом первого блока элементов И, второй выход блока контроля соединен с вторыми управляющими входами третьего и четвертого блоков элементов И, единичным входом триггера сбоя, первыми входами второго и третьего элементов И,третий выход блока контроля соеди нен с вторым входом первого элемента И, четвертый выход блока контроля соединен с вторым входом второго элемента ИЛИ, выход конца микропрограммы группы выходов микроопераций устройства соединен с нулевым вхо дом регистра адреса возврата и первым входом третьего элемента ИЛИ, которого соединен с нулевым входом триггера пуска, прямой выход которого соединен с входом пуска генератора тактовых импульсов, первый выход дешифратора - с вторым входом второго элемента И, второй выход дешифратора

1П

93

с ВТ015ЫМ управляющим входом третьего элемента И, вторым входом третьего элемента ИЛИ и выходом отказа устройства, выход третьего элемента И соединен с нулевым входом счетчика сбоев и нулевым входом триггера сбоя, прямой выход которого соединен с первым входом четвертого элемента И, выход которого соединен с счетным входом счетчика числа сбоев, выход второго элемента И соединен через одновибратор с зходон синхронизации регистра адреса сбоя, выходы которого соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами регистра адреса микрокоманд и информационными входами регистра адреса сбоя, выход схемы сравнения соединен с третьим входом третьего элемента И, вход эле мента задержки - с вторым входом четвертого элемента И и выходом генератора тактовых импульсов, выход элемента задержки соединен с четвертым входом третьего элемента И, вторым управляющим входом первого блока элементов И и третьим управляющим вхо- . дом второго блока элементов И, входы кода операции устройства соединены с асинхронными информационными входами регистра адреса возврата, входы логических условий устройства соединены с вторыми информационными входами второго блока элементов И, выходы третьего блока элементов И соединены с третьей группой входов блока элементов ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1980 |

|

SU934472A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1180888A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

Изобретение относится к автомаТике и вычислительной технике и может быть использовано при проектировании микропрограммных процессоров с высокой оперативностью восстановлечия сбоев.

Известно микропрограммное устройство управления с восстановлением при сбоях, содержащее блок памяти микро-, команд, регистр микрокоманд, регистр адреса, блок контроля, блок элементов И, формирователь адреса f ..

Недостатком этого устройства является большая временная избыточность, обусловленная тем, что независимо от места возникновения сбоя при выполнении заданной микропрограммы восстановление микропрограммы осуществляется только с фиксированной ее точки.

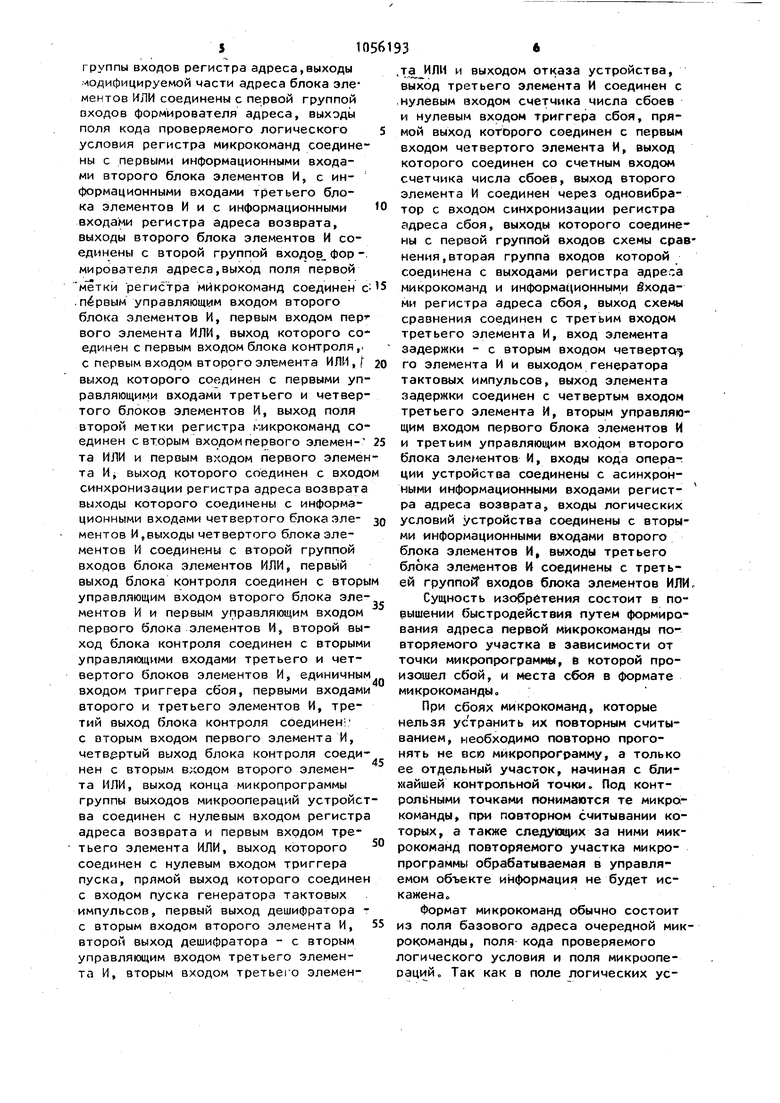

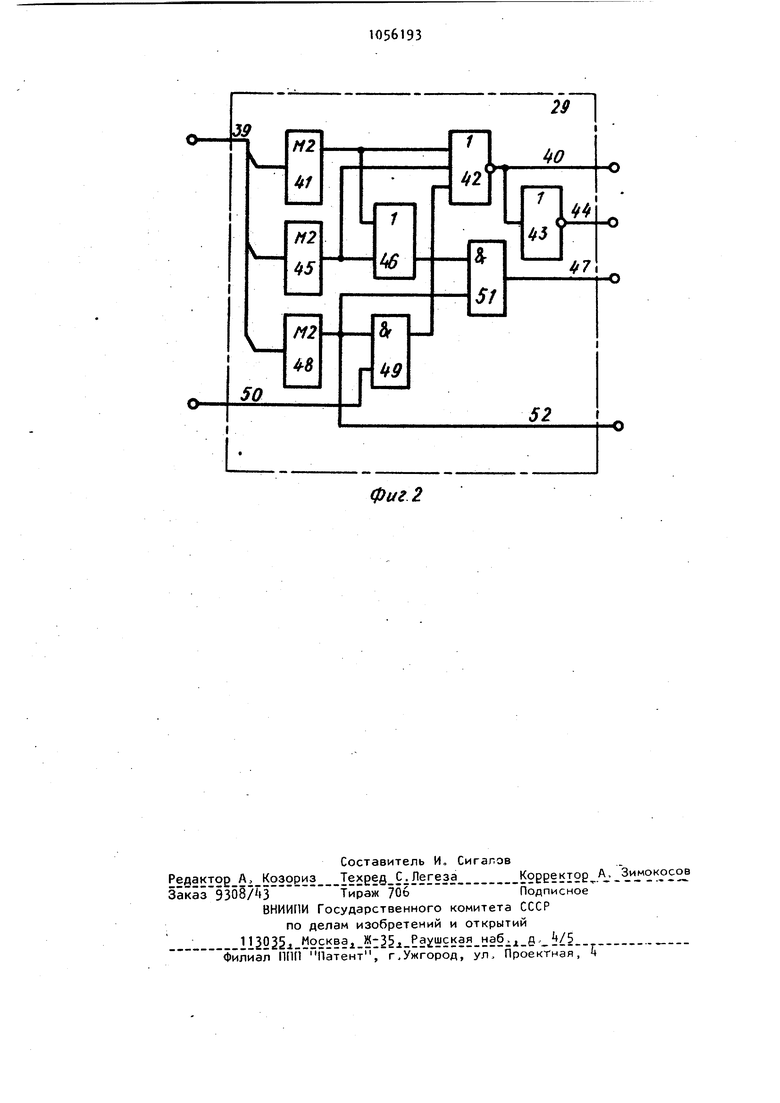

Известно также устройство контроля и восстановления микропрограмм процессора, содержащее регистр адреса, блок памяти микрокоманд, регистр микрокоманд, буферные регистры, элементы И, ИЛИ, счетчик и три ггеры 2. 3- 1 НедостаткагАи изв(;стного устройстоа являются низкая оперативность восстановления и большая сложность устройства, обусловленные наличием специального блока анализа, определяюi ero возможность восстановления микропрограммы путем повтора либо линейной последовательности, либо пбвтора всей микропрограммы Наиболее близким по технической сущности и достигаемому положительному эффекту к изобретению является устройство для управления восстановлением при сбоях, содержащее блок пампти микрокоманд, блок контроля, регистр адреса микрокоманд, регистр мик рокоманд, регистр адреса возврата, счетчик числа сбоев, дешифратор, первый , второй и третий блоки элементов И, генератор тактовых импульсов, триггер пуска, формирователь адреса, причем входы кода операций устройства соединены t первой группой входов регистра адреса микрокоманд, выходы регистра адреса микрокоманд соединены с адресными входами блока памяти микрокоманд, выходы которого соединены с входами регистра микрокоманд, выход полей базового адреса, кода проверяемого логического условия, микроопераций регистра микрокоманд - с группой входов блока контроля, выходы счетчика - с входами дешифратора, выходы формирователя адреса - с входами модифицированной части адреса второй группы входов регистра адреса мик рокоманд, выходы поля микроопераций . регистра микрокоманд соединены с выхо дами микроопераций устройства, выход генератора тактовых импульсов - с вхо дом считывания блока памяти микрокоманд з. Недостатком известного устройства является большое время восстановления сбоев, обусловленное отсутствием анализа места возникновения сбоя при выполнении микропрограммы, В известном устройстве устранение сбоев осуществляется следующим образом. Если повторное считывание искаженной микрокоманды не вызывает искажения обрабатываемой информации, то сбой -ой микрокоманды устраняется путем ее повтора, который производится не более т раз , Если повторное считывание искаженной микрокоманды ис кажает обрабатываемую информацию, то сбой -ой микрокоманды устраняется пу 93 тем повтора осей -ой микропрограммы. Если после m повторных считываний микрокоманды или прогонов микропрО - рдммы сбой не исчезает, то фиксируется отказ устройства, включается диагностическая процедура и локализируется место возникновения отказа устройства , Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для управления восстановлением микропрограмм при сбоях, содержащее блок памяти микрокоманд. блок контроля, регистр адреса кикрокоманд, регистр микрокоманд, регистр адреса возврата, счетчик числа сбоев, дешифратор, первый, второй и третий блоки элементов И, генератор тактовых импульсов, триггер пуска, формирователь адреса, причем входы кода операций устройства соединены с первой группой входов регистра адреса микрокоманд, выходы регистра адреса микрокоманд соединены с адресными входами блока памяти микрокоманд, выходы которого соединены с входами регистра микрокоманд, выходы полей базового адреса, кода проверяемого логического условия, микроопераций регистра микрокоманд соединены с группой входов блока контроля, выходы счетчика числа сбоев соединены с входами дешифратора, выходы формирователя адреса - с входами модифицированной части ггнреса второй группы входов регистра адреса микрокоманд, выходы поля микроопераций регистра микрокоманд - с выходами микроопераций устройства, выход генератора тактовых импульсов соединен с входом считывания блока памяти микрокоманд, вход пуска ycTpovicTBa соединен с единичным входом триггера пуска, дополнительно введены регистр адреса сбоя, схема сравнения, элемент задержки, одновибратор, триггер сбоя, первый, второй, третий и четвертый элементы И, первый, второй и третий элементы ИЛИ, четвертый элементов И, блок элементов ИЛИ, причем выходы поля базового адреса регистра микрокоманд соединены с информационными входами первого блока элементов И , выходы которого соединены с первой группой входов блока элементов .ИЛИ, выходы немодифицируемой части адреса которого соединены с входл -и немодифицируемой ч.зсти адреса второй группы входов регистра адреса,выходы модифицируемой части адреса блока элементов ИЛИ соединены с первой группой входов формирователя адреса, выходы поля кода проверяемого логического условия регистра микрокоманд соединены с первыми информационными входами второго блока элементов И, с информационными входами третьего блока элементов И и с информационными входами регистра адреса возврата, выходы второго блока элементов И соединены с второй группой входов фор -, мирователя адреса,выход поля первой меткй регистра микрокоманд соединен c.первым управляющим входом второго блока элементов И, первым входом nepi вого элемента ИЛИ, выход которого со единен с первым входом блока контроля,, с первым входом второго элемента ИЛИ, I выход которого соединен с первыми управляющими входами третьего и четвертого блоков элементов И, выход поля второй метки регистра микрокоманд соединен с вторым входом первого элемента ИЛИ и первым входом первого элемен та И, выход которого соединен с входо синхронизации регистра адреса возврата выходы которого соединены с информационными входами четвертого блока элементов И,выходы четвертого блока элементов И соединены с второй группой входов блока элементов ИЛИ, первь1Й выход блока контроля соединен с вторы управляющим входом второго блока элементов И и первым управляющим входом первого блока элементов И, второй выход блока контроля соединен с вторыми управляющими входами третьего и четвертого блоков элементов И, единичным входом триггера сбоя, первыми входами второго и третьего элементов И, третий выход блока контроля соединен: с вторым входом первого элемента И, четвертый выход блока контроля соединен с вторым входом второго элемента ИЛИ, выход конца микропрограммы группы выходов микроопераций устройст ва соединен с нулевым входом регистра адреса возврата и первым входом третьего элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска, прямой выход которого соединен с входом пуска генератора тактовых импульсов, первый выход дешифратора с вторым входом второго элемента И, второй выход дешифратора - с вторым управляющим входом третьего элемента И, вторым входом третьего элемента ИЛИ и выходом отказа устройства, выход третьего элемента И соединен с нулевым входом счетчика числа сбоев и нулевым входом триггера сбоя, прямой выход которого соединен с первым входом четвертого элемента И, выход которого соединен со счетным входом счетчика числа сбоев, выход второго элемента И соединен через одновибратор с входом синхронизации регистра адреса сбоя, выходы которого соединены с первой группой входов схемы срав нения,вторая группа входов которой соединена с выходами регистра адреса микрокоманд и информа1|ионными ёходами регистра адреса сбоя, выход схемы сравнения соединен с третьим входом третьего элемента И, вход элемента задержки - с вторым входом четвертое го элемента И и выходом генератора тактовых импульсов, выход элемента задержки соединен с четвертым входом третьего элемента И, вторым управляющим входом первого блока элементов И и третьим управляющим входом второго блока элементов И, входы кода операт ции устройства соединены с асинхронными информационными входами регистра адреса возврата, входы логических условий устройства соединены с вторыми информационными входами второго блока элементов И, выходы третьего блока элементов И соединены с третьей группой входов блока элементов ИЛИ. Сущность изобретения состоит в повышении быстродействия путем формирования адреса первой микрокоманды повторяемого участка в зависимости от точки микропрограм «||, в которой произошел сбой, и места сбоя в формате микрокомандыо При сбоях микрокоманд, которые нельзя устранить их повторным считыванием, необходимо повторно прогонять не всю микропрограмму, а только ее отдельный участок, начиная с блих айшей контрольной точки. Под контроя1 ными точками понимаются те микрокоманды, при повторном считывании которых, а также следующих за ними микрокоманд повторяемого участка микропрограммы обрабатываемая в управляемом объекте информация не будет искажена. Формат микрокоманд обычно состоит из поля базового адреса очередной микрокоманды, поля кода проверяемого огического условия и поля микроопераций „ Так как в поле логических условий полезная информация записана только в микрокомандах ветвления, то это поле в предлагаемом устройстве используется для записи адреса контрольной точки, к которой необходимо возвратиться при неправильном считывании текущей микрокоманды. В данном случае, если адрес контрольной точки равен адресу текущей микрокоманды, происходит ее повторное считывание, Для идентификации информации, записанной в поле логических условий, в формат микрокоманды введено поле первой метки о Единичное значение этого поля соответствует тому,что в поле . логических условий записан код проверяемого логического условия, нулевое значение поля соответствует ситуации , когда в поле логических условий записан адрес контрольной точки. Так как сбой может возникнуть при считывании микрокоманды ветвления-, то для нее также необходимо хранить адрес контрольной точки,, С этой целью в формат микрокоманды введено еще одно поле - поле второй метки„ Единичное значение метки в этом поле свидетельствует о том, что в поле пр веряемого логического условия формат микрокоманды записан код адреса конт рольной точки, к которой необходимо обратиться при считывании со сбоем микрокоманды ветвления Таким образом, в предлагаемом устройстве считываемые из блока памя ти микрокоманд микрокоманды состоят из первого поля кода базового адреса очередной микрокоманды; второго поля кода проверяемого логического условия /адреса контрольной точки, третьего поля первой метки, четвертого поля второй метки и пятого поля микроопераций. Если при считывании микрокоманд возникает сбой, то в следующем такте считывается микрокоманда ее контроль ,ной точки о В очередных тактах считываются следующие за ней микрокоманды повторяюидегося участка микрокомандt i Если при повторном считывании ми рокоманды (при первом считывании котОрой происходит сбой) сбой не позникает, то выполнение микропрограммы продолжается В противном случае про изводится повторное обращение к конт рольной точке Если в течение критического числа повторений сбой не исчезает, то идентифицируется отказ yc ФОЙстваоЕсли при считывании микропрог раммы возникает сбой только во втором поле формата микрокоманды и микрокоманда не является микрокомандой ветвления, то обращения к контрольной точке не производится и продолжается дальнейшее выполнение микропрограммы. Маскирование таких сбоев при формировании микрокоманд, . отказ от воз врата к контрольной точке, позволяет повысить быстродействие устройства. Таким образом, в предлагаемом уст ройстве реализуется плавающая контрольная точка, возврат к которой определяется точкой возникновения сбоя в микропрограмме. Это позволяет при . каждом сбое формировать минимальный . участок повтора 3 На фиг. 1 приведена функциональная схема предлагаемого устройства для управления восстановлением микропрограмм при сбоях; на фиг. 2 - функциональная схема блока контроля. Устройство для управления восстг новлением микропрограмм при сбоях (фиг, 1) содержит формирователь 1 адреса, регистр 2 адреса микрокоманд, входы 3 кода операции, блок памяти микрокоманд, регистр 5 микрокоманд с полями базового адреса очередной микрокоманды 6, кода логических условий 7, первой метки 8, второй метки 9, микроопераций 10, входы 11 сигналов логических условий, первый блок элементов И 12, блок элементов ИЛИ 13, второй блок элементов И 1U, триггер 15 пуска, генератор 16 тактовых импульсов, схему 17 сравнения, регистр 18 адреса возврата, четвертый блок элементов И 19, третий блок элементов И 20, регистр 21 адреса сбоя, первый элемент ИЛИ 22, первый элемент И 23, второй элемент ИЛИ 2, второй элемент И 25, одновибратор 26, четвертый элемент И 27, элемент 28 задержки, блок 29 контроля, выходы 30 микроопераций устройства, выход 31 микроопераций конца микропрограммы, триггер 32 сбоя, третий элемент ИЛИ 33, третий элемент И 3, счетчик 35, де-, шифратор 36, вход 37 сигнала пуска устройства, выход 38 сигнала отказа устройства. БЛОК 29 контроля (фиг. 2) содержит группу входов 39, первый выход О, первый сумматор 1 по модулю два, элемент ИЛИ-НЕ 2, инвертор 43, второй выход kk, второй сумматор 5 по модулю два, элемент ИЛИ kf, четвертый выход 7, третий сумматор 8 по модулю два, первый элемент И 9, первый вход 50, второй элемент И 51 и третий выход 52 Назначение основных элементов уст ройства состоит в следующем Формирователь 1 адреса представля ет собой сумматор по модулю два и служит для формирования модифицируемой части адреса очередной микрокоманды путем сложения по модулю два сигналов, поступающих на первую и вт рую группы его входово Регистр 2 слу жит для хранения кода адреса очередной микрокоманды, 8 блоке k памяти микрокоманд хранятся микрокоманды, формируемые устройством Устройство формирует микрокоманды трех типов К первому типу относятся микрокоманды, в поля 7 кода проверяемого логического условия которых за писан код контрольной точки, к которой необходимо возвратиться при считывании данной микрокоманды со сбоем а в полях первой 8 и второй 9 меток записан нулевой кодо К второму типу относятся микрокоманды, в поле 7 код проверяемого логического условия которых записан адрес контрольной точки, к которой необходимо обратиться при считывании со сбоем данной микро команды либо микрокоманды ветвления, выполняемой после данной микрокоманды, 8 поле 8 первой метки записан нулевой код, а в поле 9 второй метки - единичный код К третьему типу микрокоманд относятся микрокоманды ветвления, в поле 7 этих микрокоманд записан код проверяемого ло гического условия, в поле 8 первой метки - единичный код, в поле 9 второй метки - нулевой кодо Регистр 5 предназначен для хранения кода считанной микрокоманды и вы дачи ее на блок 29 контроля, выходы микроопераций устройства, на блоки элементов И 12 и t. Блок элементов И 12 служит для выдачи при правильном считывании микрокоманды кода базового адреса очередной микрокоман ды через блок элементов ИЛИ 13 на формирователь 1 адреса и регистр 2. Блок элементов И 1 предназначен для npoверки сигналов логических условий, поступакяцих на входы 11 устройства, кодами логических условий с поля 7 регистра 5 и выдачи результатов проверки на формирователь 1 адреса. Регистр 18 гюзволяет хранить адрес кон рольной 1ЧКИ, к которой необходимо возвратиться при считывании со сбоем микрокоманды третьего типа либо команд первого и второго типов, при считывании которых прюисходят сбои одновременно в полях 7 и 6 или 10, Блок элементов И 19 служит для передачи кода адреса контрольной точки с регистра 18, Блок элементов И 20 позволяет передавать адрес контрольной точки считанной со сбоем микрокоманды первого или второго типа с поля 7 регистра 5 на блок элементов ИЛИ 13 Триггер 15 служит для формирования сигнала включения генератора 16 перед выполнением микропрограммы и епо выключения при отказе устройства или окончания выполнения микропрограммы. Вход 37 служит для подачи на вход .. триггера 15 сигнала запуска перед началом выполнения микропрограммы 17 сравнения позволяет формировать сигнал при равенстве кодов в регистрах 2 и 21, И 27 служит для формирования сигналов на счетный вход счетчика 35, который служит для подсчета числа повторных считываний микрокоманды и выдачи кода этого числа на . входы дешифратора 36, позволяющего формировать сигнал на первом выходе при содержимом счетчика 35, равном нулю, и на втором выходе при содержимом , счетчика 35, равном числу повторов,при котором ид энтифицируется отказ устройства. Элемент И 25 позволяет формировать сигнал возбуждения одновибратора 26, который выдает сигнал на вход синхронизации регистра 21. Если текущая мик к команда считана со сбоем, то на выходе элемента И 25 появляется единичный сигнал При этом одновибратор 26 формирует импульс на вход синхронизации регистра 21,; Длительность этого импульса выбирается такой, чтобы обеспечить перезапись в регистр 21 из регистра 2 адреса микрокоманды, при выполнении которой происходит сбой, и исключить запись адреса контрольной точки этот адрес при сбое микрокоманды записывается с поля 7 регистра 5 либо с регистра 18 через блоки элементов И 19, 20 и блок элементов ИЛИ 13 в регистр Регистр 21 служит для хранения адреса микрокоманды, при считывании которой происходит сбой. Генератор 16 служит для формирования импульсов на вход считывания блока k памяти микрокоманд и считывания из него по

адресам, хранящимся в регистре 2, кодов микрокоманд. Элемент 28 задержки предназначен для задержки импульсов с выхода генератора 16 на время считывания микрокоманды из блока памяти микрокоманд, записи ее в регистр 5 и проверки на неискаженность в блоке 29 контроля. Блок 29

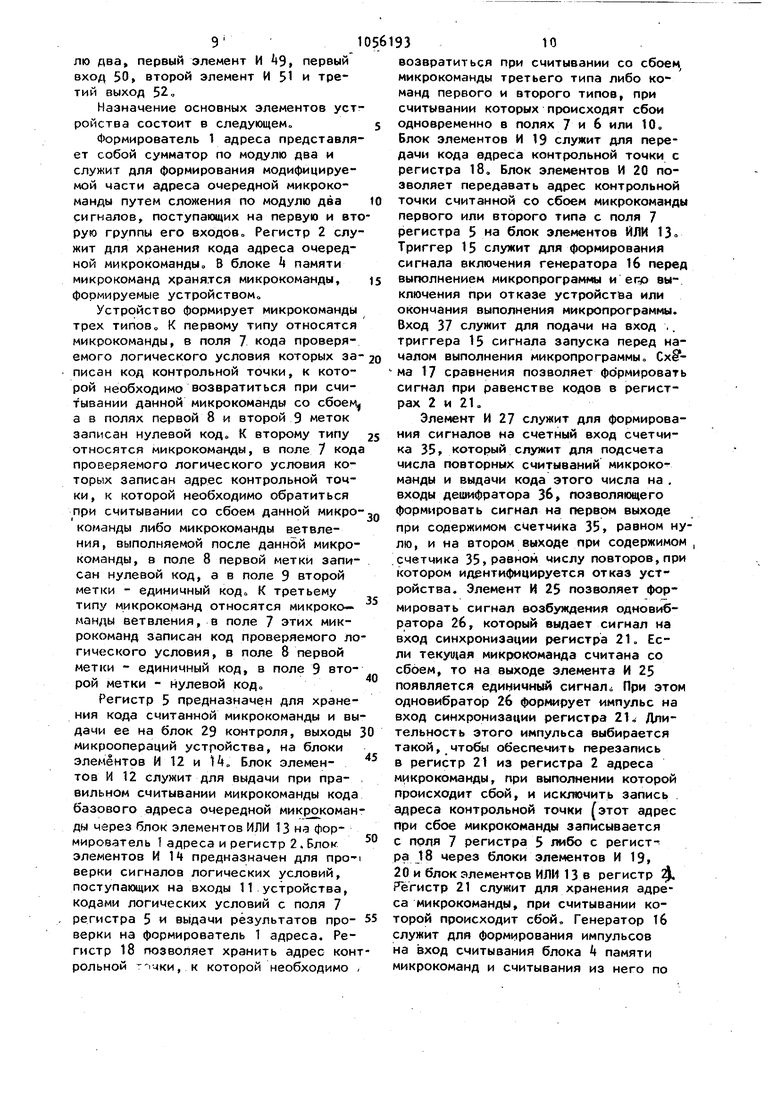

;контроля служит для проверки считываемой микрокоманды. Сумматоры 41, 5 и А8 по модулю два проверяют поступающую на их входы информацию. Если информация записана в регистре 5 без искажений, то на выходе соответствующего сумматора il (5 и 48) по модулю два сигнал отсутствует.

Блок 29 контроля функционирует следующим образом

Контроль микрокоманд первого типа. Если микрокоманда считана из блока памяти в регистр 5 без искажений, то сигналы на выходах сумматоров по модулю два отсутствуют. На вход 50 блока 29 контроля поступают нулевые сигналы. При этом на выходе tO блока контроля появляется единичный сигнал, соответствующий факту правильного считывания микрокоманд. На выходе А сигнал отсутствует (единичное значение сигнала на этом выходе соответствует считыванию микрокоманды со сбоем), Если микрокоманда первого типа считана со сбоем и сбой происходит в полях 6 или 10, то на выходе сумматора k или kS по модулю два появляется единичный сигнал.. При этом единичный сигнал на

выходе 40 блока 29 контроля исчезает;

а на выходе kk появляется. Если сбой происходит в поле / при считывании микрокоманды первого типа, то на выходе сумматора 48 по модулю два появляется единичный сигнал. Так как на вход 50 поступают нулевые сигналы, то на выходе 40 будет оставаться единичный сигнал. Если сбой происходит одновременно в полях 6 и (или) 10 и 7 считанной микрокоманды, то на выходы 44, 47 и 52 блока контроля поступают диничные сигналы,

Контроль микрокоманд второго типа, При считывании в регистр 5 микрокоманд второго типа на вход 50 блока 29 контроля поступает единичный сигнал При возникновении сбоя в микрокоманде впопях6 и 10 или одновременно в полях 6, 7 и 10 блок 29 контроля функционирует аналогично обработке этих сбоев при считывании микрокоманд первого типа. Если сбой возник только в поле 7f то на выходе сумматора 48 по модулю два появляется единичный сигнал. При этом единичный сигнал на выходе 40 блока 29 контроля исчезает, а на выходах 44 и 52 появляется (единичное значение сигнала на выходе 52 запрещает перезапись информации с поля 7 регистра 5 в регистр 18 .

Контроль микрокоманд третьего типа. .

При считывании микрокоманд третьего типа в регистр 5 на входе 50 блока 29 контроля присутствует единичный сигнал. Если сбой возник в полях 6, 7 и 10, то на выходах соответствующих сумматоров 41, 45 и 48 по МО дулю два появляются единичные сигналы. При этом на выходе 40 единичный сигнал исчезает, а на выходах 44, 47 и 52 появляется. При правильном считывании микрокоманды третьего типа значения сигналов на выходах 40, 44, 47 и 52 аналогичны их значениям при правильном считывании микрокоманд первогЬ и второго типов. Элемент ИЛИ 33 слумит для формирования сигнала обнуления триггера 15, триггер 32 служит для идентификации режима работы устройства. При нулевом состоянии триггера 32 устройство находится в режиме выполнения микропрограммы, при единичном состоянии триггера 32 в режиме восстановления сбоя. Элемент И 34 предназначен для формирования сигна11а, соответствующего факту устранения сбоя в считываемой микрокоманде.

Устройство для управления восстановлением микропрограмм при сбоях функционирует следующим образом.

Перед началом функционирования триггеры 15 и 32, регистры 2, 21, 18 и 5 и счетчик 35. устанавливаются в

нулевое состояние (входы их обнуления условно не показаны). На входы 3 устройства поступает код операции и записывается в регистры 2 и 18 Одновременно с этим на вход 37 О ступает сигнал начала выполнения микропрограммы (сигналы на выходы 3 и вход 37 устройства могут поступать, например, от центрального устройства управления. ЭВМ), При этом триггер 15 устанавливается в единичное состояние и включает генератор 16 тактовых импульсов. Тактовые импульсы с выхода генератора 16 поступа-,. .

1310

ют на вход считывания блока памяти микрокоманд С поступлением первого тактового импульса по коду адреса микрокоманды, поступающему с регистра 2 на адресные входы блока памяти микрокоманд, с последнего считывания поступает первая микрокоманда микропрограммы и записывается в регистр 5 микрокоманды Далее код микрокоманды с регистра 5 поступает в блок 29 контроля, а сигналы, микроопераций с поля 10 регистра 5 на выходы 30 микроопераций устройства,, Если микрокоманда является микрокомандой первого типа и считана без сбоев, то на первом выходе Q 29 контроля появляется единичный сигнал

При поступлении импульса с выхода элемента 28 задержки блок элементоа И 12 оказывается открытым по управляющим входам и базовый адрес очередной микрокоманды с поля 6 регистра 5 поступает на блок элементов ИЛИ 13 и с его выходов - на формирователь 1 адреса и регистр 2 адреса При этом модифицируемая часть базового адреса проходит на входы модифицированной части адреса второй группы входов регистра 2 через формирователь 1 адреса, а немодифицируемая часть базового адреса с блока элементов ИЛИ 13 поступает на входы немодифицированной части адреса второй группы входов регистра 2 непосредственно С приходом на вход считывания бло(а 4 памяти микрокоманд очередного импульса с выхода генератора 16 из блока и памяти микрокоманд считывается очередная микрокоманда в соответствии с адресом, записанным в регистре 2,

Если считываемая микрокоманда является микрокомандой второго типа и считана из блока k памяти микрокоманд в регистр 5 правильно, то сигналы микроопераций с поля 10 регистра поступают на выходы 30 устройства, базовый адрес очередной микрокоманды с поля 6 регистра 5 поступает через блок алементов И 12 на блок элементов ИЛИ V3, адрес контрольной точки с поля 7 регистра 5 записывается в регистр 18, открытый по входу синхронизации единичным сигналом с выхода элемента И 2:3 Элемент И 23 при этом открыт ,так как на него поступают единичный сигнал с поля 9 регистра 5 и нулевой сигнал с выхода 52 блока 29 контроля.

93,i,

Далее устройство функционирует аналогично алгоритму при формировании микрокоманд первого типа

Если считываемая микрокоманда является микрокомандой третьего типа и считана без искажений, то сигналы микроопераций с поля 10 регистра 5 поступают на выходы 30 микроопераций устройства, код базового адреса с поля 6 регистра 5 поступает через блок элементов И 12 на блок элементов ИШ 13, код проверяемого логического условия с поля 7 регистра 5 на блок элементов И 1U, где проверяет значения сигналов логических условий, поступающих на входы 11 устройства Сигналы, соответствующие результ1атам проверки логических условий, с выходов блока элементов И k поступают на формирователь 1 адреса, где складываются по модулю два с модифицируемой частью адреса очередной микрокоманды, поступающей на формирователь 1 с блока элементов ИЛИ 13

Далее устройство функционирует аналогично алгоритму функционирования при выполнении микрокоманд первого и второго типов

Если при считывании очередной микрокоманды происходит сбой, то на выходе kk блока 29 контроля появляется единичный сигнал. При этом регистр 21 открывается по входу синхронизации и в него записывается с регистра 2 адрес считанной со сбоем микрокоманды В регистр 2 в зависимости от типа микрокоманды, при считывании которой происходит сбой, записывается адрес контрольной точки либо с поля 7 регистра 5, либо с регистра 18 Если сбой происходит при считывании микрокоманды первого типа, то адрес контрольной точки в регистр 2 записывается с регистра 18 через блок элементов И 19, блок элементов ИЛИ 13 и формирователь 1 адреса Если сбой происходит при считывании микрокоманды второго типа и информация в поле 7 регистра 5 не искажена, то адрес контрольной точки в регистр 2 записывается с. поля 7 регистра 5 через блок элементов И 1 и блок элементов ИЛИ 13 в регистр 2 Если сбой происходит при считывании микрокоманды третьего типа либо при считывании микрокоманды второго типа (информация в поле 7 регистра 5 при считывании этих микрокоманд искажена), то адрес контрольмай точки в регистр 2 записывается С регистра 18 через блок элементов И 19, блок элементов ИЛИ 13 и формирователь 1, . С приходом очередного тактового .импульса Q выхода генератора 16 такт вых импульсов из блока k памяти микрокоманд считывается микрокоманда ; контрольной точки и поступает в реi гистр 5. Одновременно этот импульс через элемент И 27 поступает на счет ный вход счетчика 35 и увеличивает его содержимое на единицу При этом единичный сигнал на первом выходе де 1иифратора 36/исчезает. В процессе Повторного считывания микрокоманд устройство функционирует аналогично алгоритму. При каждом считывании микрокоманд содерк имое счетчика 35 увеличивается на единицу„ Если при повторном считывании искаженной микрокоманды сбой не возникает (на выходе блока 29 контроля сигнал отсутствует) и при этом число повторов меньше критического Гсигнал на втором выходе дeulифpatoра 36 отсутствует , то на выходе эле мента- И 3 появляется единичный сигнал, так как элемент И 3 открыт по всем входам. Этим сигналом триггер 32 и счетчик 35 обнуляются. Далее устройство формирует аналогично алгоритму очередные микрокоманды микропрограммы. 1fl 16 Если же после критического числа повторов сбой микрокоманды не исчезает, то содержимое счетчика 35 становится равным критическому. При этом на втором выходе дешифратора 36 появляется единичный сигнал, соответствующий факту отказа устройства. Этот сигнал поступает на выход 38 устройства и через элемент ИЛИ 33 устанавливает в нулевое состояние триггер 15. При этом генератор 16 тактовых импульсов прекращает выдачу тактовых импульсов и устройство переходит в состояние отказа. После, восстановления отказа устройство функционирует аналогично. При считывании последней микрокоманды микропрограммы на выходе 31 конца микропрограммы появляется единичный сигнал. Этот сигнал обнуляет регистр 18 и через элемент ИЛИ 13 триггер 15. При поступлении очередного кода операции на входы 3 устройства оно функционирует аналогично алгоритму,. . При использовании предлагаемого устройства существенно (на 7Q%) уменьшается время восстановления сбоев путем формирования адреса первой микрокоманды повторяемого участка микропрограммы в зависимости от характера микрокоманды, при выполнении которой происходит сбой, и места сбоя в ее формате а

фиг 2

Авторы

Даты

1983-11-23—Публикация

1982-08-24—Подача