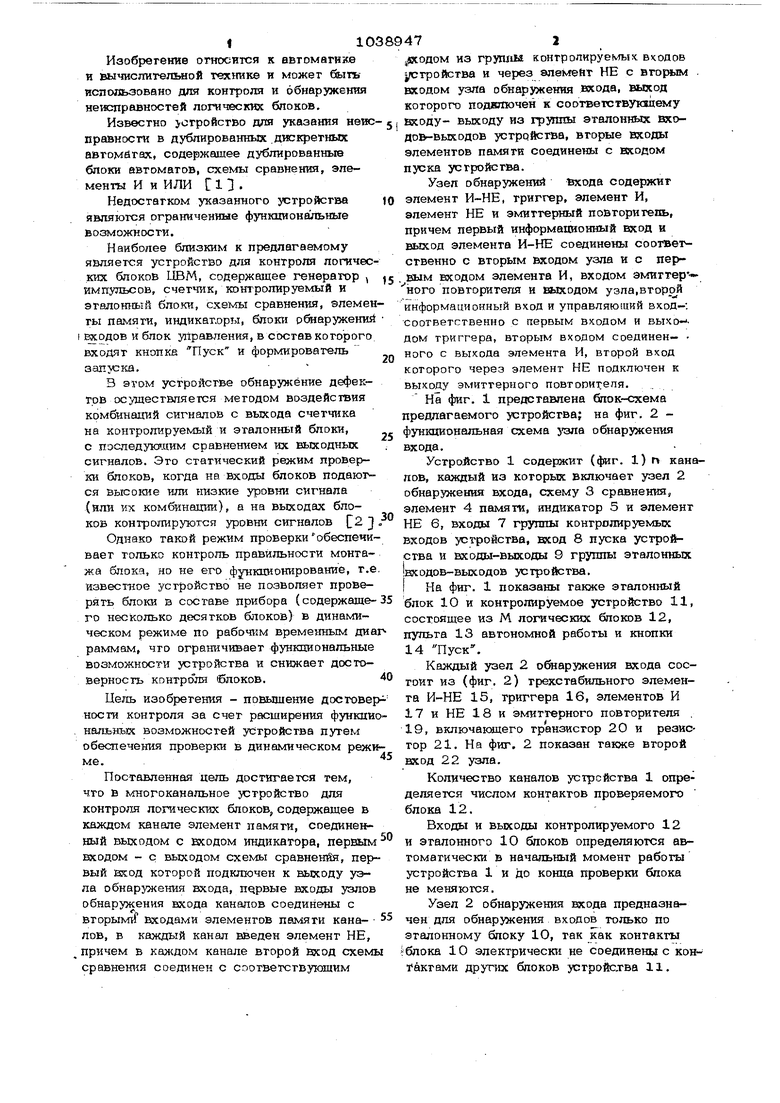

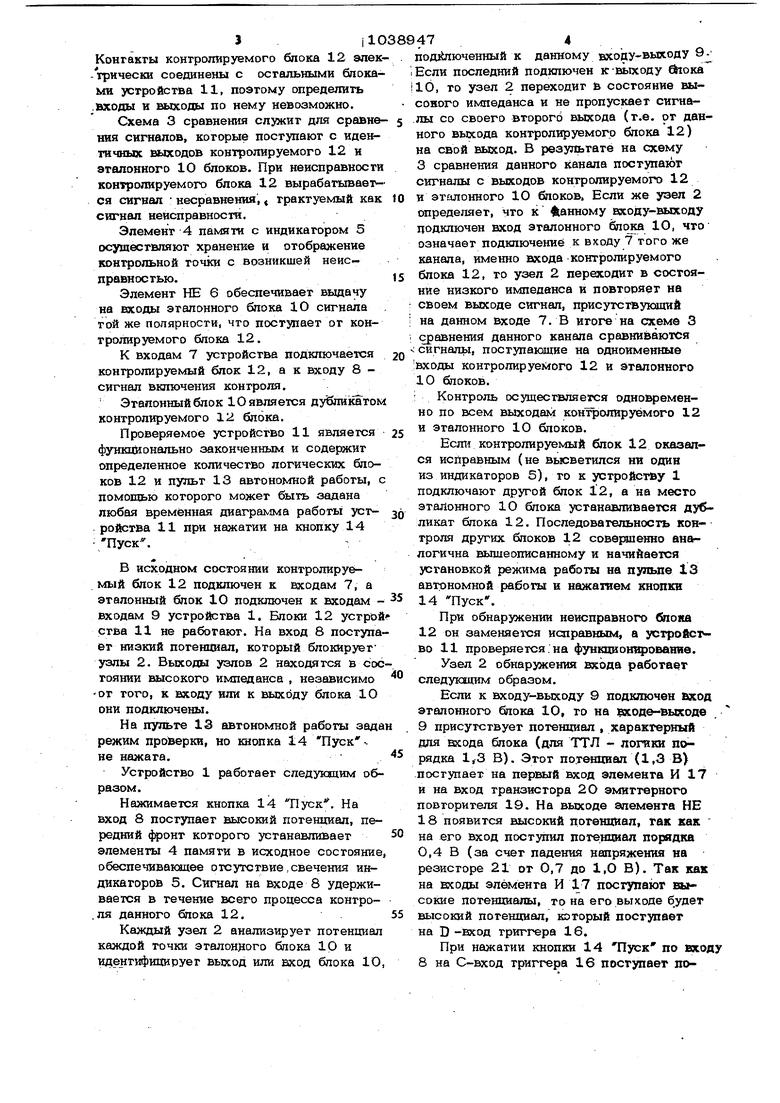

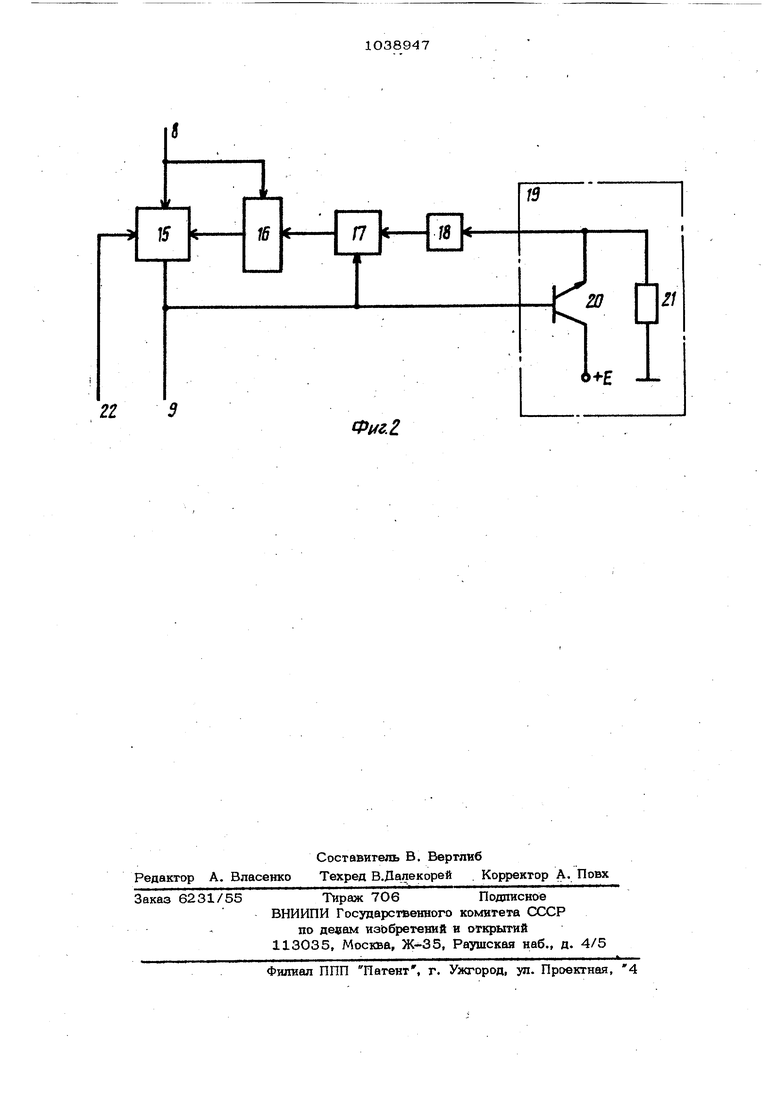

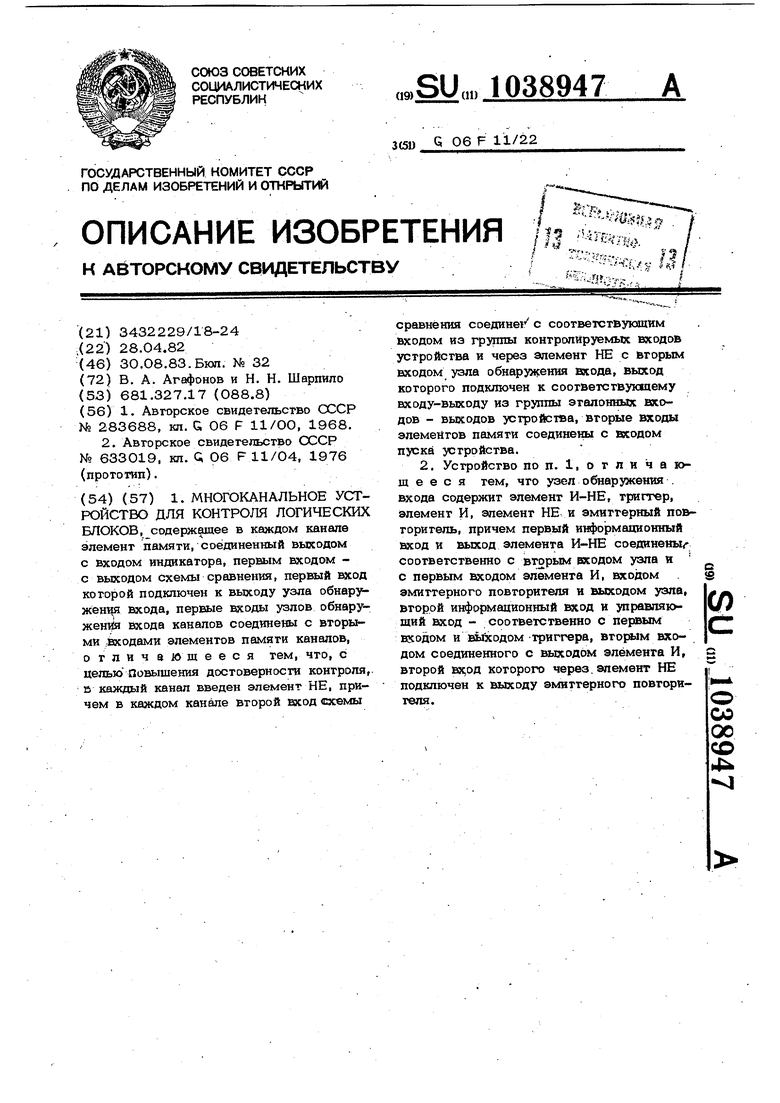

Изобрегение огносится к автомагикв и вычислительной технике и может бьтгь испояьзовано для контроля и обнаружения неисправностей логических блоков. Известно сгройство для указания нетя правности в дублированных дискретных автомйтах, содержащее дублированные блоки автоматов, схемы сравнения, элементы И и ИЛИ Г 11 . Недостатком указанного устройства являются ограниченные функционЕШЬные возможности. Наиболее близким к предлагаемому является устройство для контроля логичес ких блоков ЦВМ, содержащее генератор , импульсов, счетчик, контролируемый и эталонный бло.ки, схемы сравнения, элемен ты памяти, индикаторы, блоки обнаружений I исрдов и блок управления, в состав которого входят кнопка Пуск и формирователь sanyciis. В этом устройстве обнарумсёние дефектов осуществляется методом воздействия комбинаций сигналов с выхода счетчика на контролируемый и эталонный блоки, с последукудим сравнением их выходньк сигналов. Это статический режим проверки блоков, когда на входы блоков подаются высокие или шзкие уровни сигнала (йлн нх комбинации), а на выходах блоков контролируются уровни сигналов 2 Однако такой режим проверкиобеспечи вает только контроль правильности монтажа блока, но не его функционирование, т.е известное устройство не позволяет проверять блоки в составе прибора (содержащеГО несколько десятков блоков) в динамическом режиме по рабочим временным диа раммам, что ограничивает функциональные возможности устройства и снижает достоверность контроля блоков. Цель изобретения - повышение достове носга контроля за счет расширения функци . налЬНьк возможностей устройства путем обеспечения проверки в динамическом режи ме. Поставленная цель достигается тем, что в многоканальное устройство для контроля логических блоков, содержащее в каждом канале элемент памяти, соединенный выходом с входом индикатора, первым входом - с выходом схемы сравнения, пер вый Екод которой подключен к выходу узла обнаружения входа, первые входы узлов обнаружения входа каналов соединэны с вторыми ксодами элементов памяти кана- лов, в каждый канал введен элемент НЕ, причем в каждом канале второй вкод схемы сравнения соединен с соответствующим одом из груплн контролируемых вкодов |(стройства и через элемейт НЕ с вторым входом узла обнаружения входа, выход которого подключен к соответствукшему ВХОДУ- выходу из группы эталонных йходоБ-выходов устройства, вторые входы элементов памяти соединены с ЕКОДОМ пуска устройства. Узел обнаружений 1«ода содержит элемент И-НЕ, триггер, элемент И, элемент НЕ и эмиттерный повторитепь, причем первый информационный вход и выход элемента И-НЕ соединены соответственно с вторым йсодом узла и с первым входом элемента И, входом эмиттер - ного повторителя и выходом узла,второй информационный вход и управляющий вход-: Соответственно с первым входом и выко-. дом триггера, вторым входом соединен- кого с выхода элемента И, второй вход которого через элемент НЕ подключен к выходу эмиттерного повторителя. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 функциональная схема зпзла обнаружения входа. Устройство 1 содержит (фиг. 1) г каналов, каждый из которых включает узел 2 обнаружения входа, схему 3 сравнения, элемент 4 памяти, индикатор 5 и элемент НЕ 6, входы 7 группы контролируемых входов устройства, вкод 8 пуска устройства и входы-выходы 9 группы эталонных входов-выходов устройства. На фиг. 1 показаны также эталонный блок 10 и контролируемое устройство 11, состоящее из М логических блоков 12, пульта 13 автономной работы и кнопки 14 Пуск. Каждый узел 2 оЛаружения входа состоит из (фиг. 2) трехстабильного элемента И-НЕ 15, триггера 16, элементов И 17 и НЕ 18 и эмиттерного повторителя , 19, включающего транзистор 20 и резистор 21. На фиг. 2 показан также второй вход 22 узла. Количество каналов устройства 1 определяется числом контактов проверяемого блока 12. Входы и выходы контролируемого 12 и эталонного 10 блоков определяются автоматически в начальный момент работы устройства 1 и до конца проверки блока не меняются. Узел 2 обнаружения входа предназначен для обнаружения входов только по эталонному блоку 10, так как контакты блока 10 электрически не соединены с контактами других блоков устройства 11. 3ilO Конгакгы контролируемого блока 12 элек -грически соединены с остальными блоками устройства 11, поэтому определить .входы и выходы по нему невозможно. Схема 3 сравнения служит для сравнения сигналов, которые поступают с идентичных выходов контролируемого 12 и эталонного 10 блоков. При неисправности контролируемого блока 12 вырабатывает- ся сигнал несравнешш,« трактуемый как сигнал неисправности. Элемент 4 памяти с индикатором 5 осуществляют хранение и отображение контрольной точки с возникшей неисправностью. Элемент НЕ 6 обеспечивает выдачу на входы эталонного блока 10 сигнала гой же полярности, что поступает от контролируемого блока 12. К входам 7 устройства подключается контролируемый блок 12, а к входу 8 сигнал включения контроля. Эталонный блок 10 является ду6ли1штом контролируемого 12 блока. Проверяемое устройство 11 является фуншшонально законченным и содержит определенное количество логических блоков 12 и пульт 13 автономной работы, с помощью которого может быть задана любая временная диаграмма работы устpoiteTBa 11 при нажатии на кнопку 14 Пуск. В исходном состоянии контролируемый блок 12 подключен к входам 7, а эталонный блок 10 подключен к входам входам 9 устройства 1. Блоки 12 устрои ства 11 не работают. На вход 8 поступа ет низкий потенциал, который блокирует узлы 2. Выходы узлов 2 находятся в Сос тоянии высокого импеданса , независимо -от того, к входу или к выходу блока 1О они подключены. На пульте 13 автономной работы зада режим проверки, но кнопка 14 Пускне нажата. Устройство 1 работает следующим образом. Нажимается кнопка 14 Пуск. На вход 8 поступает высокий потенциал, передний (|чзонт которого устанавливает элементы 4 памяти в исходное состояние обеспечивающее отсутствие,свечения индикаторов 5. Сигнал на входе 8 удерживается в течение всего процесса контро,ля данного блока 12. Каждый узел 2 анализирует потенциал каждой точки эталонного блока IQ и идентифицирует выход или ЕХОД блока 10 474 подйлюченный к данному Bxoiay-выходу 9 Если последний подключен к-выходу ока О, то узел 2 переходит в состояние высоного импеданса и не пропускает сигна ° своего второго выхода (т.е. от данного выхода контролируемого блока 12) на свой выход. В результате на схему 3 сравнения данного канала поступают сигналы с выходов контролируемого 12 и эталонного 10 блоков. Если же узел 2 определяет, что к 41анному входу-выходу подключен вход эталонного блока 1О, что означает подключение к входу 7 того же канала, именно Екода контролируемого блока 12, то узел 2 переходит в состояние низкого импеданса и повторяет на своем выходе сигнал, присутствующий на данном входе 7. В итоге на схеме 3 сравнения данного канала сравниваются сигналь, поступающие на одноименные входы контролируемого 12 и эталонного 10 блоков. Контроль осуществляется одновременно по всем выходам контролируемого 12 и эталонного 10 блоков. Есл контролируемый блок 12 оказался исправным (не высветился ни один из индикаторов 5), то к устройству 1 подключают другой блок 12, а на место эталонного 10 блока устанавливается дубликат блока 12. Последовательность контроля других блоков 12 соверпенно аналогична вышеописанному и начийается установкой режима работы на пульпе 13 автономной работы и нажатием кнопки 14 Пуск. При обнаружении неисправного блока 12 он заменяется исправным, а устройс во 11 проверяется. на функцион ованяе. Узел 2 обнаружения входа работает следующим образом. Если к входу-выходу 9 подключен вход эталонного блока 10, то на вкоде-выходе 9 присутствует потешшал , характерный для входа блока (для ТТЛ - логики порддка 1,3 В). Этот потенциал (1,3 В поступает на первый вход элемента И 17 и на вход транзистора 2 О эмиттерного повторителя 19. На выходе глемента НЕ 18 появится высокий потенциал, так как на его вход поступил потешэтал порядка 0,4 В (за счет падения напряжения на резисторе 21 от 0,7 до 1,0 В). Так как на входы элемента И 17 nocrynaior высокие потенциалы, то на его выходе будет высокий потенциал, который поступает на D -вход триггера 16. При нажатии кнопки 14 Пуск по входу 8 на С-вход триггера 16 поступает поS103$9476

тенциал, который устанавливаег триггери контролируемого 12 блоков с входа 7

16 в единичное состояние. Высокий потен- входа-выхода 9 поступят на входы схемй циал с его выхода поступает на управляк щий вход трахстабипьного элемента И-НЕ 15, тем самым разрешая прохождение сигнала с входа 22 через вход-выход 9 на шсод эталонкотх) блока 10. , Если к входу-выходу 9 подключен выход эталонного блока 1О, то не восодевыходе 9 присутствует потенциал, характерный для выхода бпока ( 0,4 В или 2,4 В). При пштешшале « 0,4 В (низкий)| элемент И 17 будет закрыт по первому входу и на Р -вход триггера 16 поступит низкий потешгаал. При нажатии кнопки 14 Пуск, тригге 16 устанавливается в нулевое состояние, т.е. с его вькода на управляххций вход элемента И-НЕ 15 поступит низкий потенциал, блокирующий его переход в низкоимпедансное состояние. Следовательн6, сигналы с кодов эталонного 1О 3 сравнения. При поступлении на вход-выход 9 потендиала выхода 92,4В открывается эмиттерный повторитель 19. На вход элемента НЕ 18 поступает вью они и потенциал, а на его выходе будет низкий. На D-вход триггера 16 поступит низкий потенциал. При нажатии на кнопку 14 TlycK ситуация будет аналогичной случаю поступления п6 входу-выходу 9 потенциала выхода 40,4 В. Узел 2 обнаружения входа позволяет передавать входные сигналы контролируемого 12 блока к эталонному 10 той же полярности. Таким образом, предлагаемое устройство позволяет обеспечить контроль блоков в динамическом режиме,что и повышает достоверность контроля.

Фиг.1

f5

15

/5

D

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1226471A1 |

| Устройство для контроля профессиональных навыков радиотелеграфистов | 1983 |

|

SU1137500A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1180901A1 |

| Устройство для группового поиска кратных дефектов в комбинационных логических блоках | 1980 |

|

SU896628A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для проверки электрического монтажа | 1986 |

|

SU1336035A1 |

1. МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее в каждом канапе элемент памяти, соединенный выходом с Входом индикатора, первым входом с выходом схемы сравнения, первый вход которой подключен к выходу узла обнару жения входа, первые входы узлов обнаружен входа каналов соединены с вторыми .родами элементов памяти каналов, о тлич вющееся тем, что, с целью Повышения достоверности контроля, в каждый канал введен элемент НЕ, причем в каждом канале второй вход схемы сравнения соединег с соответствующим входом из группы контролируемых входов устройства и через элемент НЕ с вторым входом узла обнаружения вкода, выход которого подключен к соответствующему входу-выходу из группы эталонных вкодов - выходов устройства, вторые входы элементов памяти соединены с входом пуска устройства. 2. Устройство по п. 1, отличающее с я тем, что узел обнаружения . входа содержит элемент И-НЕ, триггер, элемент И, элемент НЕ и амиттерный повторитель, причем первый информационный вход и выход элемента И-НЕ соединены соответственно с вторым входом узла и с первым входом элемента И, входом эмиттерного повторителя и выходом узла, (О второй информационный вход и управляющий вход - соответственно с первым с входом и в1 йсодом триггера, вторым входом соединенного с выходом элемента И, второй вх;од которого через. элемент НЕ подключен к выходу эмиттерного повторителя. 00 ос со 4

гг

г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU283688A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-08-30—Публикация

1982-04-28—Подача