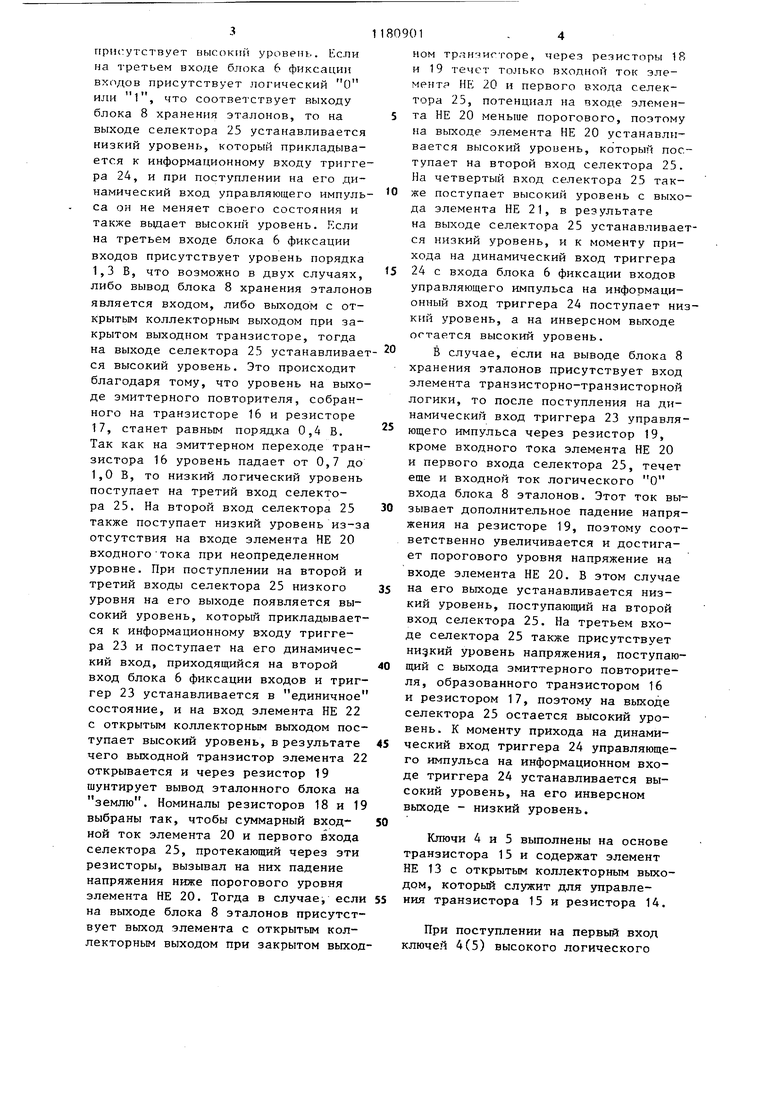

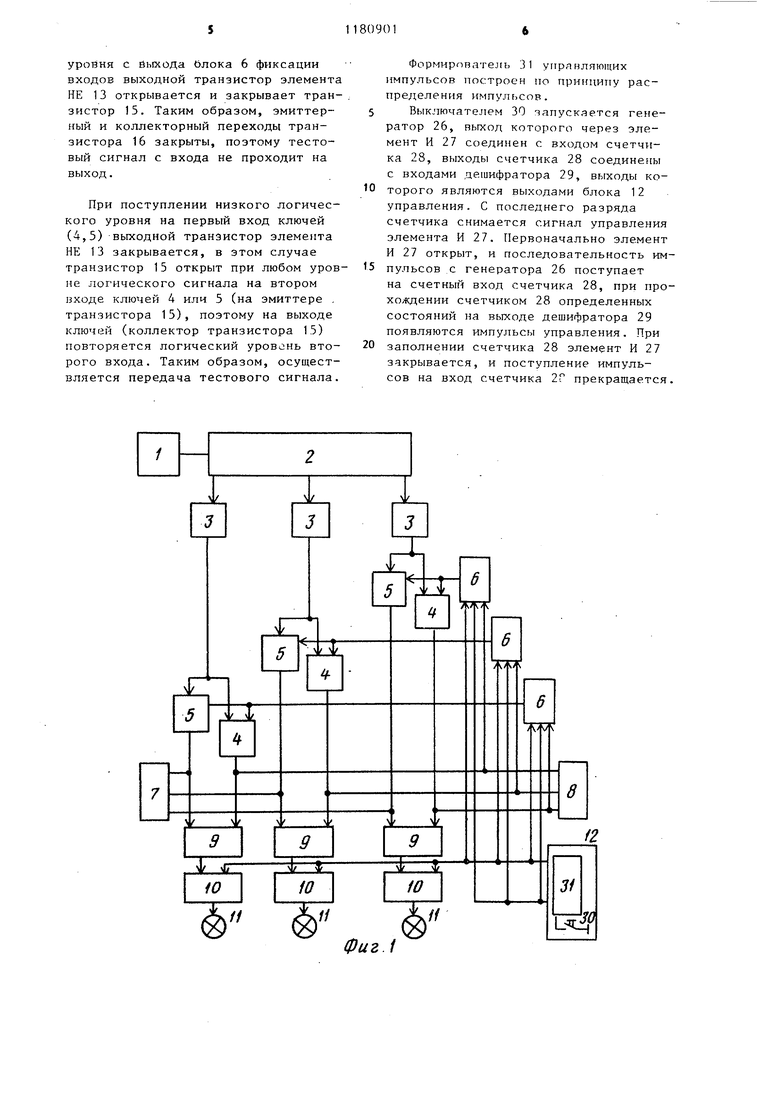

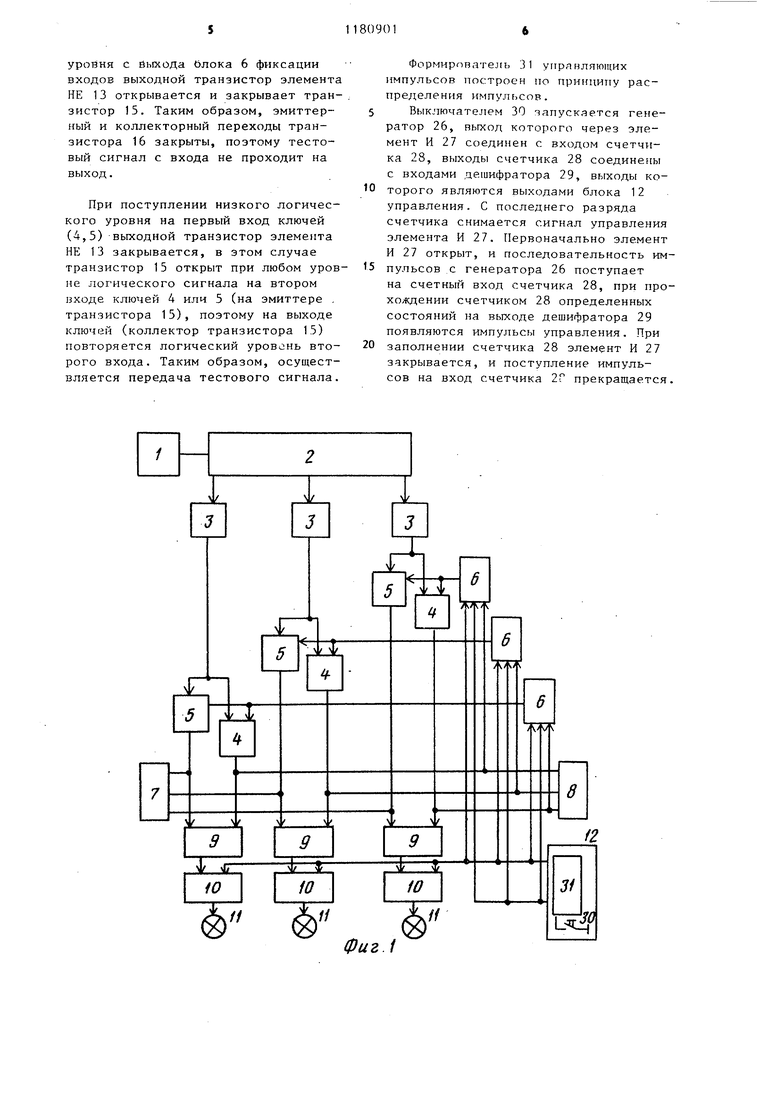

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля исправности логических блоков и цифровых интегральных схем, установле }ных на печатные штаты логических блоков .., .На фиг. 1 пре(С.тавлена структурная схемЗ)- Предлагаемог;о; устройства; на ф-иг. 2 - ключ;- нас г.- 3 - блок фиксации входов; ла фиг):, 4 блок Устройст.во содердич - генератор 1 импулцсов счетчик 2, эмиттерные повторители 3, ключи 4 и ключи 5, блок б фиксации входов, контролируемый блок 7 и блок 8 хранения эталонов, элементы 9 сравнения, элементы 10 памяти, элементы 11 индикации, блок 12 управления. Элемент 13 НЕ подключен к резистору 14 и базе транзистора 15, транзистор 16 через резисторы 17-19 соединен с элементами НЕ 20-22. Входы триггеров 23 и 24 соединены с выходом селектора 2 Генератор 26 импульсов через элемент И 27 соединен со счетчиком 28, выходы которого подключены к дешифратору 29, Выключателем 30 запускается формирователь 31 управляющих импульсов. Устройство работает следующим образом. Выключатель 30 запускает формирователь 31 управляющих импульсов, бла ггедаря чему начинают функционировать блоки 6 фиксаций входов, которые при обнаружении входов на соответствующих выводах блока 8 хранения эталонов вырабатывают низкие уровни на инверсных выходах триггеров 24, с помощью которых соответствующие пары ключей и 5 и входные тестовые сигналы от счетчика 2 через эмиттерные повторители 3 и открытые пары ключей 4 и 5 поступают на входы контро лируемого блока 7 и блока 8 хранения эталонов. Образование всевозможных тестовых наборов логических О и 1 происходит благодаря подаче на счетный вход счетчика 2 импульсов, вырабатываемых генератором 1 импуль сов . Элементы 9 сравнения сравнивают сигналы на выходах с блоков 7 и 8 и в случае несовпадения выдают сигналы на соответствующий элемент 10 памяти, которьй в этом случае устанавливается в состояние, соотвс тствующее свечению элемента 11. Если контролируемый блок 7 исправен, то в конце проверки, длительность которой задается формирователем 31 управляющих импульсов, ни один из элементов 11 не светится. Если контролируемый блок 7 является неисправным, то в конце проверки, в зависимости от характера неисправности, высвечивается определенная комбинация элементов 11. Если контролируемый блок 7 является интегральной микросхемой, установленной на печатную плату цифрового , то тестовые сигналы, поступающие на ее входы, исключают влияние сигналов, ранее присутствующих на этих входах. Устранение этого влияния происходит благодаря тому, что тестовые сигналы снимаются с выходов эмиттерных повторителей 3, которые обладают низким значением выходного импеданса. Поскольку значения выходных импедансов источников напряжения, к которым подключены входы контролируемой микросхемы 7, превышают значения выходных импедансов импульсов эмиттерных повторителей 3, происходит образование тестовых сигналов, а не тех, что присутствуют в схеме. Таким образом, осуществляется электрическая изоляция контролируемой микросхемы от логического узла, в котором она установлена. Блоки 6 фиксации входов построены таким образом, что каждый из них на выходе вырабатывает низкий уровень, если на выводе блока 8 эталонов был зарегистрирован потенциал, характерный для входа блока (для транзисторно-транзисторной логики, порядка 1,3 В), и после шунтирования этого вывода на землю через резистор 19 протекает ток логического нуля. Во всех остальных случаях, когда на выводе блока 8 эталонов присутствует либо логический О, либо логическая 1, либо уровень порядка 1,3 В, а после шунтирования этого вывода на землю не протекает ток логического О, блок 6 фиксации входов вырабатывает высокий уровень, что соответствует выходу блока 8 эталонов. В исходном состоянии триггер 24 сброшен, и на его инверсном выходе

31

присутствует высоки уровень. Если на третьем входе блока 6 фиксации входов присутствует логический О или 1, что соответствует выходу блока 8 хранения эталонов, то на выходе селектора 25 устанавливается низкий уровень, который прикладывается к информационному входу триггера 24, и при поступлении на его динамический вход управляющего импульса он не меняет своего состояния и также вьщает высокий уровень. Ксли на третьем входе блока 6 фиксации входов присутствует уровень порядка 1,3 В, что возможно в двух случаях, либо вывод блока 8 хранения эталонов является входом, либо выходом с открытым коллекторным выходом при закрытом выходном транзисторе, тогда на выходе селектора 25 устанавливается высокий уровень. Это происходит благодаря тому, что уровень на выходе эмиттерного повторителя, собранного на транзисторе 16 и резисторе 17, станет равным порядка 0,4 В. Так как на эмиттерном переходе транзистора 16 уровень падает от 0,7 до 1,0 В, то низкий логический уровень поступает на третий вход селектора 25. На второй вход селектора 25 также поступает низкий уровень из-за отсутствия на входе элемента НЕ 20 входного-тока при неопределенном уровне. При поступлении на второй и третий входы селектора 25 низкого уровня на его выходе появляется высокий уровень, которь0Ч прикладывается к информационному входу триггера 23 и поступает на его динамический вход, приходящийся на второй вход блока 6 фиксации входов и триггер 23 устанавливается в единичное состояние, и на вход элемента НЕ 22 с открытым коллекторным выходом поступает высокий уровень, в результате чего выходной транзистор элемента 22 открывается и через резистор 19 шунтирует вывод эталонного блока на землю. Номиналы резисторов 18 и 19 выбраны так, чтобы суммарный входной ток элемента 20 и первого входа селектора 25, протекающий через эти резисторы, вызывал на них падение напряжения ниже порогового уровня элемента НЕ 20. Тогда в случае, если на выходе блока 8 эталонов присутствует выход элемента с открытым коллекторным выходом при закрытом выход0901 - 4

ном транзисторе, герез резистетры 18 и 19 течет только входной ток элемента 20 и первого входа селектора 25, потенциал на входе элемента НЕ 20 меньше порогового, поэтому на выходе элемента НЕ 20 устанавливается высокий уроиень, который поступает на второй вход селектора 25. На четвертый вход селектора 25 также поступает высокий уровень с выхода элемента НЕ 21, в результате на выходе селектора 25 устанавливается низкий уровень, и к моменту прихода на динамический вход триггера

5 24 с входа блока 6 фиксации входов управляющего импульса на информационный вход триггера 24 поступает низкий уровень, а на инверсном выходе остается высокий уровень.

0 В случае, если на выводе блока 8 хранения эталонов присутствует вход элемента транзисторно-транзисторной логики, то после поступления на динамический вход триггера 23 управляющего импульса через резистор 19, кроме входного тока элемента НЕ 20 и первого входа селектора 25, течет еще и входной ток логического О входа блока 8 эталонов. Этот ток вызывает дополнительное падение напряжения на резисторе 19, поэтому соответственно увеличивается и достигает порогового уровня напряжение на входе элемента НЕ 20. В этом случае

5 на его выходе устанавливается низкий уровень, поступаюпщй на второй вход селектора 25. На третьем входе селектора 25 также присутствует нидкий уровень напряжения, поступающий с выхода эмиттерного повторителя, образованного транзистором 16 и резистором 17, поэтому на выходе селектора 25 остается высокий уровень. К моменту прихода на динамический вход триггера 24 управляющего импульса на информационном входе триггера 24 устанавливается высокий уровень, на его инверсном выходе - низкий уровень.

Ключи 4 и 5 выполнены на основе транзистора 15 и содержат элемент НЕ 13 с открытым коллекторным выходом, который служит для управле5 ния транзистора 15 и резистора 14.

При поступлении на первый вход ключей 4(5) высокого логического

уровня с йыхода Ьлока 6 фиксации входов выходной транзистор элемента НЕ 13 открывается и закрывает транзистор 15. Таким образом, эмиттерный и коллекторный переходы транзистора 16 закрыты, поэтому тестовый сигнал с входа не проходит на выход.

При поступлении низкого логического уровня на первый вход ключей (4,5) выходной транзистор элемента НЕ 13 закрывается, в этом случае транзистор 15 открыт при любом уровне логического сигнала на втором входе ключей 4 или 5 (на эмиттере , транзистора 15), поэтому на выходе ключей (коллектор транзистора 15) повторяется логический уровень второго входа. Таким образом, осуществляется передача тестового сигнала.

Формирователь 31 упраршяющих импульсов построен по принципу распределения импульсов.

Выключателем 30 запускается генератор 26, выход которого через элемент И 27 соединен с входом счетчика 28, выходы счетчика 28 соединены с входами дешифратора 29, выходы которого являются выходами блока 12 управления. С последнего разряда счетчика снимается сигнал управления элемента И 27. Первоначально элемент И 27 открыт, и последовательность импульсов с генератора 26 поступает

на счетный вход счетчика 28, при прохождении счетчиком 28 определенных состояний на выходе дешифратора 29 появляются импульсы управления. При заполнении счетчика 28 элемент И 27 закрывается, и поступление импульсов на вход счетчика 2Г прекращается.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1256032A1 |

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для вывода информации | 1985 |

|

SU1285460A1 |

| Устройство для контроля напряжения | 1973 |

|

SU789827A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| УСТРОЙСТВО САНКЦИОНИРОВАНИЯ ДОСТУПА | 1991 |

|

RU2005870C1 |

| Логический пробник | 1983 |

|

SU1132268A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее генератор импульсов, счетчик, первую группу ключей, блоки фиксации входов, блок хранения эталонов, элементы сравнения, элементы памяти, блок управления, элементы индикации, выход генератора импульсов соединен с счетным входом счетчика, выход обнуления блока управления соединен с входами обнуления блоков фиксации входов и с входами обнуления элементов памяти, тактовый выход блока управления соединен с синхровходами фиксации входов, информационные выходы блоков фиксации входов соединены соответственно с входами управления первой группы ключей, выходы которых соединены соответственно с выводами блока хранения эталонов, и с первыми входами элементов сравнения, вторые входы которых соединены с. выводами контролируемого логического блока, выходы элементов сравнения соединены соответственно с информационными входами элементов памяти, выходы которых соединены соответственно с элементами индикации, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены эмиттерные повторители и вторая группа ключей, причем информационные вМходы счетчика соединены с входами эмиттерных сл повторителей соответстврнно, управляющие входы второй группы ключей объединены с управляющими входами первой группы ключей соответственно, выходы эмиттерных повторителей соединены соответственно с информационными входами первой группы ключей и с 00 информационными входами второй групо ;о пы ключей, выходы которых соединены с вторыми входами элементов сравнения соответственно, информационные входы блоков фиксации входов соединены с вторыми входами элементов сравнения.

Фиг.1

Г

f

Ч{5)

Фиг.2

/ фиг.З

Фиг л

л.

| Устройство для контроля цифровыхузлОВ | 1979 |

|

SU807303A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-03-05—Подача