zt

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1529221A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для контроля памяти | 1984 |

|

SU1236558A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Логический анализатор | 1986 |

|

SU1410033A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для обмена данными | 1986 |

|

SU1352497A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля вычислительных систем. Цель изобретения - повышение полноты контроля за счет исключения потерь регистрируемой информации. При этом анализатор обеспечивает выборочную запись входной информации с учетом текущих значений признаков, характеризующих эту информацию, а также возможность перевода объекта контроля в квазиреальный масштаб времени путем соответствующего изменения так- тирования объекта контроля. 2 з.п. ф-лы, 3 ил, 1 табл.

Изобретение относится к вычислительной технике и может быть использовано для контроля вычислительных систем.

Цель изобретения - повышение полноты контроля за счет исключения потерь регистрируемой информации о работе контролируемого объекта.

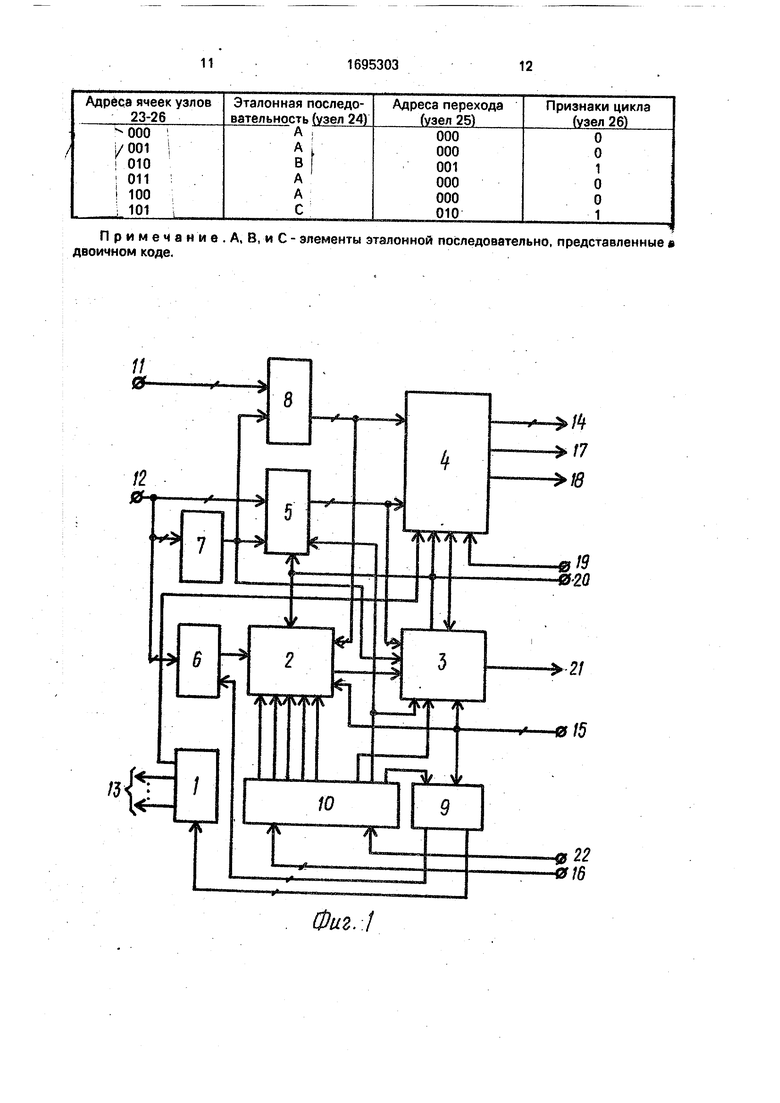

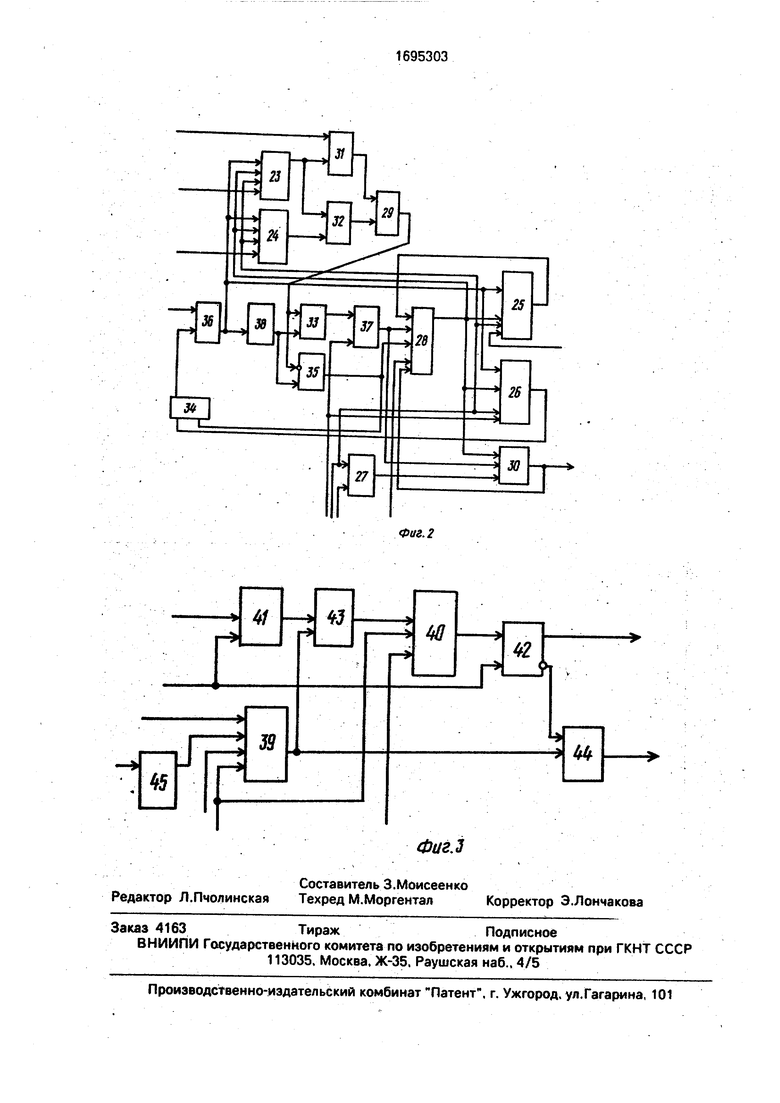

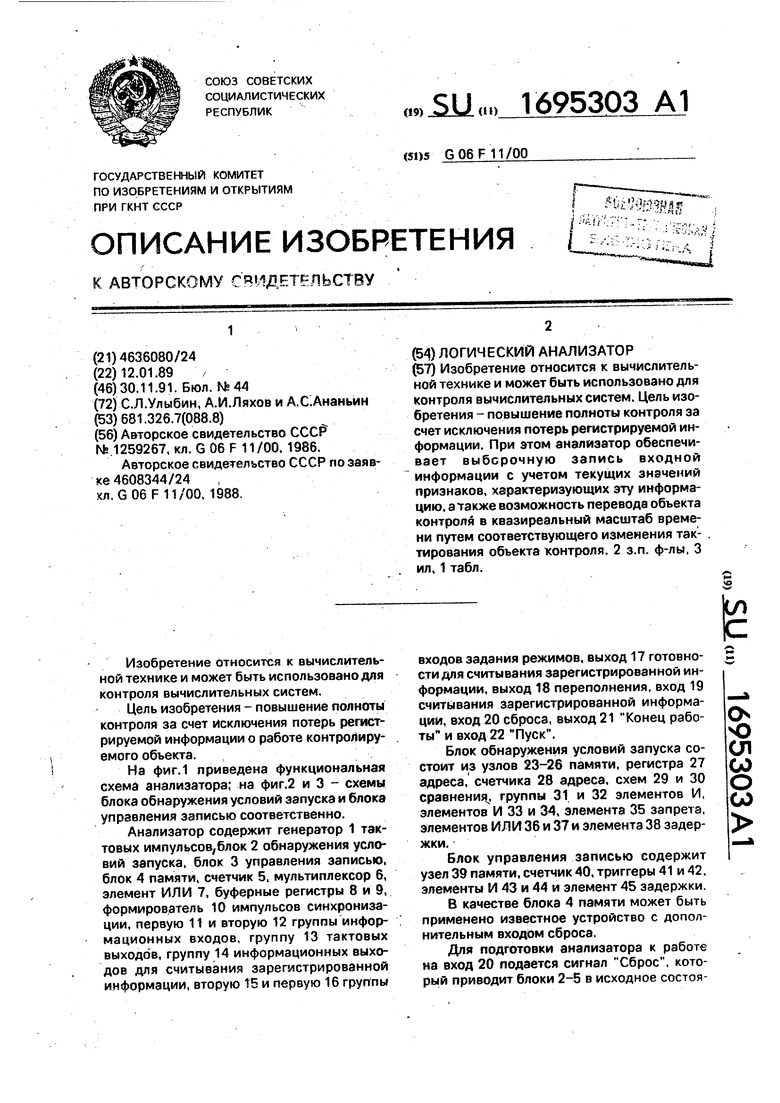

На фиг.1 приведена функциональная схема анализатора; на фиг.2 и 3 - схемы блока обнаружения условий запуска и блока управления записью соответственно.

Анализатор содержит генератор 1 тактовых импульсов,блок 2 обнаружения условий запуска, блок 3 управления записью, блок 4 памяти, счетчик 5, мультиплексор 6, элемент ИЛИ 7, буферные регистры 8 и 9, формирователь 10 импульсов синхронизации, первую 11 и вторую 12 группы информационных входов, группу 13 тактовых выходов, группу 14 информационных выходов для считывания зарегистрированной информации, вторую Т5 и первую 16 группы

входов задания режимов, выход 17 готовности для считывания зарегистрированной информации, выход 18 переполнения, вход 19 считывания зарегистрированной информации, вход 20 сброса, выход 21 Конец работы и вход 22 Пуск.

Блок обнаружения условий запуска состоит из узлов 23-26 памяти, регистра 27 адреса, счетчика 28 адреса, схем 29 и 30 сравнения, группы 31 и 32 элементов И, элементов И 33 и 34, элемента 35 запрета, элементов ИЛ И 36 и 37 и элемента 38 задержки.

Блок управления записью содержит узел 39 памяти, счетчик 40, триггеры 41 и 42. элементы И 43 и 44 и элемент 45 задержки.

В качестве блока 4 памяти может быть применено известное устройство с дополнительным входом сброса.

Для подготовки анализатора к работе на вход 20 подается сигнал Сброс, который приводит блоки 2-5 в исходное состояО

ю ел

00

о

00

ние. Затем на группу 16 входов подается код, в соответствии с которым по приходу сигнала на вход 22 на одном из восьми выходов блока 10 появляется синхроимпульс, необходимый для загрузки информации о режимах работы анализатора с входов 15 в блоки 2,3 и 9.

Подготовка к работе блока 2 обнаружения условий запуска заключается в осуществлении q циклов записи (где q - длина эталонной последовательности, q Ј п). Каждый из этих циклов состоит из четырех последовательных записей соответствующей информации по адресам, отведенным для узлов 23-26 памяти, При этом в зависимо- сти от кода на входах 16 на одном из выходов формирователя 10 появляется сигнал, который поступает на вход записи, соответствующий коду узла памяти. В первом из циклов запись производится в нулевую ячейку узлов 23-26, так как на их адресные входы приходит информация с обнуленного счетчика 28. Сигнал с выхода формирователя 10, кроме входа записи узла 26 памяти поступает на вход элемента ИЛИ 37, сигнал с выхода которого поступает на счетный вход счетчика 28 и задним фронтом увеличивает его содержимое нэ единицу. Таким образом, готовится адрес следующей ячейки узлов памяти,

Узел 24 памяти имеет емкость n x m, где п - максимальная длина эталонной информации; m - разрядность входной информации. Он предназначен для хранения эталонной информации, причем в первой его ячейке хранится первый элемент последовательности, во второй - второй элемент и т.д.

Узел 23 памяти имеет емкость n x m и предназначен для хранения кодов маски. При необходимости исключить анализ 1-го (,....т) равзряда j-ro (,...,n) элемента эталонной последовательности надо записать О в 1-й разряд j-й ячейки узла, в остальные разряды всех ячеек надо записать

« И

Узел 25 памяти имеет емкость n x к, где к 1оо,2П. Он предназначен для хранения адресов перехода. Адрес перехода представляет собой адрес ячейки узла 24, храня- щей элемент последовательности, к сравнению с которым надо перейти при несовпадении поступившего информационного слова с очередным элементом эталонной последовательности.

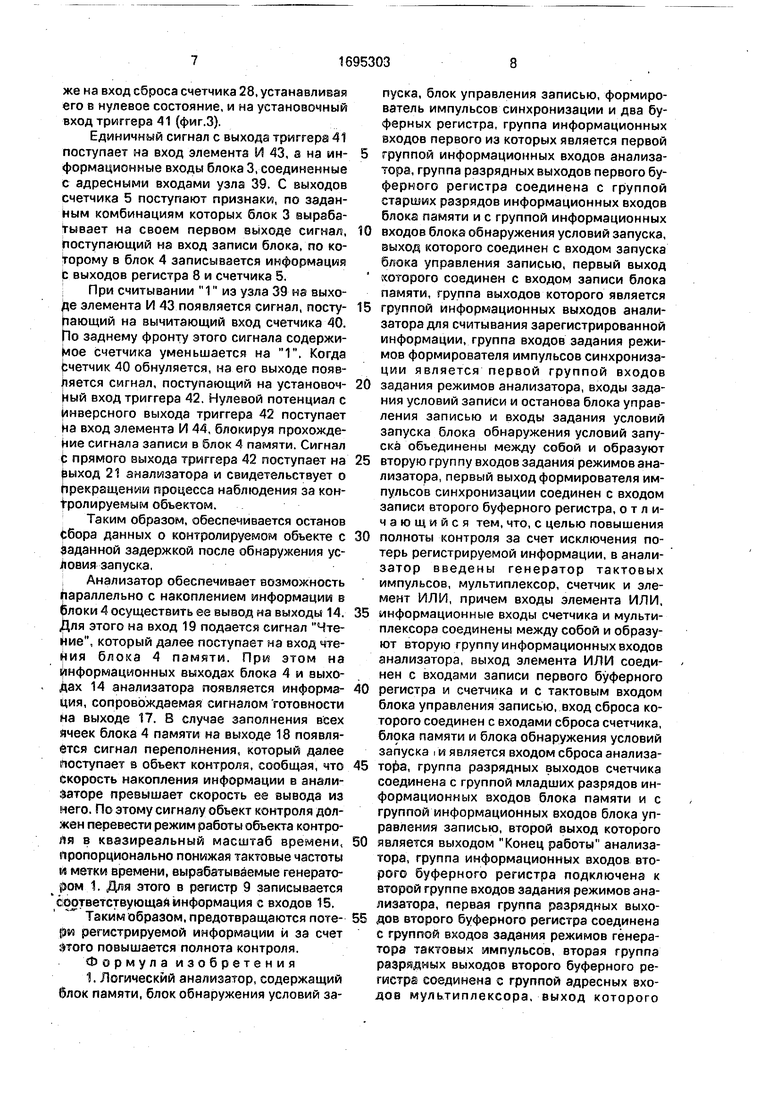

Узел 26 памяти имеет емкость n x 1 и предназначен для хранения признаков цикла. Единичный признак цикла разрешает провести цикл сравнения поступившего слова с элементом эталонной последовательности, адрес которого считан из узла 25 (см. таблицу).

Данные о поведении контролируемого объекта поступают в виде m-разрядных двоичных слов.

Очевидно, что если два последовательно поступивших слова совпали с первыми двумя элементами эталонной последовательности, а третье - не совпало, то необходимо произвести сравнение третьего слова с вторым элементом эталонной последовательности, так как возможно, что двоичный код третьего слова - это А. Точно так же при совпадении пяти слов с первыми пятью элементами приведенной последовательности и несовпадении шестого слова с шестым элементом, необходимо сравнить шестое слово с третьим элементом последовательности, так как возможно, что двоичный код шестого слова - это В. Если шестое слово не совпало с третьим элементом последовательности, то его надо сравнить с вторым элементом эталонной последовательности.

После окончания q циклов записи осуществляется запись в регистр 27 числа циклов (двоичный код q).

При подготовке к работе блока 3 21 раз (I - количество признаков на входах 12) осуществляется запись информации в узел 24, адресные входы которого подключены к выходам счетчика 5. В первом цикле информация будет записана в нулевую ячейку узла 39, так как счетчик 5 обнулен. Задним фронтом сигнала с выхода формирователя 10 содержимое счетчика увеличивается на единицу. Таким образом, подготавливается адрес следующей ячейки узла 39 памяти.

Узел 39 памяти имеет емкость 2x1, где I количество признаков, анализируемых устройством. Перед началом работы в ячейки узла 34, адресные константы которых совпадают с комбинациями признаков, сопровождающими выбранные для трассировки данные, записываются 1, остальные ячейки обнуляются.

В счетчик 40 заносится двоичный код количества данных, которые необходимо запомнить в блоке 4 после обнаружения блоком 2 заданных условий запуска. После этого на вход 20 анализатора поступает сигнал Сброс, обнулящий счетчик 5, счетчик 28 и триггеры 41 и 42. На этом подготовка анализатора к работе заканчивается, после чего логический анализатор подключается к выходам объекта контроля и работает следующим образом.

С группы 13 выходов анализатора в объект контроля поступают тактовые частоты и метки времени, определяемые кодом с выходов регистра 9. Изменяя содержимое первой группы выходов регистра 9, можно изменять тактовые частоты и метки времени на группе выходов блока 1. С выхода блока 1 опорная частота поступает на тактовый вход блока 4 памяти.

Если контролируемым объектом является ЭВМ с магистралью МПИ ГОСТ 26.765.51-86, то группа информационных входов 11 подключается к мультиплексированным линиям адрес - данные (АДОО

АД15), а группа входов 12 признаков - к линиям управляющих сигналов.

Анализатор работает следующим образом.

С группы входов 11 на информацией- ные входы регистра 8 поступают данные о работе объекта контроля. Признаки, характеризующие эти данные, поступают с входов 12 анализатора на информационные входы счетчика 5 и мультиплексора 6. Кроме того, признаки, указывающие на изменения информации, приходящей на входы 11 и 12 анализатора, поступают на входы элемента ИЛИ 7. Сигнал с выхода элемента ИЛИ 7 поступает на входы записи счетчика 5 и ре- гистра 8, записывая в них информацию, и на тактовый вход блока 3 управления записью.

На управляющий вход мультиплексора 6 с второй группы разрядных выходов регистра 9 подается код, который разрешает прохождение через мультиплексор 6 признака, сигнализирующего о наличии на входе 11 данных, последовательность которых отслеживает блок 2 (например, признак Команда при отслеживании последователь- ности команд или сигнал записи в какой-либо регистр при отслеживании последовательности изменения информации в этом регистре).

Сигнал с выхода мультиплексора 6 по- ступает на первый вход элемента ИЛИ 36 (фиг.2) с выхода которого сигнал поступает на вход элемента 38 задержки и входы считывания узлов 23-26 памяти. Из ячейки узлов, адрес которых определяется счетчиком 38, считывается информация. Код очередного элемента эталонной последовательности с группы выходов узла 24 поступает на входы группы элементов И 32. Код маски для очередного элемента эталонной последова- тельности с группы выходов узла 23 поступает на входы групп элементов И 31 и 32. Адрес перехода для очередного элемента отслеживаемой последовательности с выходов 25 памяти поступает на информацией- ные входы счетчика 28, Признак цикла с выхода узла 26 поступает на вход элемента И 24.

На выходах группы элементов И 32 появляется код очередного элемента эталонной последовательности, а на выходах группы элементов И 31 - код очередного слова из потока данных о состоянии контролируемого объекта. Причем, если из 1-го разряда кода маски считан О, то на 1-х выходах групп элементов И 31 и 32 появляется О. Таким образом, обеспечивается маскирование разрядов слова, не подлежащих анализу.

Информация с выходов групп элементов И 31 и 32 поступают соответственно на входы схемы 29 сравнения.

Если коды равны, то схема 29 вырабатывает на своем выходе единичный сигнал, если коды не равны - нулевой. Этот сигнал поступает на входы элементов И 33 и 27 и элемента 35 запрета, на другие входы которых с выхода элемента 38 задержки поступает сигнал, задержанный на время срабатывания узлов 23-26, групп элементов И 31 и 32 и схемы 29 сравнения.

Если сигнал с выхода схемы 29 нулевой (поступившее слово не совпадает с очередным элементом эталонной последовательности), то на выходе элемента 35 запрета появляется сигнал, который поступает на вход элемента И 34 и на вход записи счетчика 28. При этом в счетчик 31 записывается адрес перехода, приходящий на его информационные входы с выходов узла 25. При этом из узла 26 считывается 1. на выходе элемента И 34 появляется сигнал, поступающий на вход элемента ИЛИ 36. В результате запускается новый цикл работы блока 2 обнаружения условий запуска.

Если из блока памяти 21 считан О, то на выходе элемента И 34 сигнала нет. В счетчик 28 при этом записывается нулевой код из узла 25 памяти. Блок 2 заканчивает цикл сравнения поступившего слова с элементами эталонной последовательности и переходит к анализу следующего слова, приходящему с регистра 8.

Если сигнал с выхода блока сравнения 32-единичный (поступившее слово совпадает с очередным элементом эталонной последовательности), то на выходе элемента И 33 появляется сигнал 1, который через элемент ИЛИ 37 поступает на счетный вход счетчика 28, добавляя к его содержимому единицу, а также разрешает работу схемы 30 сравнения.

Тавким образом, на счетчике 31 формируется адрес следующего элемента эталонной последовательности.

Схема сравнивает между собой коды с выходов регистра 27 и счетчика 28. При равенстве этих кодов на ее выходе вырабатывается сигнал, являющийся сигналом запуска блока 3. Этот сигнал поступает также на вход сброса счетчика 28, устанавливая его в нулевое состояние, и на установочный вход триггера 41 (фиг.З).

Единичный сигнал с выхода триггера 41 поступает на вход элемента И 43, а на информационные входы блока 3, соединенные с адресными входами узла 39. С выходов счетчика 5 поступают признаки, по заданным комбинациям которых блок 3 вырабатывает на своем первом выходе сигнал, поступающий на вход записи блока, по которому в блок 4 записывается информация с выходов регистра 8 и счетчика 5.

При считывании 1 из узла 39 на выходе элемента И 43 появляется сигнал, поступающий на вычитающий вход счетчика 40. По заднему фронту этого сигнала содержимое счетчика уменьшается на 1. Когда :четчик 40 обнуляется, на его выходе появляется сигнал, поступающий на установочный вход триггера 42, Нулевой потенциал с инверсного выхода триггера 42 поступает йа вход элемента И 44, блокируя прохожде- Йие сигнала записи в блок 4 памяти. Сигнал Ј прямого выхода триггера 42 поступает на Ьыход 21 анализатора и свидетельствует о прекращении процесса наблюдения за контролируемым объектом.

Таким образом, обеспечивается останов (бора данных о контролируемом объекте с заданной задержкой после обнаружения условия запуска.

Анализатор обеспечивает возможность параллельно с накоплением информации в 4 осуществить ее вывод на выходы 14. Для этого на вход 19 подается сигнал Чтение, который далее поступает на вход чтения блока 4 памяти. При этом на информационных выходах блока 4 и выходах 14 анализатора появляется информация, сопровождаемая сигналом готовности на выходе 17. В случае заполнения всех Ячеек блока 4 памяти на выходе 18 появляется сигнал переполнения, который далее поступает в объект контроля, сообщая, что Скорость накопления информации в анализаторе превышает скорость ее вывода из него. По этому сигналу объект контроля должен перевести режим работы объекта контроля в квазиреальный масштаб времени, пропорционально понижая тактовые частоты и метки времени, вырабатываемые генератором 1. Для этого в регистр 9 записывается соответствующая информация с входов 15. Таким образом, предотвращаются потери регистрируемой информации и за счет Зтого повышается полнота контроля.

Формула изобретения

группой информационных входов анализатора, группа разрядных выходов первого буферного регистра соединена с группой старших разрядов информационных входов блока памяти и с группой информационных

0 входов блока обнаружения условий запуска,

выход которого соединен с входом запуска

блока управления записью, первый выход

которого соединен с входом записи блока

памяти, группа выходов которого является

5 группой информационных выходов анализатора для считывания зарегистрированной информации, группа входов задания режимов формирователя импульсов синхронизации является первой группой входов

0 задания режимов анализатора, входы задания условий записи и останова блока управления записью и входы задания условий запуска блока обнаружения условий запуска объединены между собой и образуют

5 вторую гру п пу входо в за дан ия режимов анализатора, первый выход формирователя импульсов синхронизации соединен с входом записи второго буферного регистра, отличающийся тем, что, с целью повышения

0 полноты контроля за счет исключения потерь регистрируемой информации, в анализатор введены генератор тактовых импульсов, мультиплексор, счетчик и элемент ИЛИ, причем входы элемента ИЛИ,

5 информационные входы счетчика и мультиплексора соединены между собой и образуют вторую группу информационных входов анализатора, выход элемента ИЛИ соединен с входами записи первого буферного

0 регистра и счетчика и с тактовым входом блока управления записью, вход сброса которого соединен с входами сброса счетчика, блока памяти и блока обнаружения условий запуска i и является входом сброса анализа5 тора, группа разрядных выходов счетчика соединена с группой младших разрядов информационных входов блока памяти и с группой информационных входов блока управления записью, второй выход которого

0 является выходом Конец работы анализатора, группа информационных входов второго буферного регистра подключена к второй группе входов задания режимов анализатора, первая группа разрядных выхо5 дов второго буферного регистра соединена с группой входов задания режимов генератора тактовых импульсов, вторая группа разрядных выходов второго буферного регистра соединена с группой адресных входов мультиплексора, выход которого

соединен с входом разрешения блока обнаружения условий запуска, входы с первого по пятый записи условий запуска которого подключены к выходам с второго по шестой формирователя импульсов синхронизации, седьмой выход которого соединен со счетным входом счетчика и с первым входом записи блока управления записью, восьмой выход формирователя импульсов синхронизации соединен с вторым входом записи блока управления записью, вход чтения блока памяти является входом считывания зарегистрированной информации анализатора, вход разрешения формирователя импульсов синхронизации является входом Пуск анализатора, выход генератора тактовых импульсов соединен с тактовым входом блока памяти, группа выходов генератора тактовых импульсов является группой тактовых выходов анализатора для подключения к тактовым входам кон7ролируемого объекта, первый выход блока памяти является выходом готовности анализатора для считывания зарегистрированной информации, второй выход блока памяти является выходом переполнения анализатора.

первой схемы сравнения и подключены к выходам счетчика адреса, входы считывания узлов памяти с первого по четвертый и вход элемента задержки подключены к выходу первого элемента ИЛИ, первый вход которого является t входом разрешения блока, одноименные информационные входы узлов памяти с первого по четвертый соединены с соответствующими информационными входами регистра адреса и образуют входы задания условий запуска блока, входы записи узлов памяти с первого по четвертый и вход записи регистра адреса являются входами записи с первого по пятый блока, первые группы входов элементов И первой и второй групп попарно соединены между собой и подключены к группе выходов первого узла памяти, вторая группа входов первой группы элементов И является группой информационных входов блока, вторая группа входов второй группы элементов И подключена к группе выходов второго узлав памяти, группы выходов элементов И первой и второй групп соединены с первой и второй группами входов второй схемы сравнения, выход которой соединен с первым входом первого элемента И и с инверсным входом элемента запрета,

5 прямой вход которого и второй вход первого элемента И подключены к выходу элемента задержки, выход первого элемента И подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с вхо0 дом записи третьего узла памяти, выход элемента запрета соединен с первым входом второго элемента И и с входом записи счетчика адреса, группа информационных входов которого подключена к выходам

5 четвертого узла памяти, первый вход сброса счетчика адреса является входом сброса блока, выход второго элемента ИЛИ соединен со счетным входом счетчика адреса и с входом разрешения первой схемы сравне0 ния, выход которой является выходом блока и соединен с вторым входом сброса счетчика адреса, выход третьего узла памяти соединен с вторым входом второго элемента И, выход которого соединен с вторым входом

5 первого элемента ИЛИ, группа выходов регистра адреса соединена с второй группой информационных входов первой схемы сравнения.

0 3. Анализатор по п. 1, от л и ч а ю щи й- с я тем, что блок управления записью содержит узел памяти, счетчик, два триггера, два элемента И и элемент задержки, причем вход элемента задержки является тактовым

5 входом блока, выход элемента задержки соединен с входом чтения узла памяти, вход записи которого является вторым входом записи блока, соответственно информационные входы узла памяти и счетчика соеди0 нены между собой и образуют группу входов задания условий запуска и останова входов блока, группа адресных входов узла памяти является группой информационных входов блока, выход узла памяти соединен

5 с первыми входами первого и второго элементов И, установочный вход первого триггера является входом запуска блокз, выход первого триггера соединен с вторым входом первого элемента И, выход которого соеди0 нен с вычитающим входом счетчика, вход записи которого является первым входом записи блока, выход заема счетчика соединен с установочным входом второго триггера, вход сброса которого и вход сброса

5 первого триггера образуют вход сброса блока, прямой выход второго триггера является вторым выходом блока, инверсный выход второго триггера соединен с вторым входом второго элемента И, выход которого является первым выходом блока.

Примечание. А, В, иС- элементы эталонной последовательно, представленные двоичном коде.

Фиг. 1

Составитель З.Моисеенко Редактор Л.Пчолинская Техред М.МоргенталКорректор Э.Лончакова

Заказ 4163ТиражПодписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул.Гагарина, 101

Фиг.З

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР по заявке 4608344/24 л | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-01-12—Подача