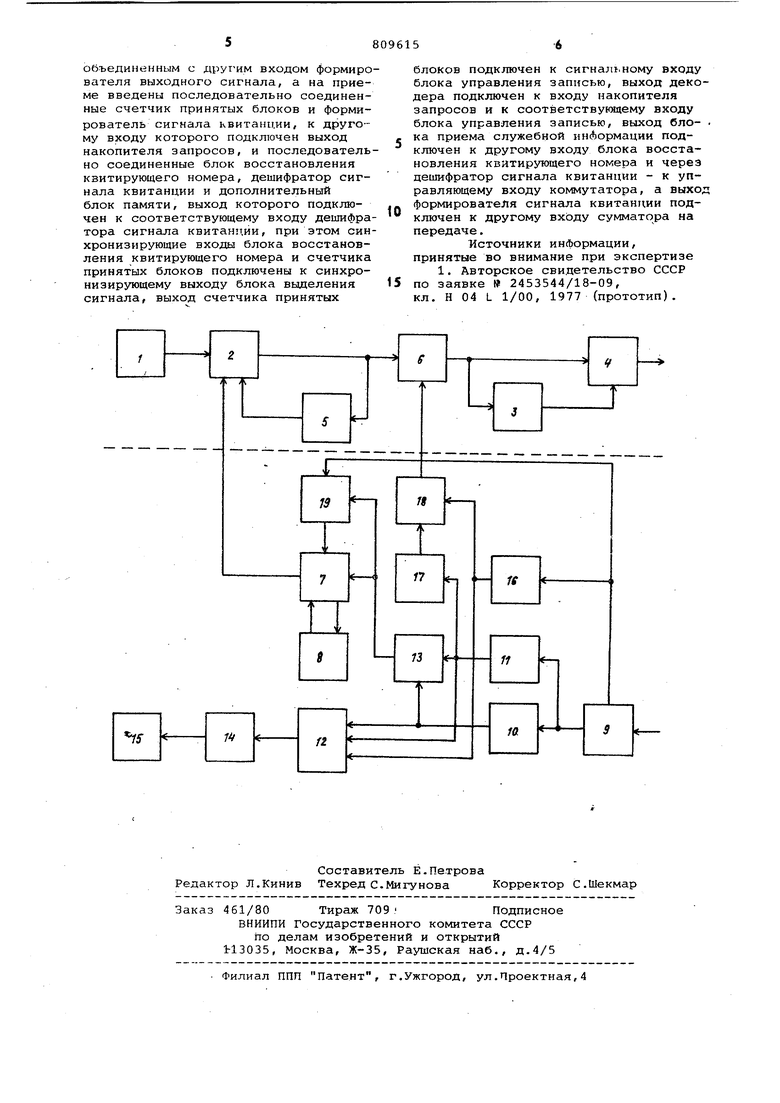

формирователя сигнала квитанции подключен к другому входу сумматора на передаче. На чертеже приведена структурная электрическая схема предлагаемого устройства. Устройство для передачи и приема дискретной информации с коррекцией ошибок содержит на передающей стороне источник 1 информации, коммутатор 2, кодер 3, формирователь 4 выходног сигнала, блок 5 памяти и сумматор 6, на приемной стороне - дешифратор 7 сигнала квитанции, дополнительный блок 8 памяти, блок 9 вьоделения сигнала, входной накопитель 10, декодер 11,блок 12 управления записью, блсЗк приема служебной информации, накопитель 14 приема, потребитель 15, счет чик 16 принятых блoкoвJ накопитель 17 запросов, формирователь 18 сигнала квитанции и блок 19 восстановления квитирующего номера. Устройство работает следующим образом.. На передающей стороне- дискретный сигнал, поступающий от источника 1, разделяется в коммутаторе 2 на блоки каждый из которых дополняется в сумматоре б служебными битами, а в формирователе 4 - выработанными в кодере 3 проверочными битами. Из формиро вателя 4 сигнал поступает через кана связи (не обозначен) на блок 9. Одно временно информационная часть блока записывается в блок 5 на случай повт рения. На приемной стороне принятый Дискретный сигнал через бЛок 9 проходи на вход декодера 11 и входного накопителя 10. В блоке 9 по тому или ино му методу циклового фазирования Формируют последовательность импульсов, отмечающих -границы блоков в принятом сигнале. Эти импульсы через синхрони зирующий выход блока 9 подаются на счётчик 16 и блок 19. В декодере 11 производится проверка принятого блока на наличие в нем Сшибок. БСЛЙ декодер 11 не обнаруживает ошибок в принятом кодовом блоке, то информационная часть блока из входного накопителя 10 через блок .12 переписыв.ается в накопитель 14 на место, определяемое счетчиком 16, и через, некоторое время выдается потреби тетАо -15. Одновременно служебная част блока перезаписывается через блок 13 частично в блок 19 (два младших разряда квитирующего номера) и частично .в дешифратор 7 (биты, сообщающие об обнаружении ошибок на противоположно стороне в данном и пре.дьщу1пем кодовы блоках).В блоке 19 по полученным .дву младшим разрядам квитирующего номера и по сигналам, приходящим от синхронизирующего выхода блока 9, формируется полный квитирующий номер, который , поступает в дешифратор 7. По куаитирующему номеру и битам, содержащим информацию об О1; ибках, дешифратор 7 вырабатывает, сигналы управления коммутатором 2: послать новую информацию или повторить передачу информации, хранящейся в блоке 5. Одновременн.о сигналы управления записываются в дополнительный блок 8 и используются для управлергия коммутатором 2 при передаче следующего блока, если в следующем принятом блоке декодер 11 обнаруживает ошибку. Если декодер 11 обнаруживает ошибку в принятом кодовом блоке, то блок 12 маркирует в накопителе 14 место, номер которого указывается счетчиком 16, для последующего его заполнения при повторной передаче. Блок 13 блокирует перезапись служебной информации из входного накопителя 10 в блок 19 и дешифратор 7. Сигнал об обнаружении или необнаружении ошибок в принятом кодовом . блоке, вырабатываемый декодером 11, поступает также в накопитель 17, где запоминается на время, равное времени передачи одного блока. Из накопителя 17 в формирователь 18 передается информация о наличии ошибок в последнем принятом блоке, а также в блоке, предшествовавшем ему. По этой информации и по номеру последнего принятого блока, поступающему из счетчика 16, формирователь 18 создает квитанцию, которую с помощью сумматора б вставляют в передаваемый сигнал. Предлагаемое устройство позволяет повысить пропускную способность канала без ухудшения достоверности передачи информации за счет сокращения объема передаваемой с каждым блоком служебной информации. Формула изобретения Устройство для передачи и приема дискретной информации с :,дррекцией ошибок, содержащее на передаче последовательно соединенные источник информации, коммутатор и блок памяти, выход которого подключен к другому информационному входу коммутатора, и последовательно соединенные кодер и формирователь выходного сигнала, а на приеме - последовательно соединенные блок выделения сигнала, входной накопитель, блок управления записью, накопитель приема и потребитель, причем выход блока выделения сигнала через декодер подключен к одному из входов блока приема служебной информации, к другому входу которого подключен выход входного накопителя, отличающееся тем, что, с целью повышения пропускной способности канала, на передаче введен сумматор, включенный между выходом коммутатора и входом кодера,

объединенным с другим входом формирователя выходного сигнала, а на приеме введены последовательно соединенные счетчик принятых блоков и формирователь сигнала квитанции, к другому входу которого подключен выход накопителя запросов, и последовательно соединенные блок восстановления квитирующего номера, дешифратор сигнала квитанции и дополнительный блок памяти, выход которого подключен к соответствующему входу дешифратора сигнала квитанп.ии, при этом синхронизирующие входы блока восстановления квитирующего номера и счетчика принятых блоков подключены к синхронизирующему выходу блока выделения сигнала, выход счетчика принятых

блоков подключен к сигнальному входу блока управления записью, выход декодера подключен к входу накопителя запросов и к соответствуквдему входу блока управления записью, выход блока приема служебной информации подключен к другому входу блока восстановления квитирующего номера и через дешифратор сигнала квитанции - к управляющему входу коммутатора, а выхо формирователя сигнала квитанции подключен к другому входу сумматора на передаче.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке 2453544/18-09, кл. Н 04 L 1/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1988 |

|

SU1578825A2 |

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1984 |

|

SU1197114A1 |

| Устройство для передачи и приема дискретной информации с коррекцией | 1978 |

|

SU698149A1 |

| Устройство статистического кодирования и декодирования факсимильных сигналов | 1981 |

|

SU1040623A1 |

| Устройство передачи и приема дискретной информации | 1989 |

|

SU1646066A1 |

| СПОСОБ ПЕРЕДАЧИ СООБЩЕНИЙ В ПОЛУДУПЛЕКСНОМ КАНАЛЕ СВЯЗИ | 1996 |

|

RU2127953C1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1978 |

|

SU767993A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство кодирования и декодирования факсимильных сигналов | 1980 |

|

SU1043834A1 |

Авторы

Даты

1981-02-28—Публикация

1979-04-27—Подача