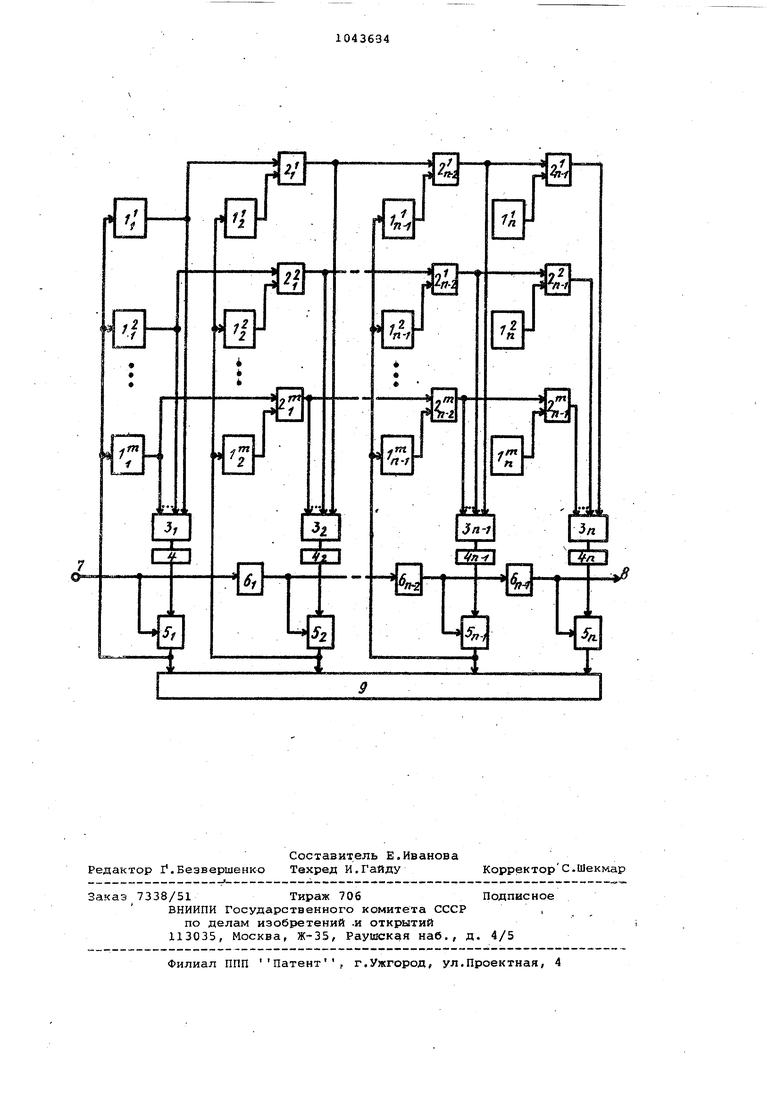

Изобретение относится к автомати ке и вычислительной технике, в част ности к устройствам сортировки чисе и предназначено, например, для элек |ронной цифровой вычислительной сист мы, выполненной на узлах с большой степенью интеграции.; Известно устройство для сравнения двоичных чисел , содержавшее связанные соответствующим образом п двоичных вычитающих счетчика, два реверсивных счетчика,, триггеры, схемы И и ИЛИ и дифференцирующие цепи 1. Недостатками данного устройства являются его сложность и применение значительного числа элементов памяти что в целом, не позволяет создать регулярную структуру с большой степенью интеграции. Известно также устройство для определения максимального из группы чисел, содержащее связанные соответствующим образом регистры чисел, группы элементов И, элементы ИЛИ, регистр результата, группы выходных элементов И, элементы ИЛИ и И, элементы НЕ, выходные элементы И, управ ляющий регистр, управляющие элементы И, управлйкнций элемент ИЛИ, элемент ИЛИ-НЕ, задающие элементы И и элементы залержки 2. Наиболее близким к изобретению по технической сущности и достигаемому эффекту является устройство для выделения максимального числа из hi двоичных чисел, содержащее m груп элементов И, m групп элементов памяти, m групп элементов ИЛИ, многовходовые элементы ИЛИ, управляющие элементы И, регистр результата, элементы Зсщержки, причем вход управления началом работы устройства соедииен с первым входом первого управляю щего элемента И и входом первого эле мента задержки, выход каждого i -го элемента задержки (,2,, .., П -1) ;1 П - количество сравниваемых чисел) подключен к первому входу (i+l)-ro управляющего элемента И и входу {1+1)-го элемента задержки, выход (п-;1)-го элемента задержки соединен с выходной шиной устройства, выход каждого j -го управляющего элемента (, 2,..., п) подключен к информационному входу ) -го разряда регистра результата, инверсный выход каждого первого элемента памяти К-й группы (, 2,..., m ) соединен с первым входом первого элемента и К-й группы, выход каждого из которых под ключен к входу установки внулевое состояние второго элемента памяти К-й группы, выход каждого Р-го элемента ИЛИ -каждой К--й группы (, 2, ,,., П -2) соединен с первым входом (Р+1) элемента ИЛИ К-й группы, инверсный выход каждого 6 -го элемента памяти К-й группы (, 3,.,., п-1) подключен к первому входу Р -го элемента И К-й группы, выход которого подключен к второму входу (-1)-го элемрнта ИЛИ К-й группы, прямой выход каждого i-го элемента памяти К-й группы соединен с К-м входом 1-го многовходового элемента ИЛИ, выход каждого из которых подключен к второму входу i-го управляющего элемента И, выход каждого -го управляющего элемента И соединен с вторыми входами ( -X элементов И всех групп13. Недостатком известных устройств является их сложность. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройство для выделения максимального числа, содержащее (1 групп элементов И, гп групп элементов Пс1МЯти, где щ число сравниваемых двоичных чисел, элементы ИЛИ, управляющие элементы И, регистр результата и элементы задержки, причем вход управления началом работы устройства соединен с первым входом первого управляющего элемента И и входом первого элемента задержки, выход i -го элемента задержк.и (, 2, ..., П -2) ; Ц -количество разрядов сравниваемых чисел) подключен к первому входу (п+1)-го управлякицего элемента И и входу (i -И)-го элемента задержки, выход (П-1)-го элемента задержки соединен с лвыходной шиной устройства, прямой выход первого элемента памяти К-й группы (где , 2,..., IT) соединен с К-м входом первого элемента ИЛИ, введены элементы НЕ, причем вход j-го элемента НЕ (где j 1, 2/...,П ) соединён с выходом j -го элемента ИЛИ, а выход подключен к второму входу -го управляющего элемента И, выход которого подключен к входу установки в нуль j -го разряда регистра результата и входам установки в единичное состояние j -X элементов памяти всех.групп, выход первого элемента памяти К-й группы соединен с первЕЛм входом первого элемента И той же группы, выход 6-го элемента И К-й группы ( где В 1, 2, . ., (П-2) ) подключен к первому входу (Е+1)-го эле- ; мента И той же группы, второй вход Р-го элемента И К-й группы где Р 1, 2..., ( -1) соединен с выходом (P-fl)-ro элемента памяти той же группы, выход Р-го элемента И К-Й группы соединен с К-м Входом ()-го элемента ИЛИ. На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит m групп элементов-1, , 1 , ...„, , l|,... 1., ..., , Ij ,. . . и 1 псиляти, m групп элементов И 21, 2Л..., 2, 2, 2, у1oh о) о П) мыт-, ti-i у t «п-1 MHO говходовые элементы ИЛИ 3( , Зг , . . . . 1 3() , элементы НЕ 4 , 42,..., , управляющие элементы И 5 , 5 , , .. , 5г) элементы 6, бг{ ,. . . , 6f задержки, вход 7 управления началом работы, выходную шину 8 и регистр 9 результа та. Выходы всех элементов Ij , 1; ... , 1 у. памяти подключены к первым элемента ИЛИ 3 входам многовходового i памяти 1 (где выход каждого элемента памяти 1 (где 8 2, .3,. .. , П ; , 2,. .. , hi) связан с вторым входом элемента И 2°, первый .вход элемента И 2 (где , 2, ....f (п-2)) подключен к первому входу элемента И 2. Кроме того, выход каждого элемента И 2|(где 1, 2,... (h-1) ) связан сК-м входом многовходового элемента ИЛИ 3j. Выход каждб го многовходового элемента ИЛИ 3j (гд 1, 2,...,П ) подсоединен через эле мент НЕ 4 , 4,.. ,, 4п ) к входу упра лякхцего элемента И 5 , первый вход управляющего элемента И 5{ , соединен с входом каждого элемента задержки 6{.|. Вход 7 управления началом работы связан с первым входом элемента И 5; и входом первого из последовательно соединенных элементов задержки 6/, 6,..., 6fl.,, выход последнего соедцнен с выходной шиной устройства 8. выход каждого управляющего элемента И 5j подключен к входу установки в единичное состояние элементов памяти l| , 1,- ,... , 1 7 и входу установки в нуль i -го разряда регистра 9 per зультата. Устройство работает следующим образом. tlepe начале работы все разряды регистра 9 устанавливаются в единичное состояние. В элементы 1 памяти заносится Ш п -разрядных чисел. По сигналу начала операции, который пос тупает на вход 7, разрешается обработка сигналов с выхода элементов памяти l| , 1,..., в которых записаны старшие разряды чисел - если .на одном из упомянутых элементов памяти записана хотя бы одна единица, на выходе многовходового элемента ИЛИ 3 и соответствующего элемента НЕ 4 формируется сигнал нулевого уровня а с выхода элемента И 5f снимается также сигнал нулевого уровня и, таким образом, первый разряд регистра 9 остается в единичном состоянии. С выходов элементов памяти 1, 1,..., ij, в которых записан нуль, снимается сигнсш нулевого уровни, который, поступая на соответствующие элементы И , 2 ,. .,, 2 Ij, исключает дальнейшее участие чисел, в старшем разряде которых записан нуль, в последующих тактах сравнения. В случае, если в старших разрядах всех сравниваемьЬс чисел записаны нули, элементами ИЛИ 3, НЕ 4 и И 5 последовательно формируются сигналы единичного уровня и старший разряд регистра 9. результата сбрасывается в нуль, а элементы па.1 1 ,т мяти 1, устанавливаются в единичное состояние, разрешая анализ в последующем такте работы устройства содержимого всех элементов памяти Ij, l|,..,, 1. При появлении сигнала на выходе элемента б/ задержки производится анализ содержимого элементов памяти Uj, 1 ,.,., i, . не (исключенных на предыдущем такте работы устройства. Если на указанных элементах памяти записана хотя бы одна единица, элементами ИЛИ З., НЕ 4( и И Bg последовательно формируются сигналы нулевого уровня - во втором разряде регистра 9 результата остается записайной единица, а с выходов элементов памяти 1 , Ij,... 1 в которых записан нуль, снимается сигнал нулевого уровня, который, поступая на входы соответствующих элементов И 2 , 2 , . .. , 2 , исключает соответствующие числа из процесса сравнения на последующих тактах работы. Если на не исключенных на первом такте элементах памяти 1 , ./ 1 записанывсе нули, сигнал единичного уровня последовательно формируется на выходах элементов ИЛИ 32 НЕ 4 к И 52 . Сигналом с выхода элемента И 5,-второй разряд регистра 9 результата устанавливается в нуль, а элементы памяти ll , 1, . . . , 12 устанавливают, а элементы памяти 1, l| , ся в ч нуль ..., Ij устанавливаются в единицу, т.е. во втором такте, таким образом, не исключается ни одно число из дальнейших тактов сравнения. Аналогичным образом, последовательно во времени анализируются остальные разряды сравниваемых чисел. При выдаче единичного сигнала с выхода элемента 6п-4 задержки на выходную шину 8 устройства на регистре 9 результата фиксируется код максимального числа. Изобретение позволяет упростить структуру устройства по сравнению с известным за счет сокращения количества логических элементов, используемых в устройстве, . В известном устройстве число логических элементов. С,.2п4.тИп-3), ) а в предлагаемом С., 2п4-т (n-i). (2). Таким образом, в среднем число логических элементов в предлагаемом устройстве на 45% меньше, чем в известном.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения максимального из @ чисел | 1981 |

|

SU999041A1 |

| Устройство для определения максимального числа из группы чисел | 1980 |

|

SU959065A1 |

| Устройство для выделения максимального числа | 1989 |

|

SU1697076A1 |

| Устройство для поиска максимального числа | 1985 |

|

SU1314334A1 |

| Устройство для выделения максимального числа | 1982 |

|

SU1024902A1 |

| Устройство для определения максимального из @ -двоичных чисел | 1983 |

|

SU1173408A1 |

| Устройство для определения экстремального числа | 1980 |

|

SU962920A1 |

| Устройство для определения максимального из т двоичных чисел | 1980 |

|

SU875376A1 |

| Устройство для выделения среднего из нечетного количества чисел | 1988 |

|

SU1647554A1 |

| Устройство для сравнения @ @ -разрядных двоичных чисел | 1981 |

|

SU983703A1 |

УСТРОЙСТВО ДЛЯ ВЬЩЕЛЕНИЯ МАКСИМАЛЬНОГО ЧИСЛА, содержшцее (л . групп элементов И, m групп элементов памяти, где m - число сравниваемых двоичных, чисел, элементы ИЛИ, управляющие элементы И, регистр результата и элементы задержки, причем Вход управления началом работы устройства соединен с первым входом первого управляющего элемента И. и входом первого элемента задержки, выход г -го элемента задержки (где i 1, 2..., (п-2)J м - количество разрядов сравниваемых чисел) подключен к первому входу ( +1)-го управляющего элемента И и входу (+1)-го элемента задержки, выход (n-l).-ro элемента задержки соединен с выходной шиной устройства, прямой выход первого элемента памяти К-и группы (где k 1, 2,...,m) соединен с k-м входом первого элемента ИЛИ, о тличающе е с я тем, что, с целью упрощения устройства, в негр введены элементы НЕ, причем вход ) -го элемента НЕ (где , 2, ..., Ч) соединен с выходом j-го элемента ИЛИ, а выход подключен к второму входу j-го управляющего элемента И, выход которого подключен к входу установки в нуль j-го разряда регистра результата и входам установки в единичное состояние j-х элементов па(Л мяти всех групп, выход первого элемента памяти k-и группы соединен с с первым входом первого элемента И той же группы, выход 8 -го элемента И k-й группы (где 1, 2,..., (h-2) подключен к первому входу (-И)-го элемента И той же группы, второй вход р-го элемента И k-й группы (где , 2,...,

| I | |||

| Устройство для сравнения двоичных чисел | 1972 |

|

SU444180A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-23—Публикация

1982-06-29—Подача