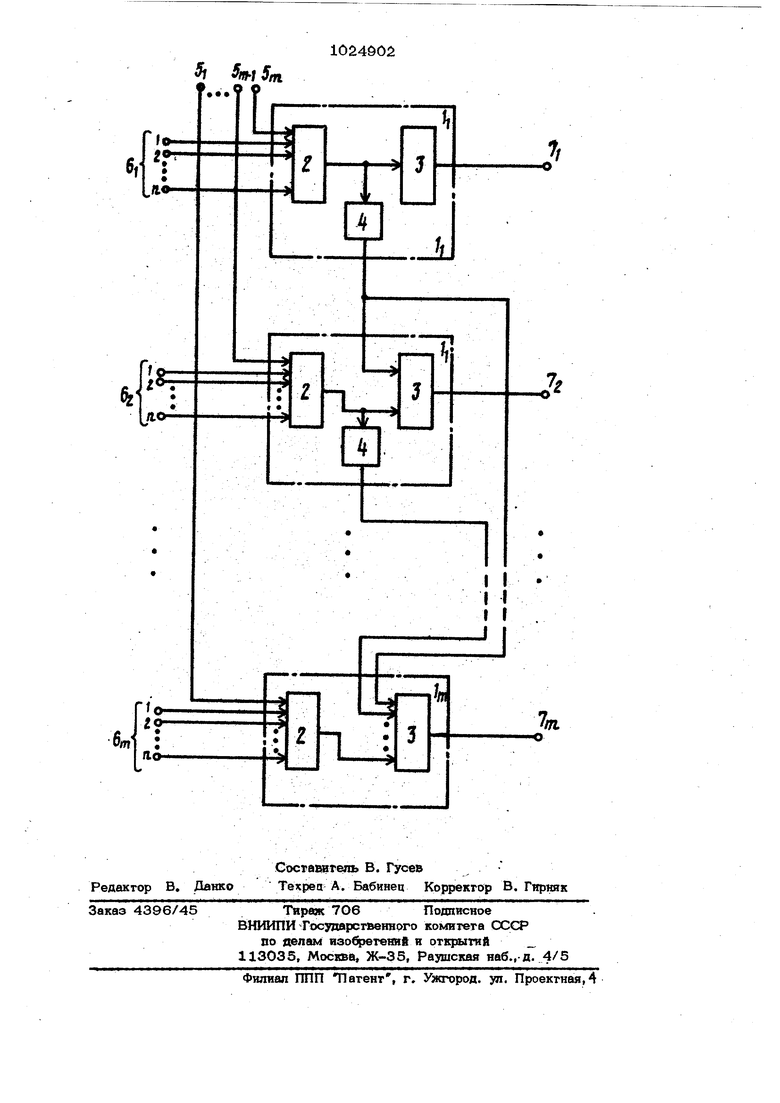

Изобретение относится к технической кибернетике и может быть использовано для построения технических средств систем классификации, распознавания образов, поиска информации и автоматизании принятия решений в не четких условиях. Устройство предназначено для реализации операций дизъюнкции и имшшкаиии над нечеткими,; переменными (высказьгоаниями) в нечеткой логике Л.Заде, где результат С операции дизъюнкции Vi нечетких переменных (i 1,2 ... , VI ) вычисляется по формуле С г.уу) , а результат 3) операции импликации- двух нечетких переменных А и Bi вьгчисляется по формуле . D vYiO( 1-А, В; ). Здесь А.В ( 1 1,2,.-. , И ), С, Т) - числа из ин тервала О, Ij , представленные jyi-разрядным унитарным кодом ( один из w ) Известен распределитель сигналов, позволяющий выделять левую единицу из v -разрядного двоичного кода, содер жащий вьтолненные на триггерах вспомогательный регистр, основной регистр . однотипные ячейки, каждая из которых содержит элемент ИЛИ и два элемента И. Выделение левой единицы происходит за два такта f 1J . Недостатком известного устройства является низкое б 1стродействие, сложность и то, что оно не выделяет макси мального из И чисел, представленных унитарным кодом. Наиболее близки и к изобретению является устройство для определения макс мального из m двоичных чисел, содержащее Vvi грушт элементов И, YYI групп элементов памяти, уг групп элементов ИЛИ, многовходовые элементы ИЛИ, уп равляющие элементы И, регистр результата, элементы задержки, причем вход упрбюления началом работы устройства соединен с первьшс входом первого эп& та. задержки, выход каждого i -го элем та задержки, где i 1,2,,.,. , ( ц - 1 VI - количество разрядов сравниваемых сел, соединен с первым входом {i+f )управляющего элемента И и с вхо + 1)-го элемента задержки, выход ( и - 1) -го элемента задержки соединен с вькоциой шиной устройства, вы ход каждого j -го управляющего элемен та И, где j 1,2, ... , и , соединен информационным входом j нгю разряда регистра результата, инверсный выход каждого первогю элемента памяти к-й Группы, где к в 1,2, ,. , 1, соединен с первым входом первого элемента И к-Л грухшы, выход каждого из которых соединен с входом установки в нулевое состояние второго элемента памяти к-й группы и с первым входом первого элемента ИЛИ к-й группы, выход каждого р ) элемента ИЛИ каждой к-й группы, где р « 1,2,,.. , ( VI - 2), соединен с первым входом ( р + 1 )нто элемента ИЛИ к-й группы, инверсный выход каждого 8-го элемента памяти к-й группы, где 8 2,3, ..., { и-. 1) соединен с первым входом g-го элемента И к-й группы, выход которого соединен с вторым входом (е- 1)-го элемента ИЛИ к-й группы, прямой выход каждого ; -го : элемента памяти к-й группы, соединен с к-м входом 1 -го многовходового элемента ИЛИ, выход каждого из которых соединен с вторым входом i-го управляю шего элемента И, выход каждого i -го управл$пощего элемента И соединен с вторыми входами i -X элементов И всех групп 2 .1 Недостатлом устройства является его сложность, и низкое быстродействие. Целью изобретения является упрошение устройства и повышение его быстродействия. Поставленная цель достигается тем, что устройство для выделения максимального числа, содержащее элементы И, ИЛИ, причем вхогма i -го элемента ИЛИ соединены с входами f -х разрядов сравниваемых чисел ( i 1, ..„ v,, где W- число разрядов срамиваемых чисел), а выход соединен с пер вым входом 1 -го элемента И, содержит элементы НЕ, причем j- вход j -го элемента И соединен с выходом ( J- 1)-го элемейта НЕ, где 2,Л. ... I W1 г вход к-гч элемента НЕ соединен с выходом кчго элемента ИЛИ, где к в 1, .. , w- 1, выходы элементов И Являются выходами устройства. На чертеже приставлена блок-схема устройства. Устройство состоит из W поразрядных узлов анализа 1, ... , 1, содержащих элементы ИЛЙ2, ИЗ и НЕ4 ( узле элемент НЕ отсутствует), групйы 1ШШ 5 I 5- ,.,. ,5 для подачи первого числа,П групп , 62, .,., 6 по и шин в каждой для додачи соответственно 1нсч), 2-го, ч t.. , т -го разряда каждого из и остальных чисел, выходных шин 7л Назначение каждого из УМ поразрядных узлов анализа состоит в выполненки дизъюнкции соответствующих разрядов унитарных кодов чисел, поданных на вход элемента ИЛИ, в выделении единицы соответствующего разряда и выработке сиг нала для блокировки элементов И младших узлов анализа. Возрастание индексации на чертеже соотеетствует упорядоченности от старших разрядов к младщим. Вьгаисление дизъюнкции v нечетких переменных состоит 6 выполн1енин поразрядной, дизъюнкции унитарных кодов этих чисел и в последующем выделении из йолученного кода старшей единицы. Вычисление результата 3) импликации двух нечетких переменных А и В состоит в получении разности {1-А) иначэжеении аизъюнкцни чисел (1-А), в указанном порядке. В устройстве значение разности 1-А образуется за счет инверсного порядка подключения шин разрядов числа А к первым входам элементов ИЛИ поразрядных узлов анализа. Тем самым вместо кода числа А фактически подаетсякод числа 1-А. Устройство работает следующим образом При вычислении операшш дизъюнкции нечетких переменных тш шины 5 подаю ся нулевые сигналы. Щ оганы 6 подаютс .уни-гарные коды М чисел В , B,j, .,. ,B Если требуется вылопнать двзъюнк цвю меньшего числа нечетких переменных то на иганы остальных переменных подаются нулевые сигналы. На выходах элементов ИЛИ2 поразрядных узлов анализа образуется код, представляющий собой поразрядную дизгьюшшию кодов чисел В , В,..,., В . Пусть в этом коде старшая единица находится в -м разряде. Тогда единичный сигнал с выхода элемента ИЛИ 2 /i -го узла анализа проходит на выход элемента И 3,так как на остальные входы этенгю элемента с выходов элементов НЕ 4 всех старших узлов анализа подаются единичные сигналы. Нулевой сигнал сВыхода элемента НЕ 4 i -го узла запрещает прохождение единичного сигнала на выходы элементов И 3 всех мпашиих поразрядных узлов анализа. Таким образом, на выходных шинах 7 формируется унитарнь1й код максимального из чисел В В, .... , В„ . При вычислении операции импликации двух нечетких переменных А и на Л шины 5 подается унитарный код числа А. П{ж этом на первых входах элементов ИЛИ 2 о азуется унитарный коц числа 1-А. - . Так как результат рпервиии импликации определяется как дизьюякпвя чисел (1-А) и В , то, подав чнсйЪ на входы 6 указанным , на выходах 7 устройства получим увнта ый код результата операции импликации чисел А и В . Таким образом, предлагаемое изо()етеяие позволяет упростить устройство за счет сокращения количества логических элементов и повыснзъ быстродействие устройства.,

15,

/л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения экстремального числа | 1983 |

|

SU1108437A1 |

| Устройство для выделения экстремального числа | 1984 |

|

SU1156060A1 |

| Устройство для выделения максимального числа | 1986 |

|

SU1345188A1 |

| Устройство для анализа нечетких данных | 1989 |

|

SU1683004A1 |

| Устройство для сравнения чисел | 1986 |

|

SU1376079A1 |

| Устройство для обработки нечеткой информации | 1989 |

|

SU1619252A1 |

| Устройство для обработки логической информации | 1987 |

|

SU1446616A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ | 1992 |

|

RU2042186C1 |

| Устройство для определения максимального числа | 1987 |

|

SU1449984A1 |

| Устройство для вычитания | 1989 |

|

SU1654813A1 |

УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ МАКСИМАЛЬНОГО ЧИСЛА, содержащее элементы И, ИЛИ, причем вхопы -i -пз элемента ИЛИ соед11нены с входами 1 чых разрядов сравниваемьсс чисел (i I,..,. , w, где vn- число разрядов сравниваемксх чисел), а выход соединен с. первым входом i .«го элемента И, отличаюше ее я тем, что, с целью упрощения устройства и повышения быстродействия, устройство содержит элементы НЕ, првяем j -ый вход j -4ч э;1 емента И соединен с BXiiходом ( J- 1) -го элемента НЕ, где j 2, ,.., т , вкоа к-го элемента НЕ соепинен с выходом к-го элемента ИЛИ, где к 1,1.. , W- 1, выходы элементов И являюггся выходами устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Распределитель сигналов | 1973 |

|

SU475616A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для определения максимального из т двоичных чисел | 1980 |

|

SU875376A1 |

Авторы

Даты

1983-06-23—Публикация

1982-02-17—Подача