вых импульсов, счетчика и блока постоянной памяти, причем выход генератвра тактовых импульсов подключен к входу счетчика, выход счетчика подключен к адресному входу блока постоянной памяти,выходы блока постоянной памяти являются выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления - точечного преобразования фурье | 1978 |

|

SU746539A1 |

| Устройство для вычисления коэффициентов фурье | 1977 |

|

SU717780A1 |

| Устройство для вычисления коэффициентов фурье | 1976 |

|

SU643889A1 |

| Анализатор спектра Фурье | 1984 |

|

SU1226486A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

1.УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ ФУРЬЕ, содержа-г щее аналого-цифровой преобразователь, арифметический блок, состоящий из двух арифметических узлов, блок памяти коэффициентов, первый коммутатор, первый и второй блоки сдвига, каждый из которых состоит из четы- рех узлов сдвига, и блок управления, причем информационный вход аналогоцифрового преобразователя является информационным входом устройства, а.выход подключен к первому информационному входу первого коммутатора, вьоход блока памяти коэффициен-тов подключен к входам коэффициентов арифметических узлов арифметического блока, выходы которых подключены к второму и третьему информационным .входам первого коммутатора, выходы первого, второго и третьего узлов сдвига .в каждом блоке сдвига подключены к информационнымвходам второго, третьего и четвертого узлов сдвига соответственно, информационные, входы первых и третьих узлов сдвига в каждом блоке сдвига подключены к соответствующим выходам первого коммтутатора, адресные входы блока памяти коэффягциентов, а также управляющие входы аналого-цифрового преобразователя, арифметических узлов в арифметическом блоке, первогокоммутатора и узлов сдвига в первом и втором блоках сдвига подключены к соответствующим выходам 6ЛОК4 управления, отличающееся тем, что, с целью повьшения быстродействия устройства, оно содержит второй коммутатор и третий блок сдвига, состоящий из четырех узлов сдвига, причем выходы первого, второго и третьего узлов сдвига в третьем блоке сдвига подключены к информационным входам второго, третьего .и четвертого -узлов сдвига соответственно, информационные входы первого и тре- тьего узлов сдвига в третьем блоке сдвига подключены к соответствующим С выходам первого коммутатора, выходы первых, вторых,, третьих и четвертых узлов сдвига в каждом блоке сдвига подключены соответственно к первой, второй, третьей и четвертой группам входов второго коммутатора, первый выход второго коммутатора подключен 4 00 к входам первых операндов арифметических узлов в арифметическом блоке, второй выход второго коммутатора пода ключен к входам вторых операндов арифметических узлов в арифметическом да блоке, третий и четвертый выходы второго коммутатора подключены к входам треTjbего операнда соответст;венно первого и второго арифметических узлов в арифметическом бло-лке, управляющие входы второго коммутатора и узлов сдвига в третьемблоке сдвига подключены к соответствующим выходам блока управления, выход четвертого узла сдвига в третьем блоке сдвига является выходом устройства. 2, Устройство по п.1, отличающееся тем, что блок управления состоит из генератора такте

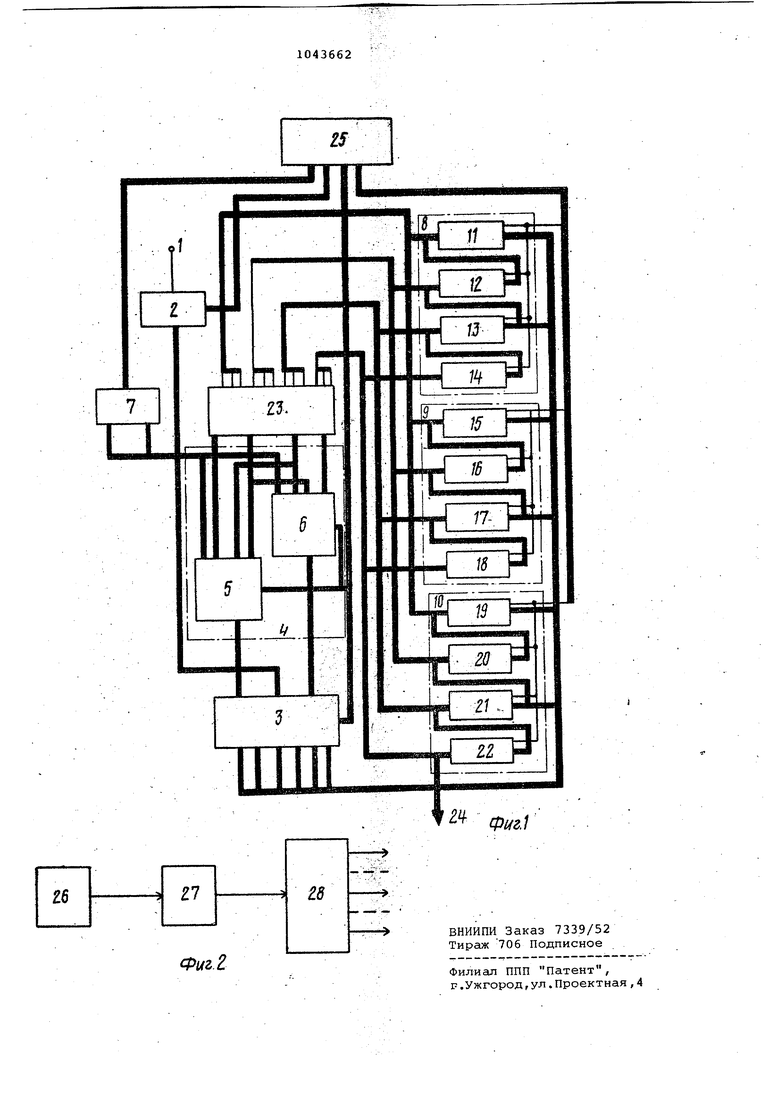

Изобретение относится к автома и- вычислительной технике и может б использовано в системах обработки сигналов цифровыми методами, системах диагностики, а также в систе автоматического управления. Известно устройство для вычисления коэффициентов Фурье, содержащее две группы аналоговых сдвигающих регистров и переключателей коммутационные панели, счетчикии блоки операционных усилителей tl2 Недостатками этого устройства являются низкая точность, ограниченные функциональные возможности а также сравнительно большая сложность и низкая надежность. Наиболее близким по техническому решению к изобретению является устройство для вычисления коэффициентов Фурье, содержащее аналогоцифровой преобразователь, коммутатор, арифметический блок, состоящий из двух арифметических узлов, блок памяти коэффициентов, первый и второй блоки сдвига, каждый из которых состоит из четырех узлов сдвига, и блок управления f 2 J. Недостатком известного устройства для вычисления коэффициентов Фурье является низкое быстродейств и, -как следствие, узкий частотный диапазон входного сигнала, посколь ку анализируемые данные поступают через аналого-цифровой преобразова тель на блок буферных регистров, в котором накапливается входная информация. После окончания текущей реализации входного сигнала информация переписывается в первый блок сдвига. Подобная организация устро ства требует значительных затрат времени на перезапись информации, так как при больших объемах выборки запись из одного блока сдвига другой может быть организована тол ко в последовательном режиме. В противном случае требуются значительные аппаратурные затраты. Цель изобретения - повышение быстродействия устройства, Поставленная цель достигается т что устройство для вычисления коэф фициен,тов Фурье, содержащее аналог цифровой преобразователь, арифмети ческий блок, состоящий из двух арифметических узлоч, блок памяти коэффициентов, первый коммутатор, первый и второй блоки сдвига, каждый из которых состоит из четырех узлов сдвига, и блок управления, причем информационный вход аналого-цифрового преобразователя является информационным входом устройства, а выход подключен к первому информационному входу первого коммутатора, выход блока памяти коэффициентов подключен ко входам коэффициентов арифметических узлов арифметического блока, выходы которых подключены ко второму и третьему информационным входам первого коммутатора, выходы первого, второго и третьего узлов сдвига в каждом блоке сдвига подключены к информационным входам второго, третьего и четвертого узлов сдвига соответственно, информационные входы первых и третьих узлов сдвига в каждом блоке сдвига подключены к соответствующим выходам первого коммутатора, адресные входы блока памяти коэффициентов, а также управляющие входы аналогоцифрового преобразователя, арифметических узлов в арифметическом блоке, первого коммутатора и узлов сдвига в первом и втором блоках сдвига подключены к соответствующим выходам блока -управления, содержит второй коммутатор и третий блок сдвига, состоящий из четырех узлов сдвига, причем выходы первого, второго и третьего узлов сдвига в третьем блоке сдвига подключены к информационным входам второго, третьего и четвертого узлов сдвига соответственно, информационные входы первого и третьего узлов сдвига в третьем- блоке сдвига подключены к соответствующим выходам первого коммутатора,выходы первых, вторых, третьих и четвертых,узлов сдвига в каждом блоке сдвига подключены соответственно к первой, второй, третьей и четвертой группам входов второго коммутатора, первый выход второго коммутатора подключен ко входам первых операндов арифметических узлов, в арифметическом блоке, второй выход второго коммутатора подключен ко входам вторых операндов арифметических узлов в арифметическом блоке, третий и четвертый выход второго коммутатора подключены ко входам третьего операнда соответственно первого и второго арифметических узлов в арифметическом блоке , управляющие входы второго комму татора и узлов сдвига в третьем бло ке сдвига подключены к соответствую щим выходам блока управления, вы- ход четвертого -узла сдвига в третьем блоке сдвига является выходом устройства. Кроме того, блок управления состоит из генератора тактовых импульсов, счетчика и блока постоянной па мяти, причем выход генератора такто вых импульсов подключен ко входу счетчика, выход счетчика подключен к адресному входу блока постоянной памяти, выходы блока постоянной памяти являются выходами блока управления.На фиг.1 представлена структурная схема устройства для вычисления коэффициентов Фурье; на фиг.2 структурная схема блока управления Устройство содержит входную шину 1 , аналого-цифровой преобразовав тель 2, коммутатор 3, .арифметический блок 4, состоящий из арифметических узлов 5 и 6, блок 7 памяти ко.эффициентов, блоки 8-10 сдвига, состоящие из узлов 11-22 сдвига, коммутатор 23, выходную шину 24, блок 25 управления. Блок управлени состоит из генератора 26 тактовых импульсов, счетчика 27 и .блока 28 постоянной памяти. Устройство для вычисления коэфф циентов Фурье работает следующим образом. В исходном состоянии блоки 8 и сдвига не содержат информации, тог да как в блоке 9 сдвига в параллел ном коде хранится М отсчетов преды дущей реализации входного сигнала, которая была подана на вход 1 устройства, так что на выходе узла 18 сдвига присутствует нулевой отсчет на выходе узла 17 сдвига - отсчет номером N1/4, на выходе узла 15.сдв га - отсчет с номером 3N/4. Аналого-цифровой преобразовател обеспечивает в моменты поступления на его управляющий вход тактовых импульсов преобразование входного аналогового сигнала, подаваемого на вход 1, в цифровую форму на выходе. Параллельный код отсчетов те щей реализации последовательно -загружается через коммутатор 3 в бло сдвига так, что первый из N отсчетов реализации после N тактов синхронизации занимает выходную позицию узла 14 сдвига, отсчет с номером N/4 занимает выходную позицию в узле 13 сдвига, отсчет с ном ром N/2 занимает выходную позицию в узле 12 сдвига, а отсчет с номером 3N/4 - в узле 11 сдвига. Одновременно с загрузкой текущей реализации вычисляются коэффициенты Фурье для реализации, хранящейся в исходном состоянии в блоке 9 сдвига. Вычисление происходит по алгоритму быстрого преобразования Фурье для вещественных входных сигналов. Согласно этому алгоритму в первом цикле вычислений на входы арифметического блока 4 через коммутатор 23 поступают в параллельном коде отсчеты с номерами О, N/4, N/2 и 3N/4, которые служат для арифметического блока 4 операндамиX о, X , Xj и ХзАрифметический блок выполняет над поступившими операндами следующие действия: Xjj+X2r X +Х j; XQ- К21 -i Х. Результаты указанных действий являются составляющими первого массива частичных сумм при вычислении коэффициентов Фурье. При этом на выходах арифметического блока сначала одновременно формируются числа Хр+Х2 и. X 5, а затем-числа Хо-Х2 и . Вычисленные таким образом значения поступают через коммутатор 3 на входы блока 10 сдвига. Числа Хд+Х и X + Xj одно за другим загружаются в узел 19 сдвига, а числа Xfl-Xj и Х-,-Хз - в узел 21 сдвига. Затем происходит сдвиг информации, и выходные позиции в узлах 1518 сдвига занимают отсчеты обрабатываемой реализации с номерами 1, N/4+1, N/2+1 и 3N/4+1, которые в свою оуередь являются операндами для вычисления следующих значений первого массива частичных сумм, значения которых через коммутатор 3 записываются в блок 10 сдвига, В дальнейшем, вследствие выполнения N/4 аналогичных операций блок 9 сдвига очищается, а блок 10 сдвига оказывается заполненным частичными суммами первого массива. После этого выходы блока 1.0 сдвига через коммутатор 9 подключаются ко входам арифметического блока 4, а результаты вычислений записываются через коммутатор 3 в блок 9 сдвига в качестве второго массива частичных сумм. Затем второй массив обрабатывается аналогичным образом, а результат обработки - третий массив - помещается в свободный блок 10 сдвига. После выполнения операций в блоке 9 сдвига, если tog2N является четным числом, или в блоке 10 сдвига, если 6og2N - нечетное, оказываются записанными коэффициенты Фурье. При этом на соответствующих этапах вычисления арифметический блок может выполнять, кроме указан- , ных действий, и операции вида Хд+Х«-ь

Xp-J-x -F. ,-x,g|

, F.X2/ ,,

x +FpXj;

где F - значения векторов поворота, хранящиеся в блоке 7 памяти коэффициентов и поступающие на первый вход арифмеI тического блока 4, .

быстродействие элементной базы и тактовая частота функционирования арифметического блока выбирается такой, чтобы все итераций по вычислению коэффициентов Фурье выполнялись эа время, меньшее, чем время загрузки текущей реализации в блок 8 сдвига. Поэтому, после окончания последней инерции результаты преобразования Фурье над предьадущей реализацией выводятся из устройства на выход 24 последовательно, число за числом в параллельном .коде. Таким образом блоки 9 и 10 сдвига рчищаются преждеJ чем заканчивается загрузка текущей реализации. После окончания ; текущей реализации еледующая реализация начинает загружаться ВО Бторой блок сдвига, а текущая реализация обрабатывается аналогичны образом, за исключением того, что обмен операндами и результатак вычислений производится между первым и третьим блоками сдвига.

Блок управления работает следующим образом.

Пусть в ис «одиом состоянии блоки 8 и 10 сдвига не содержат, информации, тогда как в блоке 9 сдвига .в параллельном коде хранится N отсчетов предыдущей реализации входного сигнала. Первый и второй коммутаторы 3 и 23 программируются кодами формируемыми на выходах блока 25 управления так, что первый из них подключает выходы арифметических узлов 6 и 5 к входам узлов 19 и 21 сдвига, а второй соединяет выходы узлов 15-18 сдвига с входами арифметического блока 4. Во время первой итерации блок управления формирует на своих выходах импульсы сдвига для блока 8 с частотой аналого-цифрового преобразования. Эти тлпульсы поступают на управляющие входы узлов 11-14 сдвига и иницируют запись входной реализации с выхода аналого-цифрового преобразователя 2 через первый кокшутатор 3 в блок 8 сдвига по входу узла11 сдвнга. Одновременно подаются импульсы сдвига на блоки 9 и 10 сдвига, приче частота синхронизации блока 9, из которого считЕйваются по четыре операнда за каждый такт по выходам узлов 15-18 сдвига через второй коммутатор 23 в арифметический блок 4, в два раза меньше частрты сдвига в блоке 10, в который; результаты промежуточных вычислений записываются попарно из арифметических узлов 5 и 6 через первый коммутатор 3, Арифметические узлы 5 и 6 настраиваются кодами, поступающими на их управляющие входы, на те операции, которые необходимо выполнить в течение первой итерации.. При этом контакты для выполнения операции умножения на коэффициент поступают в арифметический блок 4 из блока 7 памяти коэффициентов, адресуемого по группе, выходов блока 6 управления.

Такой порядок работы сохраняется до тех пор, пока не опорожнится блок 9 сдвига., а блок 10 не заполнится. После этого, коды, управляющие коммутаторами и настраивающие арифметический блок, изменяются так, что к входам арифметического бло- ка 4 подсоединяются выходы узлов 19-22 сдвига, а выходы арифметического блока подключаются к входам блока 9 сдвига. Синхронизирующие импульсы удвоенной частоты начинают поступать уже на вход 9 блока, а на синхронизирующий вход блока 10 импульсы подаются в два раза реже. По окончании второй итерации снова происходит изменение состояния выходов блока управления в соответствии с выбранным алгоритмом. Сигналы, формируемые на управляющих входах аналого-цифрового преобразователя 2, асинхронны по отношению к остальным управляющим сигналам. Последовательность этих импульсов прекращается после заполнения блока 8 сдвига, К этому моменту все итерации уже закончены и результат преобразования выведен во внешнее устройство через выход 24.

Предлагаемая конструкция и порядок .работы устройства для вычисления коэффициентов Фурье позволяет вычислять преобразование Фурье для относительно широкополосных сигналов в реальном масштабе времени, что недостижимо в известном устройстве.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для выполнения быстрого преобразования фурье | 1974 |

|

SU497589A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления - точечного преобразования фурье | 1978 |

|

SU746539A1 |

| Хпрототип) | |||

Авторы

Даты

1983-09-23—Публикация

1981-01-04—Подача