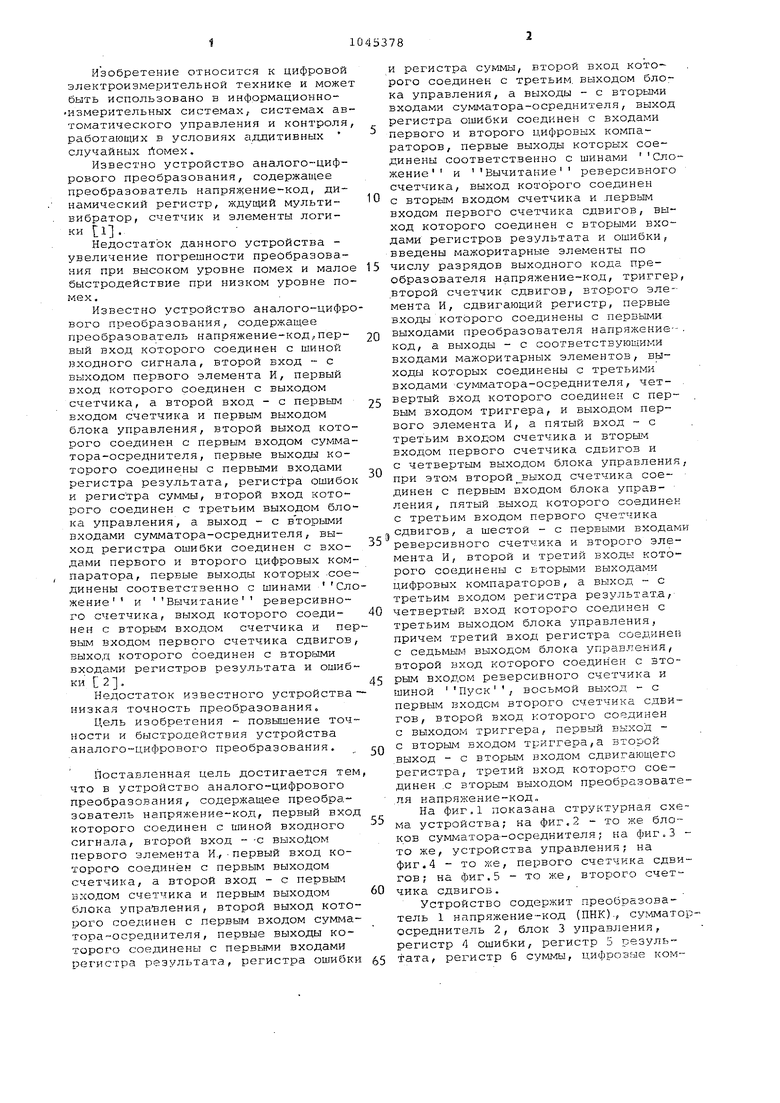

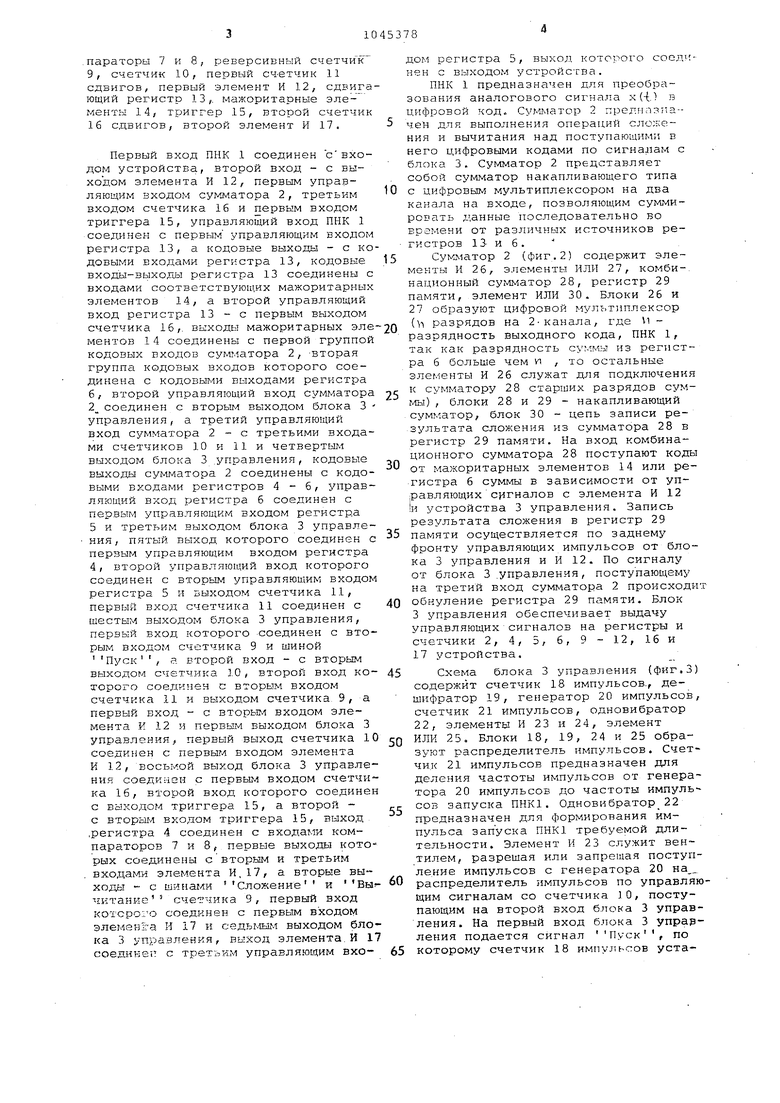

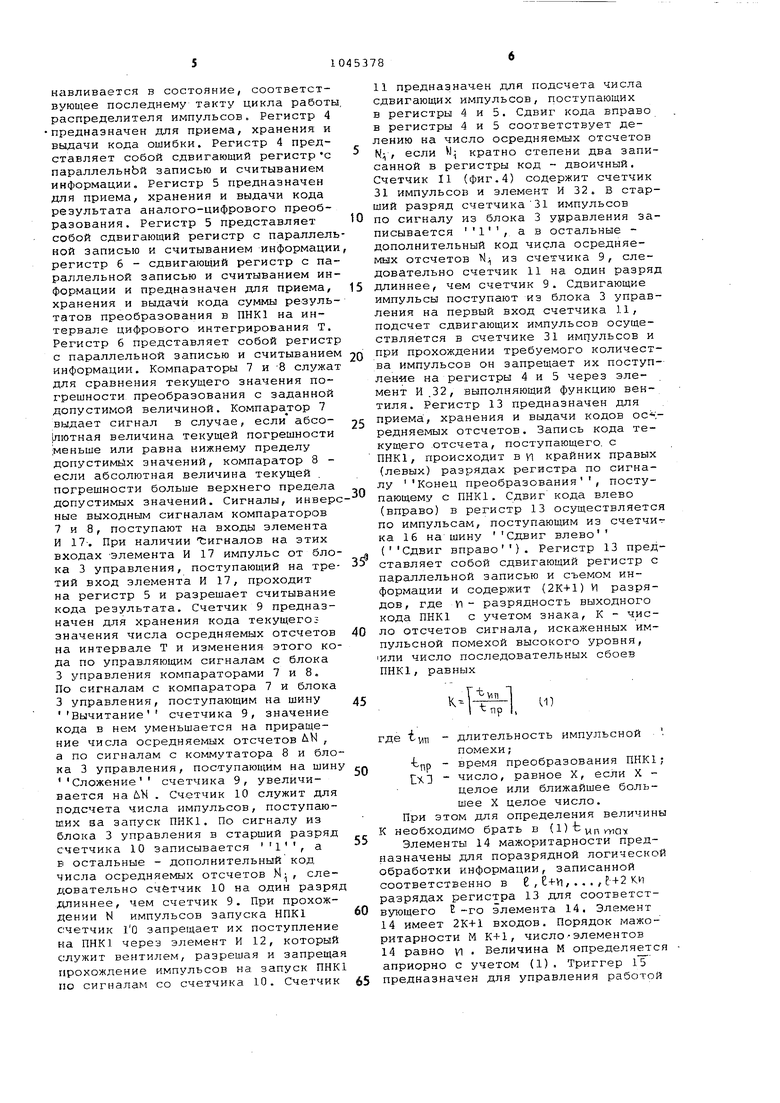

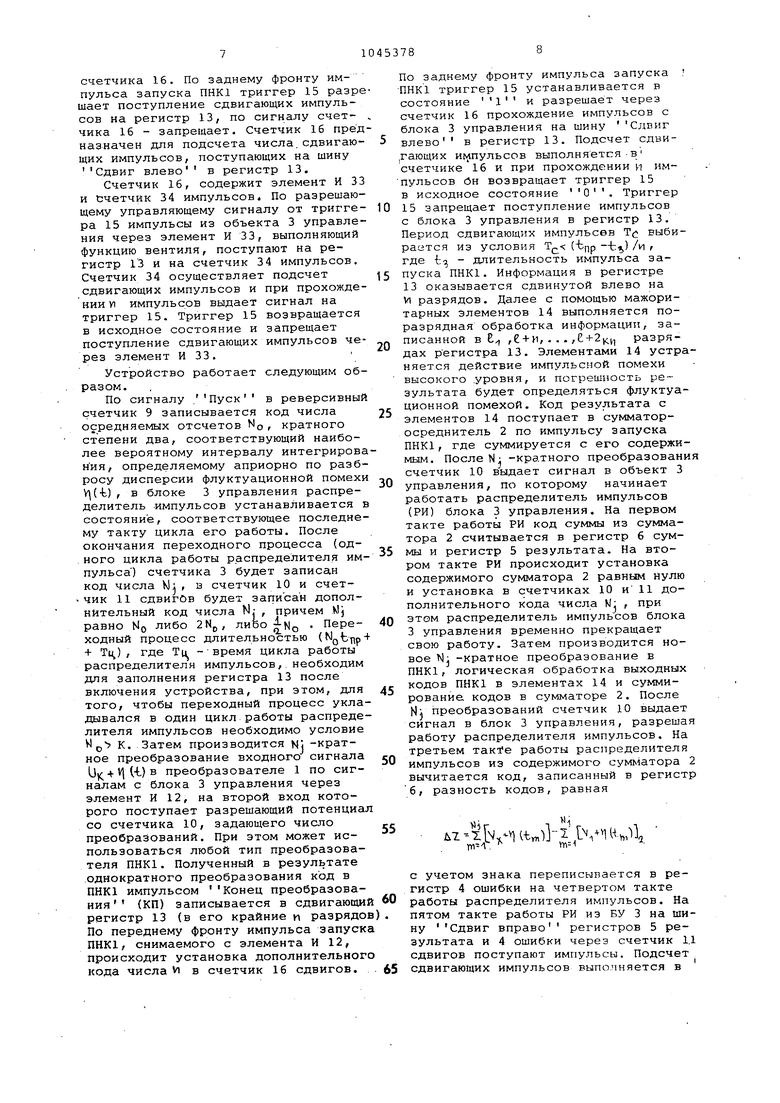

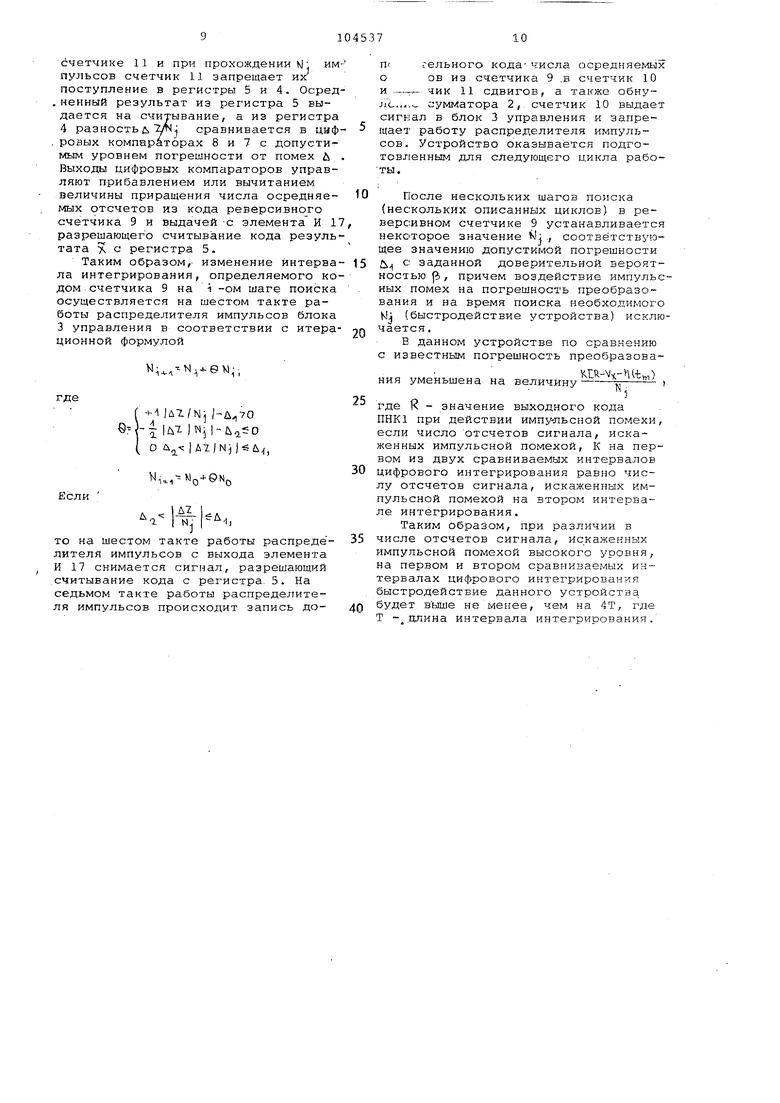

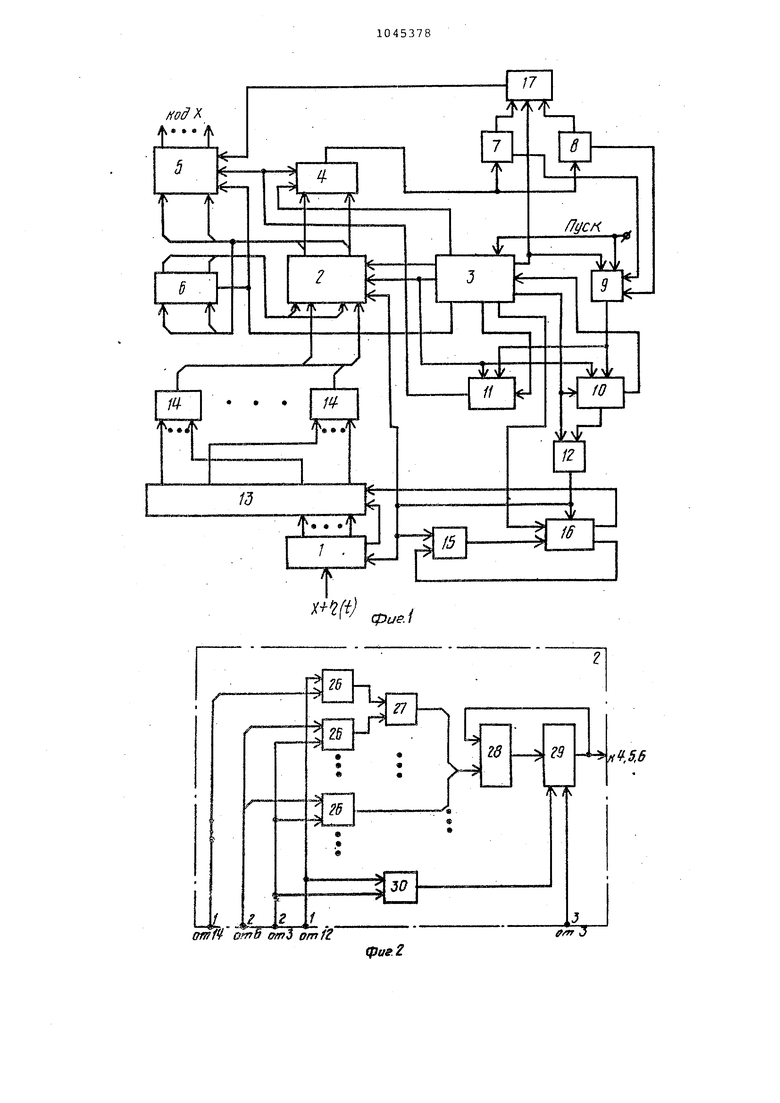

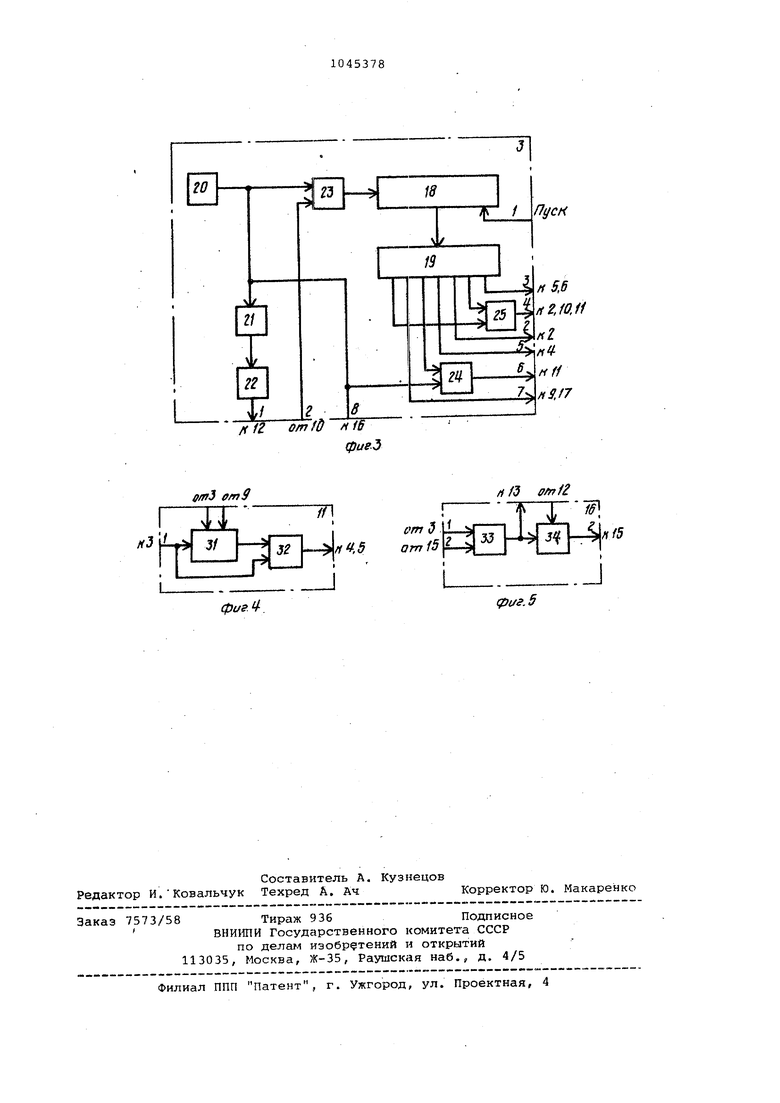

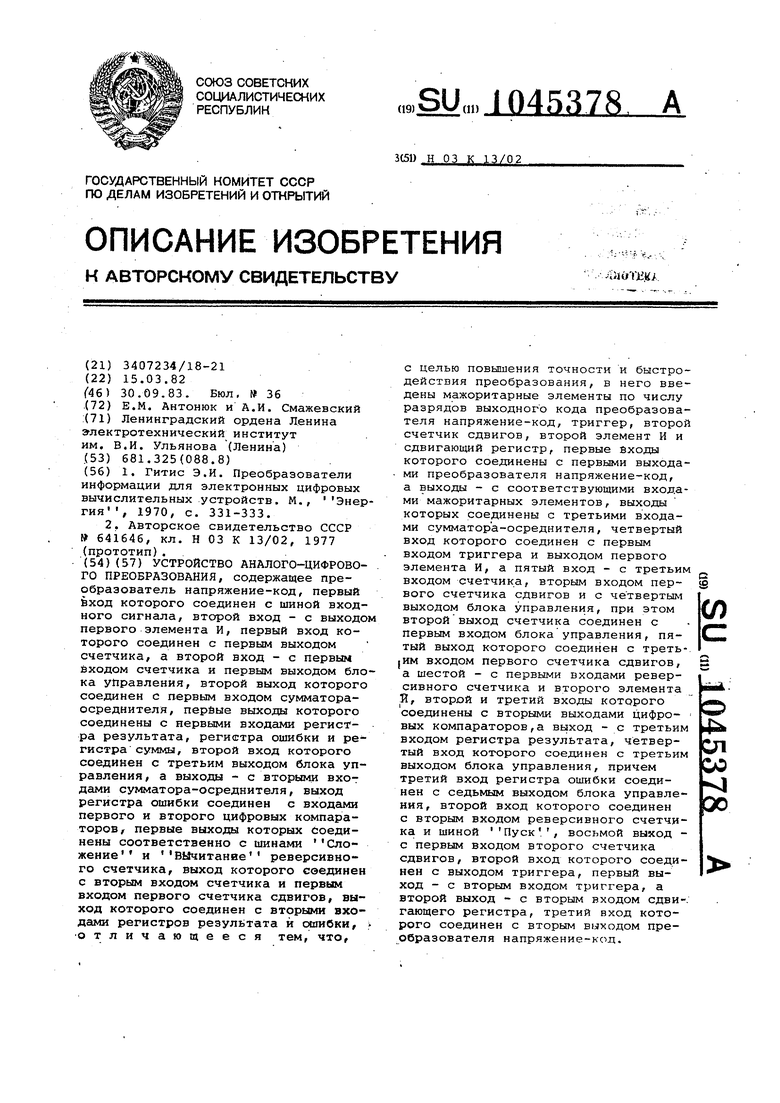

Изобретение относится к цифровой электроизмерительной технике и може быть использовано в информационноизмерительных системах, системах ав томатического управления и контроля работающих в условиях аддитивных случайных йомех. Известно устройство аналого-цифрового преобразования, содержащее преобразователь напряжение-код, динамический регистр, ждущий мультивибратор, счетчик и элементы логики D. Недостаток данного устройства увеличение погрешности преобразования при высоком уровне помех и мало быстродействие при низком уровне по мех. Известно устройство аналого-цифр вого преобразования, содержащее преобразователь напряжение-код,первый вход которого соединен с шиной входного сигнала, второй вход - с выходом первого элемента И, первый вход которого соединен с выходом счетчика, а второй вход - с первым входом счетчика и первым выходом блока управления, второй выход кото рого соединен с первым входом сумма тора-оореднителя, первые выходы которого соединены с первыми входами регистра результата, регистра ошибо и регистра суммы, второй вход которого соединен с третьим выходом бло ка управления, а выход - с вторыми входами сумматора-осреднителя, выход регистра ошибки соединен с входами первого и второго цифровых ком паратора, первые выходы которых сое динены соответственно с шинами Вычитание реверсивного счетчика, выход которого соединен с вторым входом счетчика и пе входом первого счетчика сдвигов выход которого соединен с вторыми входами регистров результата и ошиб ки С 2 . Недостаток известного устройства низкая точность преобразования. Цель изобретения - повышение точ ности и быстродействия устройства аналого-цифрового преобразования. Поставленная цель достигается тем что в устройство аналого-цифрового преобразования, содержащее преобразователь напряжение-код, первый вход которого соединен с шиной входного сигнала, BTOpofi вход -с выхоДом первого элемента И., первый вход которого соединён с первым выходом счетчика, а второй вход - с первым входом счетчика и первым выходом блока управления, второй выход которого соединен с первым входом сумматора-осреднителя, первые выходы которого соединены с первыми входами рехистра результата, регистра ошибки и регистра суммы, второй вход кото рого соединен с третьим, выходом блока управления, а выходы - с вторыми входами сумматора-осреднителя, выход регистра ошибки соединен с входами первого и второго цифровых компараторов , первые выходы которых соединены соответственно с шинами Вычитание жение реверсивного счетчика, выход которого соединен с вторым входом счетчика и .первым входом первого счетчика сдвигов, выход которого соединен с вторыми входами регистров результата и ошибки, введены мажоритарные элементы по числу разрядов выходного кода преобразователя напряжение-код, триггер, второй счетчик сдвигов, второго эле-мента И, сдвигающий регистр, первые входы которого соединены с первыми выходами преобразователя напряжение-. код, а выходы - с соответствующими входами мажоритарных элементов, выходы которых соединены с третьими входами сумматора-осреднителя, четвертый вход которого соединен с первым входом триггера, и выходом первого элемента И, а пятый вход - с третьим вход-ом счетчика и вторым входом первого счетчика сдвигов и с четвертым выходом блока управления, при этом второй выход счетчика соединен с первым входом блока управления, пятый выход которого соединен с третьим входом первого счетчика сдвигов, а шестой - с первыми входами реверсивного счетчика и второго элемента И, второй и третий входы которого соединены с вторыми выходами цифровых компараторов, а выход - с третьим входом регистра результата, четвертый вход которого соединен с третьим выходом блока управления, причем третий вход регистра соединеп с седьмым выходом блока управления; второй вход которого соединен с вторым входом реверсивного счетчика и шиной Пуск, восьмой выход - с первым входом второго счетчика сдвигов, второй вход которого согздинен с выходом триггера, первый выход с вторым входом триггера,а второй .выход - с вторым входом сдвигающего регистра, третий вход которого соединен .с вторым выходом преобразователя напряжение-код„ На фиг,1 показана структурная схема устройства; на фиг.2 - то же блоков сумматора-осреднителя; на фиг.З то же, устройства управления; на фиг.4 - то же, первого счетчика сдвигов; на фиг.5 - то же, второго счетчика сдвигов. Устройство содержит преобразователь 1 напряжение-код (ПНК)., сумматоросреднитель 2, блок 3 управления, регистр 4 ошибки, регистр 5 результата, регистр 6 суг-мы, цифровые ком.параторы 7 и 8, реверсивный счетчик 9, счетчик 10, первый c4-eT4viK 11 сдвигов, первый элемент И 12, сдвига ющий регистр 13,, мажоритарные эле- менты 14, триггер 15, второй счетчик 16 сдвигов, второй элемент И 17. Первый вход ПНК 1 соединен свходом устройства, второй вход - с выходом элемента И 12, первым управляющим входом сумматора 2, третьим входом счетчика 16 и первым входом триггера 15, управляющий вход ПНК 1 соединен с первым управляющим входом регистра 13, а кодовые выходы - с ко довыми входами регистра 13, кодовые входы-выходы регистра 13 соединены с входами соответствующих мажоритарных элементов 14, а второй управляющий вход регистра 13 - с первым выходом счетчика 16,. выходы мажоритарных эле ментов 14 соединены с первой группой кодовых входов сумматора 2, вторая группа кодовых входов которого соединена с кодовыми вглходами регистра 6, второй управляющий вход cy ЛJмaтopa 2 соединен с вторым выходом блока 3 управления, а третий управляющий вход сумматора 2-е третьими входами счетчиков 10 и 11 и четвертым выходом блока 3 .управления, кодовые выходы сумматора 2 соединены с кодовыми входами регистров 4-6, управляющий вход регистра 6 соединен с первым управляющим входом регистра 5 и третьим выходом блока 3 управления , пятый выход которого соединен с первым управляющим входом регистра 4, второй управляю иий вход которого соединен с вторым управляющим входом регистра 5 и выходом счетчика И/ первый вход счетчика 11 соединен с шестым выходом блока 3 управления, первый вход которого соединен с вто рым входом счетчика 9 и шиной а второй вход - с вторЕлм выходом счетчика 10, второй вход ко торого соединен с вторым входом счетчика 11 и выходом счетчика 9, а первый вход - с вторым входом элемента И 12 и первым выходом блока 3 управления, первый выход счетчика 1 соединен с первым входом элемента И 12, восьмой выход блока 3 управле ния соединен с первым входом счетчи ка 16, второй вход которого соедине с выходом триггера 15, а второй с вторам входом триггера 15, выход .регистра 4 соединен с входами компараторов 7 и 8, первые выходы кото рых соединены с вторым и третьим входами элемента И,17, а вторые выСложениеходы - с шина1ли -жтание счетчика 9, первый вход KOTCpoio соединен с первым входом элеменга И 17 и седы.-ШйМ выходом бло ка 3 управления, выход элемента. И 1 соеднкеп с третьим yпpaвляюLf им входом регистра 5, выход которого соединен с выходом устройства. ПНК 1 предназначен для преобразования аналогового сигнала х(-(:.) в цифровой код. CyKiMarop 2 предназу а-че н д.пя выполнения операций слогкения и вычитания над поступающими в него цифровыми кодами по сигналам с блока 3. Сумматор 2 представляет собой сугда атор накапливающего типа с цифровыгу мультиплексором на два канала на входе, позволяющим суммировать данные последовательно во времени от различных источников регистров 13 и 6 . Сумматор 2 (фиг.2) содержит элементы И 26, элементы ИЛИ 27, комби-, национный сумматор 28, регистр 29 памяти, элемент ИЛИ 30. Блоки 26 и 27 образуют цифровой мул типлексор (1 разрядов на 2-канала, где Vi разрядность выходного кода, ПНК 1, так как разрядность суммы из регистра 6 больше чем и , то остальные элементы И 26 служат для подключения к сумматору 28 старших разрядов сумлы) , блоки 28 и 29 - накапливающий сумматор, блок 30 - цепь записи результата сложения из сумматора 28 в регистр 29 памяти. На вход комбинационного сум.1атора 28 поступают коды от мажоритарных элементов 14 или регистра 6 суммы в зависимости от управляющих сигналов с элемента И 12 и устройства 3 управления. Запись результата сложения в регистр 29 памяти осуществляется по заднему фронту управляющих импульсов от блока 3 управления и И 12. По сигналу от блока 3 .управления, поступающему на третий вход сумматора 2 происходит обнуление регистра 29 памяти. Блок 3 управления обеспечивает выдачу управляющих сигналов на регистры и счетчики 2, 4, 5, 6, 9 - 12, 16 и 17 устройства. Схема блока 3 управления (фиг.З) содержит счетчик 18 импульсов,, дешифратор 19, генератор 20 импульсов, счетчик 21 импульсов, одновибратор 22, элементы И 23 и 24, элемент ИЛИ 25. Блоки 18, 19, 24 и 25 образуют распределитель импульсов. Счетчи.к 21 импульсов предназначен для деления частоты импульсов от генератора 20 импульсов до частоты импульсов запуска ПНК1. Одновибратор 22 предназначен для формирования импульса запуска ПНК1 требуемой длительности. Элемент И 23 служит вентилем, разрешая или запрещая поступление импульсов с генератора 20 на распределитель импульсов по управляющим сигналам со счетчика 10, поступающим на второй вход б,пока 3 управления. На первый вход блока 3 упрарления подается сигнал Пуск, по которому счетчик 18 импульсов устанавливается в состояние соответствующее последнему такту цикла работ распределителя импульсов. Регистр 4 предназначен для приема, хранения и выдачи кода ошибки. Регистр 4 представляет собой сдвигающий регистр с параллельнЬй записью и считыванием информации. Регистр 5 предназначеш для приема, хранения и выдачи кода результата аналого-цифрового преобразования. Регистр 5 представляет собой сдвигающий регистр с параллел ной записью и считыванием информаци регистр б - сдвигающий регистр с па раллельной записью и считыванием ин формации и предназначен для приема, хранения и выдачи кода суммы резуль татов преобразования в ПНК1 на интервале цифрового интегрирования Т. Регистр 6 представляет собой регист с параллельной записью и считыванием информации. Компараторы 7 и -8 служа для сравнения текущего значения погрешности преобразования с заданной допустимой величиной. Компара гор 7 выдает сигнал в случае, если абсо(лютная величина текущей погрешности :меньше или равна нижнему пределу допустимйх значений, компаратор 8 если абсолютная величина текущей погрешности больше верхнего предела допустимых значений. Сигналы, инвер ные выходным сигналам компараторов 7 и 8, поступают на входы элемента И 17-. При наличии Сигналов на этих входах элемента И 17 импульс от бло ка 3 управления, поступающий на тре тий вход элемента И 17, проходит на регистр 5 и разрешает считывание кода результата. Счетчик 9 предназначен для хранения кода текущегоз значения числа осредняемых отсчетов на интервале Т и изменения этого кода по управляющим сигналам с блока 3 управления компараторами 7 и 8, По сигналам с компаратора 7 и блока 3 управления, поступающим на шину Вычитание счетчика 9, значение кода в нем уменьшается на приращение числа осредняемых отсчетов iN , а по сигналам с коммутатора 8 и блока 3 управления, поступающим на шину Сложение счетчика 9, увеличивается на uVl . Счетчик 10 служит для подсчета числа импульсов, поступгиоших за запуск ПНК1. По сигналу из блока 3 управления в старший разряд счетчика 10 записывается в остальные - дополнительный код числа осредняемых отсчетов Н, следовательно счётчик 10 на один разряд длиннее, чем счетчик 9. При прохождении N импульсов запуска НПК1 счетчик ID запрещает их поступление на ПНК1 через элемент И 12, который служит вентилем, разрешая и запрещая прохождение импульсов на запуск ПНК1 по сигналам со счетчика 10. Счетчик 11 предназначен для подсчета числа сдвигающих импульсов, поступающих в регистры 4 и 5. Сдвиг кода вправо в регистры 4 и 5 соответствует делению на число осредняемых отсчетов NV/ если кратно степени два записанной в регистры код двоичный. Счетчик 11 (фиг.4) содержит счетчик 31 импульсов и элемент И 32. В старший разряд счетчика31 импульсов по сигналу из блока 3 управления заа в остальные писываетсядополнительный код числа осредняемых отсчетов М из счетчика 9, следовательно счетчик 11 на один разряд длиннее, чем счетчик 9. Сдвигающие импульсы поступают из блока 3 управления на первый вход счетчика 11, подсчет сдвигающих импульсов осуществляется в счетчике 31 импульсов и при прохождении требуемого количества импульсов он запрещает их поступление на регистры 4 и 5 через элемент И.32, выполняющий функцию вентиля. Регистр 13 предназначен для приема:, хранения и выдачи кодов осЧредняемых отсчетов. Запись кода текущего -отсчета, поступающего, с ПНК1, происходит в У1 крайних правых (левых) разрядах регистра по сигналу Конец преобразования, поступающему с ПНК1. Сдвиг кода влево (вправо) в регистр 13 осуществляется по импульсам, поступающим из счетчи ка 16 на шину Сдвиг влево (Сдвиг вправо). Регистр 13 представляет собой сдвигающий регистр с параллельной записью и съемом информации и содержит (2К+1) И разрядов, где У1 - разрядность выходного кода ПНК1 с учетом знака, К - число отсчетов сигнала, искаженных импульсной помехой высокого уровня, 1ИЛИ число последовательных сбоев ПНК1, равных М пр L -длительность импульсной помехи; -время преобразования ПНК1; число, равное X, если X целое или ближайшее большее X целое число. При этом для определения величины необходимо брать в (1) 11, упоЭлементы 14 мажоритарности предазначены для поразрядной логической бработки информации, записанной соответственно в 6 Д+и, .. . , Р+2 КИ азрядах регистра 13 для соответствующего Е-го элемента 14. Элемент 14 имеет 2К+1 входов. Порядок мажоитарности М К+1, число-элементов 14 равно VI . Величина М определяется априорно с учетом (1), Триггер 15 предназначен для управления работой счетчика 16. По заднему фронту импульса запуска ПНК1 триггер 15 разр шает поступление сдвигающих импульсов на регистр 13, по сигналу счетчина 16 - запрещает. Счетчик 16 пред назначен для подсчета числа.сдвигающих импульсов, поступающих на шину Сдвиг влево в регистр 13. Счетчик 16, содержит элемент И 33 и ьчетчик 34 импульсов. По разрешающему управляющему сигналу от тригге ра 15 импульсы из объекта 3 управле ния через элемент И 33, выполняющий функцию вентиля, поступают на регистр 13 и на счетчик 34 импульсов. Счетчик 34 осуществляет подсчет сдвигающих импульсов и при прохожде нии VI импульсов выдает сигнал на триггер 15. Триггер 15 возвращается в исходное состояние и запрещает поступление сдвигающих импульсов че рез элемент И 33. Устройство работает следующим образом. По сигналу .Пуск в реверсивный счетчик 9 записывается код числа осредняемых отсчетов NQ, кратного степени два, соответствующий наиболее вероятному интервалу интегрирова ния, определяемому априорно по разбросу дисперсии флуктуационной помехи V(-t) , в блоке 3 управления распределитель -импульсов устанавливается в состояние, соответствующее последнему такту цикла его работы. После окончания переходного процесса (одного цикла работы р.аспределителя импульса) счетчика 3 будет записан код числа Wi, в счетчик 10 и счетчик И сдвигов будет записан дополнительный код числа NJ , причем Wj равно Ы{5 либо 2Np, либо --No Переходный процесс длительностью ( + Tt) , где Тц --время цикла работы распределителя импульсов, необходим для заполнения регистра 13 после включения устройства, при этом, для того, чтобы переходный процесс укладывался в один цикл работы распределителя импульсов необходимо условие Wj, к. Затем производится Ni -кратное преобразование входного сигнала Ol 4 ПШ в преобразователе 1 по сигналам с блока 3 управления через элемент И 12, на второй вход которого поступает разрешающий потенциал со счетчика 10, задающего число преобразований. При этом может использоваться любой тип преобразователя ПНК1. Полученный в результате однократного преобразования код в ПНК1 импульсом Конец преобразования (КП) записывается в сдвигающий регистр 13 (в его крайние м разрядов По переднему фронту импульса запуска ПНК1, снимаемого с элемента И 12, происходит установка дополнительного кода числа и в счетчик 16 сдвигов. По заднему фронту импульса запуска ПНК1 триггер 15 устанавливается в и разрешает через состояние счетчик 16 прохождение импульсов с блока 3 управления на шину Сдвиг влево в регистр 13. Подсчет сдви.гающих иглпульсов выполняется-в счетчике 16 и при прохождении и импульсов Он возвращает триггер 15 в исходное состояние О. Триггер 15 запрещает поступление импульсов с блока 3 управления в регистр 13. Период сдвигающих импульсев Т( выбирается из условия Tj, (Ьрр --Ь,) /и t где t- - длительность импульса запуска ПНК1. Информация в регистре 13 оказывается сдвинутой влево на И разрядов. Далее с помощью мажоритарных элементов 14 выполняется поразрядная обработка информации, записанной в Е. ,С + и, . . . , разрядах регистра 13. Элементами 14 устраняется действие импульсной помехи высокого .уровня, и погрешность результата будет определяться флуктуационной помехой. Код результата с элементов 14 поступает в сумматоросреднитель 2 по импульсу запуска ПНК1, где суммируется с его содержимым. ПослеN: -кратного преобразования счетчик 10 выдает сигнал в объект 3 управления, по которому начинает работать распределитель импульсов (РИ) блока 3 управления. На первом такте работы РИ код суммы из сумматора 2 считывается в регистр 6 суммы и регистр 5 результата. На втором такте РИ происходит установка содержимого сумматора 2 равным нулю и установка в счетчиках 10 и 11 дополнительного кода числа W; , при этом распределитель импульсов блока 3 управления временно прекращает свою работу. Затем производится новое Jj -кратное преобразование в ПНК1, логическая обработка выходных кодов ПНК1 в элементах 14 и суммирование кодов в сумматоре 2. После Мл преобразований счетчик 10 выдает сигнал в блок 3 управления, разрешая работу распределителя импульсов. На третьем работы распределителя импульсов из содержимого сумь1атора 2 вычитается код, записанный в регистр 6, разность кодов, равная til ьО с учетом знака переписывается в регистр 4 ошибки на четвертом такте работы распределителя импульсов. На пятом такте работы РИ из БУ 3 на шину Сдвиг вправо регистров 5 результата и 4 ошибки через счетчик 1.1 сдвигов поступают импульсы. Подсчет сдвигающих импульсов выполняется в

счетчике 11 и при прохождении Ы;, импульсов счетчик 11 запрещает их поступление в регистры 5 и 4. Осред. ненный результат из регистра 5 выдается на считывание, а из регистра 4 разность U сравнивается в цнф. ровых компараторах 8 и 7 с допустиглым уровнем погрешности от помех Д . Выходы цифровых компараторов управляют прибавлением или вычитанием величины приращения числа осредняемых отсчетов из кода реверсивно го счетчика 9 и выдачей С элемента И 17 разрешающего считывание кода результата с регистра 5.

Таким образом,- изменение йнтервала интегрирования, определяемого кодом счетчика 9 на -1 -ом шаге поиска осуществляется на шестом такте работы распределителя импульсов блока 3 управления в соответствии с итерационной формулой

,

f-b-1 |u7./N -{ 1Л1 О t |A7:)Nj)eu,

VI,.,- No-t-©No

Если

AI

д,

3

то на шестом такте работы распределителя импульсов с выхода элемента И 17 снимается сигнал, разрешающий считывание кода с регистра. 5. На седьмом такте работы распределителя импульсов происходит запись доП гельного кодачисла осредняемых о ОБ из счетчика 9 ,в счетчик 10 и -г чик 11 сдвигов, а также обнуjic.... сумматора 2, счетчик 10 выдает сигнал в блок 3 управления и запрещает работу распределителя импульсов. Устройство оказывается подготовленным для следующего цикла работы.

После нескольких щагов поиска (нескольких описанных циклов) в реверсивном счетчике 9 устанавливается некоторое значение Klj ., соответствующее значению допустимой погрешности fXj с заданной доверительной вероятностью , причем воздействие импульсных помех на погрешность преобразования и на время поиска необходимого H,j (быстродействие устройства) исключается .

В данном устройстве по сравнению с известным погрешность преобразоваKi:u-v - iit)

ния уменьшена на величину

5

где R - значение выходного кода ПНК1 при действии импу-льсной помехи если число отсчетов сигнала, искаженных импульсной помехой, К на первом из двух сравниваемых интервалов цифрового интегрирования равно числу отсчетов сигнала, искаженных импульсной помехой на втором интервале интегрирования.

Таким образом, при различии в числе отсчетов сигнала, искаженных импульсной помехой высокого уровня, на первом и втором сравниваемых интервалах цифрового интегрирования быстродействие данного устройства будет выше не менее, чем на 4Т, где Т - .длина интервала интегрирования.

м5,В 112,10.11

к1 HtiMfi

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Устройство аналого-цифрового преобразования | 1989 |

|

SU1647894A1 |

| Устройство аналого-цифрового преобразования | 1981 |

|

SU1012435A1 |

| Устройство аналого-цифрового преобразования | 1977 |

|

SU641646A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1037313A1 |

| Система для передачи телеизмерительной информации | 1982 |

|

SU1113832A1 |

| Цифровой измеритель пикового значения импульсных воздействий | 1984 |

|

SU1167734A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU432676A1 |

| Устройство для ввода информации | 1987 |

|

SU1522189A1 |

| Устройство для распознавания образов | 1989 |

|

SU1709359A1 |

УСТРОЙСТВО АНАЛОГО-ЦИФРОВО- . ГО ПРЕОБРАЗОВАНИЯ, содержащее преобразователь напряжение-код, первый Вход которого соединен с шиной входного сигнала, второй вход - с выходом первого элемента И, первый вход которого соединен с первым выходом счетчика, а второй вход - с первым входом счетчика и первым выходом блока управления, второй выход которого соединен с первым входом сумматораосреднителя, перйые выходы которого соединены с первыми входами регистра результата, регистра ошибки и регистра суммы, второй вход которого соединен с третьим выходом блока управления, а выходы - с вторыми вхог дами сумматора-осреднителя, выход регистра ошибки соединен с входами первого и второго цифровых компараторов, первые выходы которых соединены соответственно с шинами Сложение и ВЫчитанве реверсивного счетчика, выход которого соединен с вторым входом счетчика и первым входом первого счетчика сдвигов, выход которого соединен с вторыми входами регистров результата и ошибки, j. отличающееся тем, что. с целью повышения точности и быстродействия преобразования, в него введены мажоритарные элементы по числу разрядов выходного кода преобразователя напряжение-код, триггер, второй счетчик сдвигов, второй элемент И и сдвигающий регистр, первые Входы которого соединены с первыми выходами преобразователя напряжение-код, а выходы - с соответствующими входами мажоритарных элементов, выходы которых соединены с третьими входами сумматора-осреднителя, четвертый вход которого соединен с первым входом триггера и выходом первого элемента И, а пятый вход - с третьим входом счетчика, вторым входом первого счетчика сдвигов и с четвертым (Л выходом блока управления, при этом второй выход счетчика соединен с с первым входом блока управления, пятый выход которого соединен с треть|ИМ входом первого счетчика сдвигов, а шестой - с первыми входами реверсивного счетчика и второго элемента И, второй и третий входы которого соединены с вторыми выходами цифро- вых компараторов,а выход - с третьим входом регистра результата, четверел тый вход которого соединен с третьим : выходом блока управления, причем третий вход регистра ошибки соединен с седьмым выходом блока управлеX ния, второй вход которого соединен с вторым входом реверсивного счетчика и шиной Пуск . , восьмой выход с первым входом второго счетчика сдвигов, второй вход которого соединен с выходом триггера, первый выход - с вторым входом триггера, а второй выход - с вторым входом СДВИ-. гаюадего регистра, третий вход которого соединен с вторым выходом преобразователя напряжение-ксщ.

fTll omW /v iS

em S

a 15 am 15

.J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М., Энергия f 1970, с | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство аналого-цифрового преобразования | 1977 |

|

SU641646A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-09-30—Публикация

1982-03-15—Подача