11

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в информационно-измерительных системах и системах автоматического управления, работающих в условиях аддитивных случайных помех.

Цель изобретения - расширение динамического диапазона измеряемого сигнала за счет того, что при поразрядной логической обработке кодов отсчетов сигнала Операция И выполняется с (k+2) отсчетами выходного кода преобразователя напряжение-код где k - число отсчетов сигнала, искаженных импульсной помехой высокого уровня, или число последовательных сбоев преобразователя напряжение- код, что позволяет учесть возможное изменение числа значащих разрядов кода отсчетов.

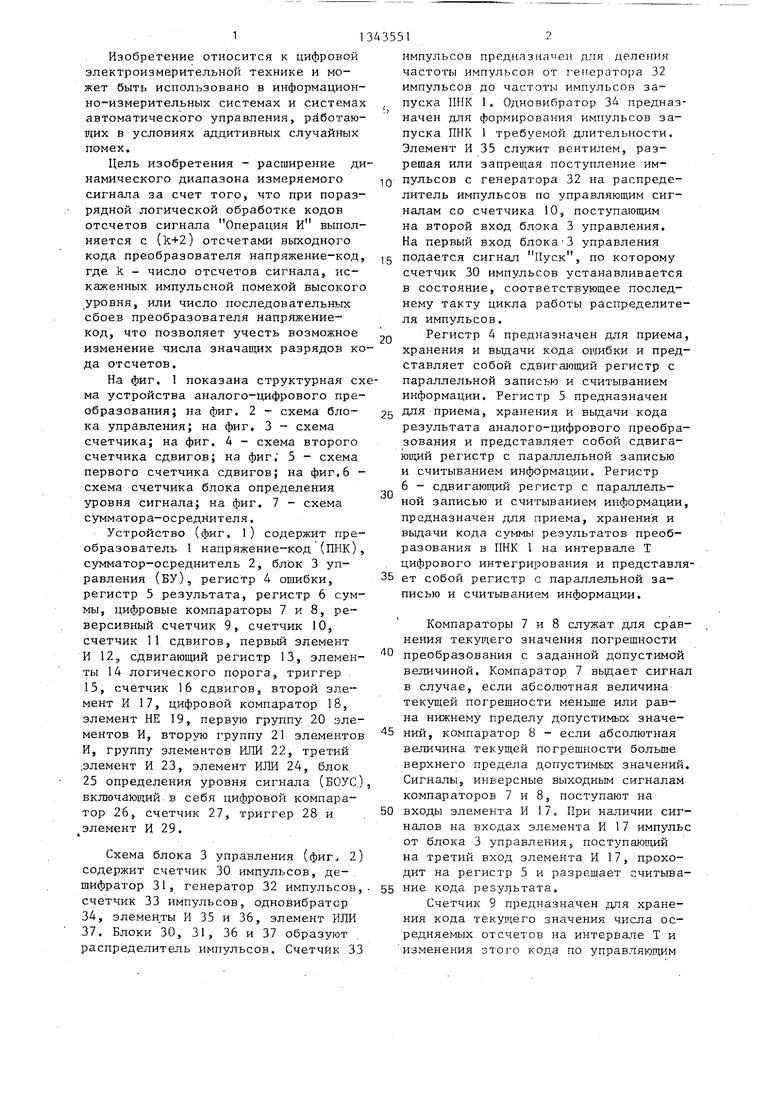

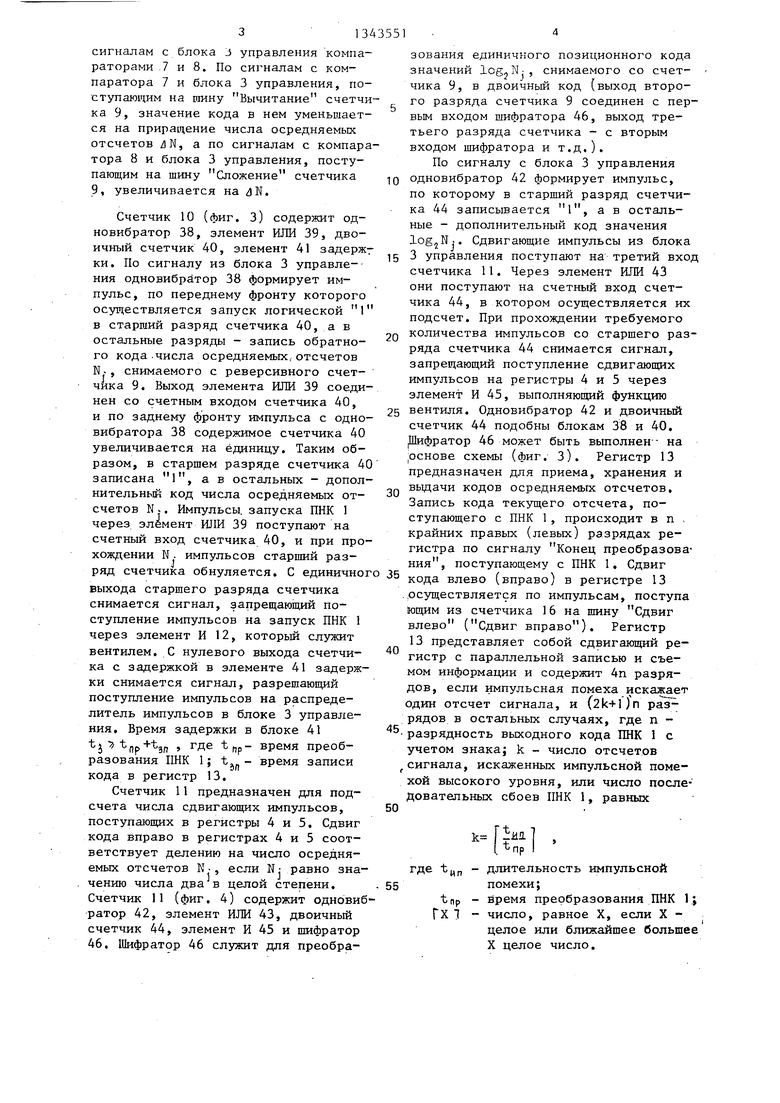

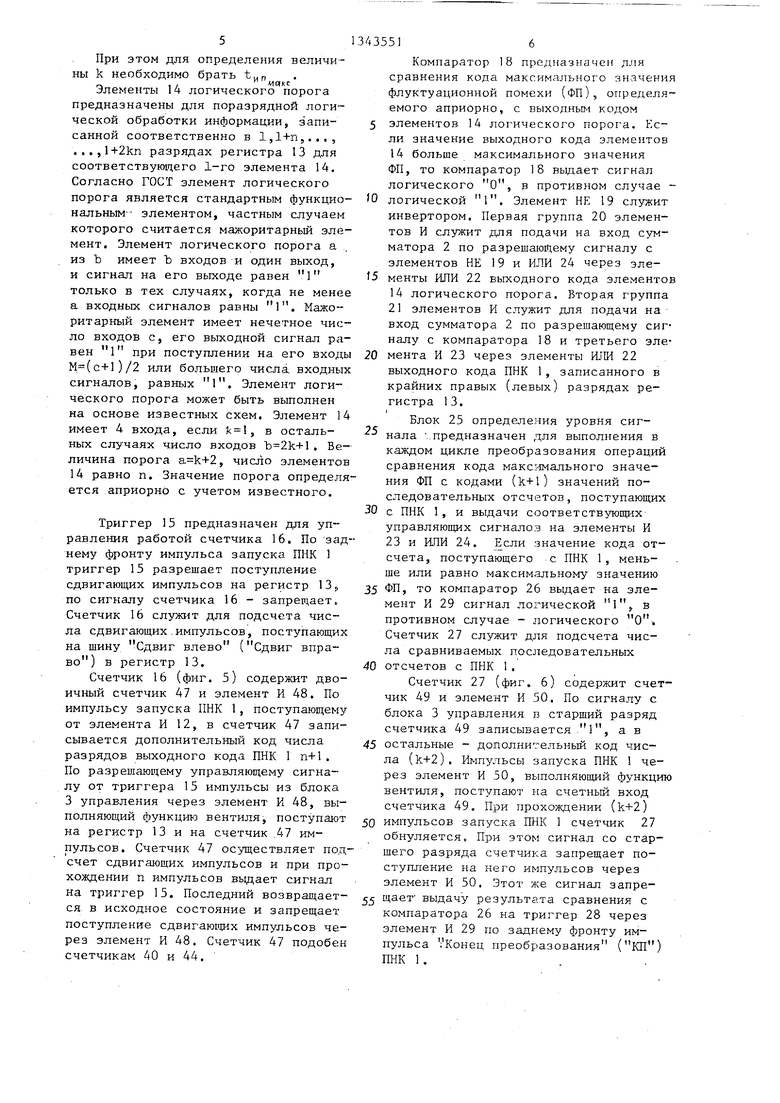

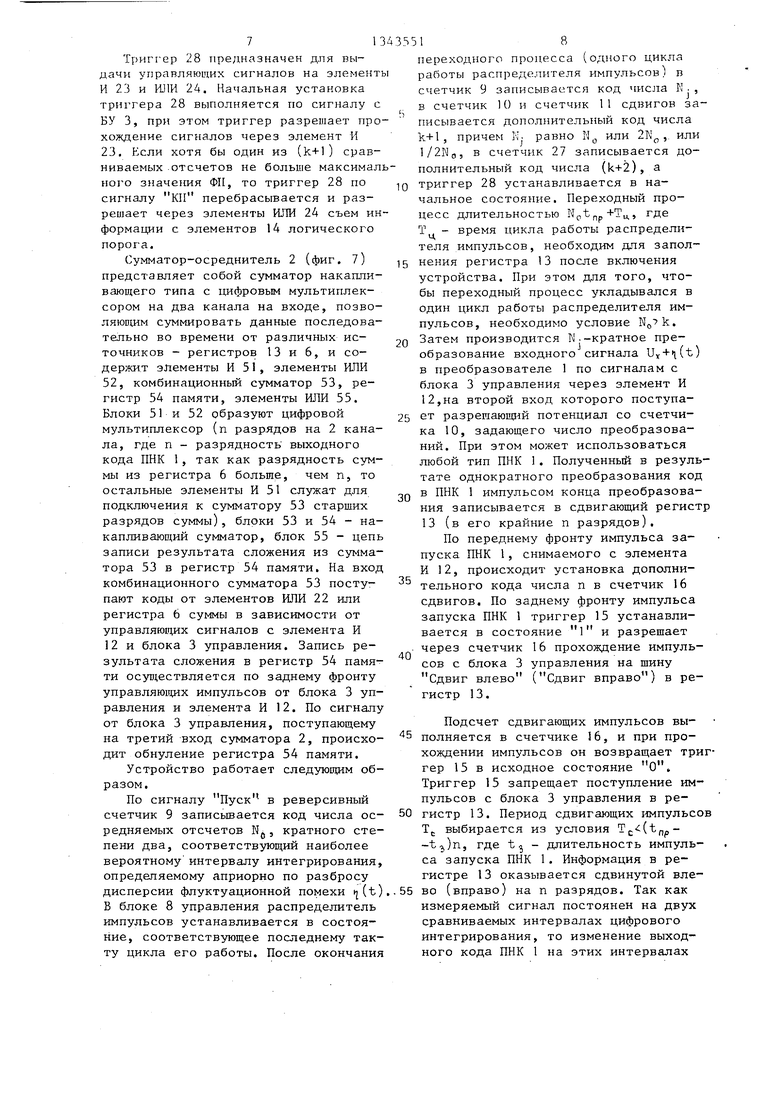

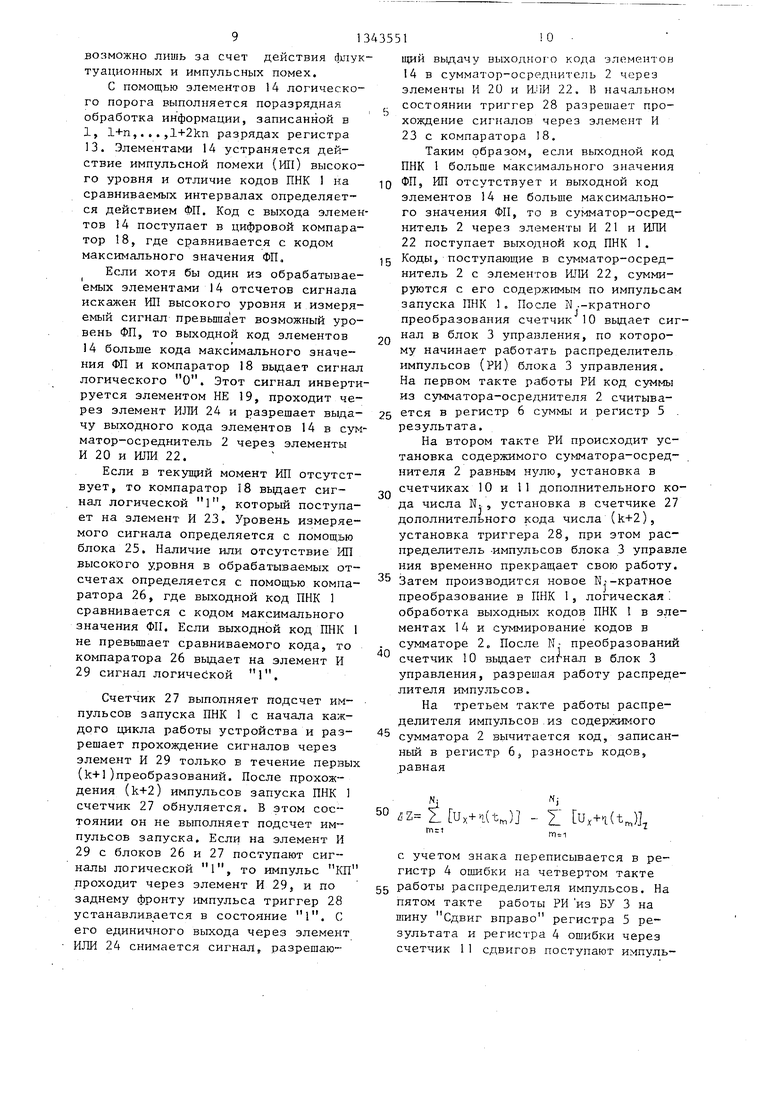

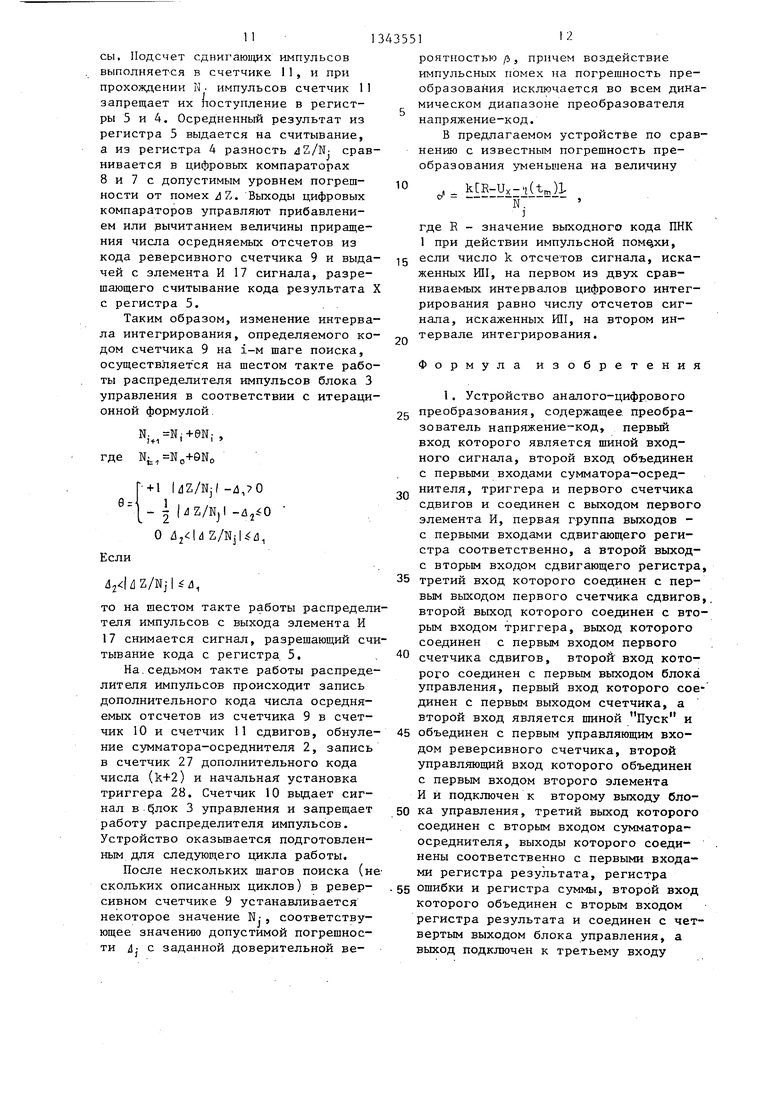

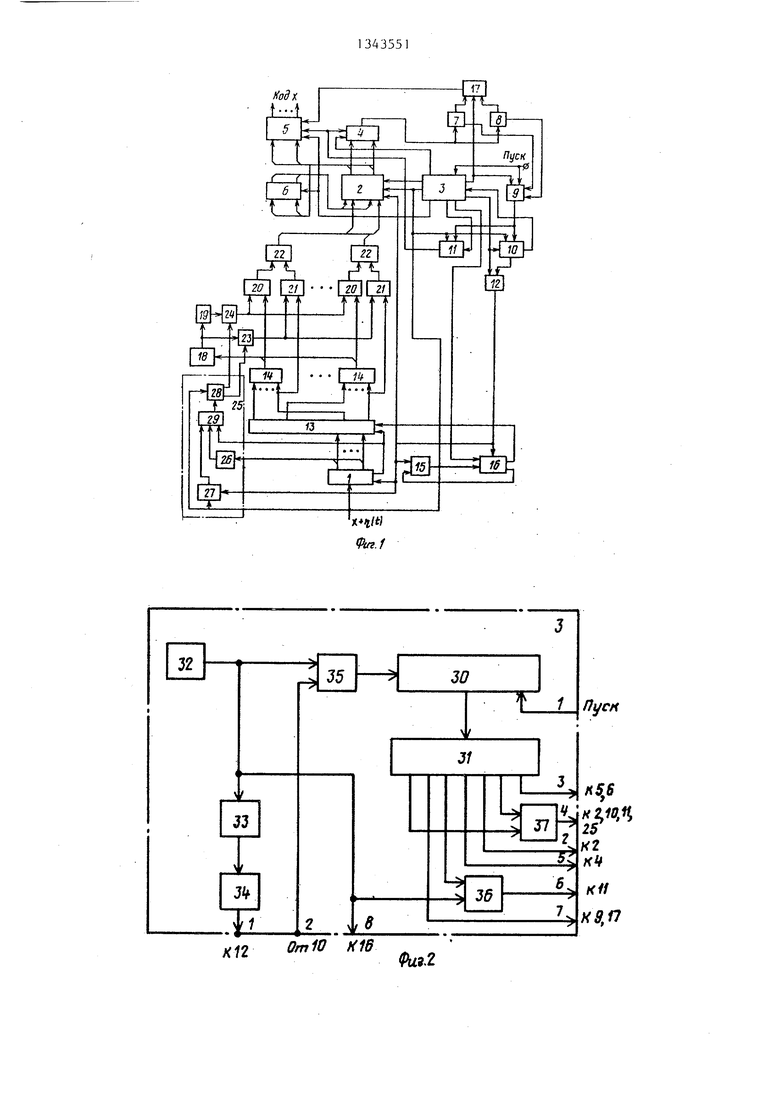

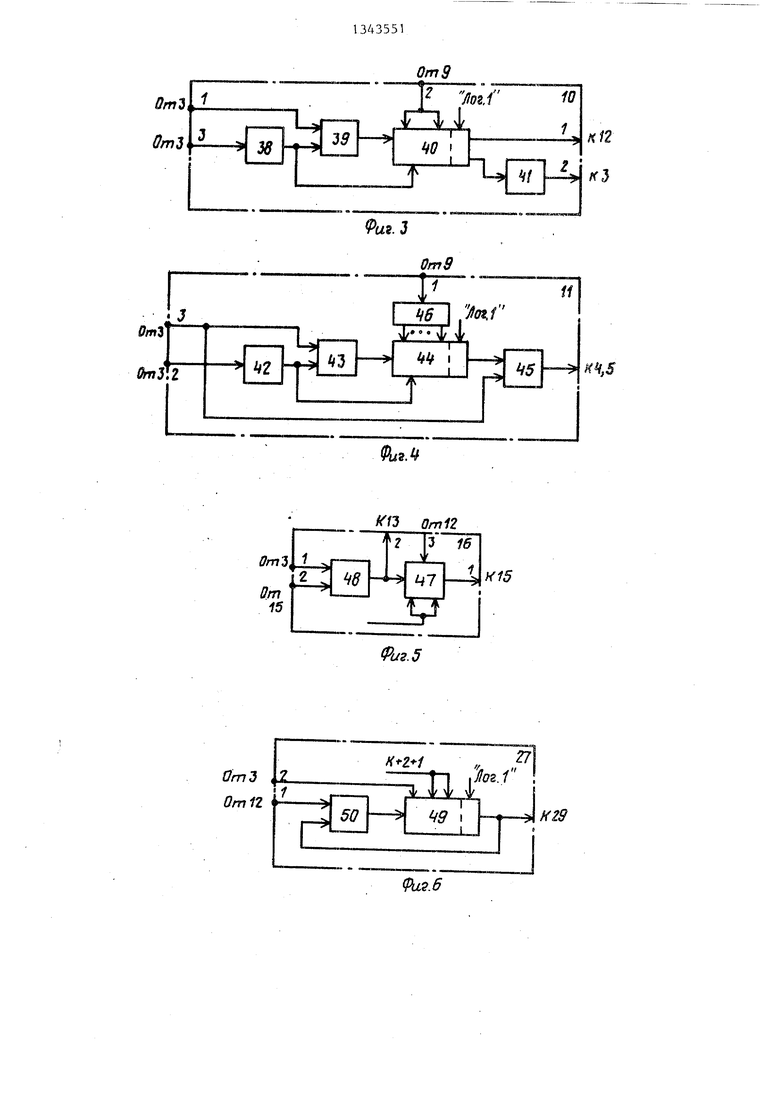

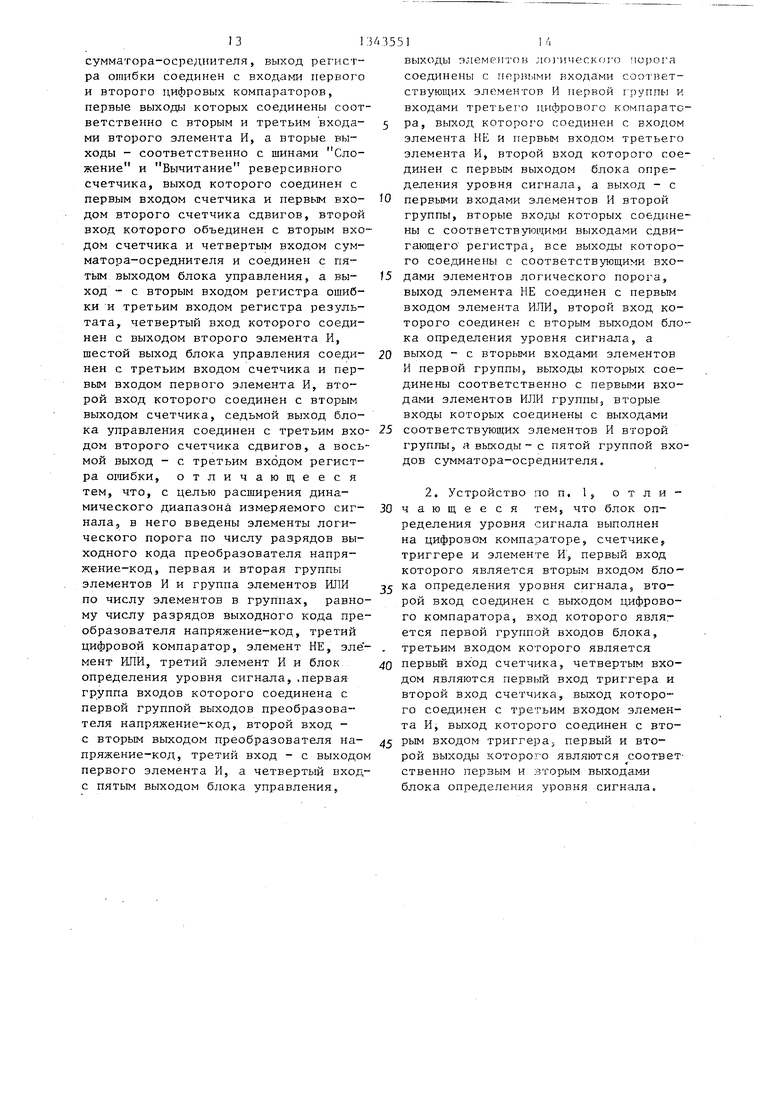

На фиг, 1 показана структурная схма устройства аналого-цифрового преобразования; на фиг, 2 - схема блока управления; на фиг, 3 - схема счетчика; на фиг, 4 - схема второго счетчика сдвигов; на фиг, 5 - схема первого счетчика сдвигов; на фиг,6 - схема счетчика блока определения уровня сигнала; на фиг, 7 - схема сумматора-осреднителя,

Устройство (фиг, 1) содержит преобразователь 1 напряжение-код (ПНК) сумматор-осреднитель 2, блок 3 управления (БУ), регистр 4 ошибки, регистр 5 результата, регистр 6 суммы, цифровые компараторы 7 и 8, реверсивный счетчик 9, счетчик 10, счетчик 11 сдвигов, первьш элемент И 12,, сдвигающий регистр 13, элементы 14 логического порога, триггер 15, счетчик 16 сдвигов, второй элемент И 17, цифровой компаратор 18, элемент НЕ 19, первую группу. 20 элементов И, вторую группу 21 элементов И, группу элементов ИЛИ 22, третий ;элемент И 23, элемент ИЛИ 24, блок 25 определения уровня сигнала (ВОУС включающий.Б себя цифровой компаратор 26, счетчик 27, триггер 28 и элемент И 29,

Схема блока 3 управления (фиг. 2) содержит счетчик 30 импульсов, дешифратор 31, генератор 32 импульсов, счетчик 33 импульсов, одновибратор 34, элементы И 35 и 36, элемент ИЛИ 37, Блоки 30, 31, 36 и 37 образуют распределитель импульсов. СчетчИк 33

импульсов предназначен для деления частоты импульсов от генератора 32 импульсов до частоты импульсов запуска ПНК 1, Одновибратор 34 предназначен для формирования импульсов запуска ПНК 1 требуемой длительности. Элемент И 35 служит вентилем, разрешая или запрещая поступление импульсов с генератора 32 на распределитель импульсов по управляющим сигналам со счетчика 0, поступающим на второй вход блока 3 управления. На первый вход блока 3 управления подается сигнал Пуск, по которому счетчик 30 импульсов устанавливается в состояние, соответствующее последнему такту цикла работы распределителя импульсов.

Регистр 4 предназначен для приема, хранения и вьщачи кода ошибки и представляет собой сдвигающий регистр с параллельной записью и считыванием информации. Регистр 5 предназначен

для приема, хранения и выдачи кода результата аналого-цифрового преобра- зо вания и представляет собой сдвигающий регистр с параллельной записью и считыванием информации. Регистр 6 - сдвигающий регистр с параллельной записью и считыванием информации, предназначен для приема, хранения и вьщачи кода суммы результатов преобразования в ПНК 1 на интервале Т цифрового интегрирования и представляет собой регистр с параллельной записью и считыванием информации.

Компараторы 7 и 8 служат для сравнения текущего значения погрешности

преобразования с заданной допустимой величиной. Компаратор 7 выдает сигнал в случае, если абсолютная величина текущей погрешности меньше или равна нижнему пределу допустимых значеНИИ, компаратор 8 - если абсолютная величина текущей погрешности больше верхнего предела допустимых значений. Сигналы, инверсные выходным сигналам компараторов 7 и 8, поступают на

входы элемента И 17, При наличии сигналов на входах элемента И 17 импульс от блока 3 управления5 поступающий на третий вход элемента И 17, проходит на регистр 5 и разрешает считывание кода результата.

Счетчик 9 предназначен для хранения кода текущего значения числа ос- редняемых отсчетов на интервале Т и изменения этого кода по управляющим

313А

сигналам с блока J управления компараторами 7 и 8. По сигналам с компаратора 7 и блока 3 управления, поступающим на тину Вычитание счетчика 9, значение кода в нем уменьшается на приращение числа осредняемых отсчетов jN, а по сигналам с компаратора 8 и блока 3 управления, поступающим на шину Сложение счетчика 9, увеличивается на 4N.

Счетчик 10 (фиг. З) содержит од- новибратор 38, элемент ИЛИ 39, двоичный счетчик 40, элемент 41 задержг ки. По сигналу из блока 3 управления одновибратор 38 формирует импульс, по переднему фронту которого осуществляется запуск логической 1 в старший разряд счетчика 40, а в остальные разряды - запись обратно- го кода .числа осредняемых, отсчетов N., снимаемого с реверсивного счетчика 9, Выход элемента ИЛИ 39 соединен со счетным входом счетчика 40, и по заднему фронту импульса с одно- вибратора 38 содержимое счетчика 40 увеличивается на единицу. Таким образом, в старшем разряде счетчика 40 записана 1, а в остальных - допол- нительньй код числа осредняемых от- счетов N.. Импульсы, запуска ИНК 1 через элемент ИЛИ 39 поступают на счетный вход счетчика 40, и при прохождении N - импульсов старший разряд счетчика обнуляется. С единичног выхода старшего разряда счетчика снимается сигнал, запрещающий поступление импульсов на запуск ПНК 1 через элемент И 12, которьш служит вентилем. С нулевого выхода счетчи- ка с задержкой в элементе 41 задержки снимается сигнал, разрешающий поступление импульсов на распределитель импульсов в блоке 3 управления. Время задержки в блоке 41 , где tfjp- время преобразования ПНК 1; время записи кода в регистр 13.

Счетчик 11 предназначен для подсчета числа сдвигающих импульсов, поступающих в регистры 4 и 5. Сдвиг кода вправо в регистрах 4 и 5 соответствует делению на число осредняемых отсчетов К-, если N: равно значению числа два в целой степени. Счетчик 11 (фиг. 4) содержит одновибратор 42, элемент ИЛИ 43, двоичный счетчик 44, элемент И 45 и шифратор 46. Шифратор 46 служит для преобра

зования единичного позиционного кода значений , снимаемого со счетчика 9, в двоичный код (выход второго разряда счетчика 9 соединен с первым входом шифратора 46, выход третьего разряда счетчика - с вторым входом шифратора и т.д.).

По сигналу с блока 3 управления одновибратор 42 формирует импульс, по которому в старший разряд счетчика 44 записывается 1, а в остальные - дополнительный код значения logjN;. Сдвигающие импульсы из блока 3 управления поступают на третий вход счетчика 11. Через элемент ИЛИ 43 они поступают на счетный вход счетчика 44, в котором осуществляется их подсчет. При прохождении требуемого количества импульсов со старшего разряда счетчика 44 снимается сигнал, запрещающий поступление сдвигающих импульсов на регистры 4 и 5 через элемент И 45, выполняющий функцию вентиля. Одновибратор 42 и двоичный счетчик 44 подобны блокам 38 и 40. |Шифратор 46 может быть выполнен на jocHOBe схемы (фиг. З). Регистр 13 предназначен для приема, хранения и вьщачи кодов осредняемых отсчетов. Запись кода текущего отсчета, поступающего с ПНК 1, происходит в п , крайних правых (левых) разрядах регистра по сигналу Конец преобразования, поступающему с ПНК 1. Сдвиг кода влево (вправо) в регистре 13 осуществляется по импульсам, поступа йщим из счетчика 16 на шину Сдвиг влево (Сдвиг вправо). Регистр 13 представляет собой сдвигающий регистр с параллельной записью и съемом информации и содержит 4п разрядов, если импульсная помеха искажает один отсчет сигнала, и (2k+l)n разрядов в остальных случаях, где п - разрядность выходного кода ПНК 1 с учетом знака; k - число отсчетов .сигнала, искаженных импульсной помехой высокого уровня, или число последовательных сбоев ПНК 1, равных

ЛЬа|

1, t пр I

Пр

- длительность импульсной

помехи;

- время преобразования ПНК 1.; - число, равное X, если X целое или ближайшее большее X целое число.

При этом для определения величины k необходимо брать tun

1

Элементы 1ч логического порога

предназначены для поразрядной логической обработки информации, записанной соответственно в 1,1+п,.,,, ...,l+2kn разрядах регистра 13 для соответствующего 1-го элемента 14, Согласно ГОСТ элемент логического порога является стандартным функциональным-- элементом, частным случаем которого считается маиюритарный элемент. Элемент логического порога а из Ъ имеет Ъ входов и один выход, и сигнал на его выходе равен 1 только в тех случаях, когда не менее а входных сигналов равны . Мажоритарный элемент имеет нечетное число входов с, его выходной сигнал равен 1 при поступлении на его входы М(с+1)/2 или большего числа, входных сигналов, равных 1, Элемент логического порога может быть выполнен на основе известных схем. Элемент 4 имеет 4 входа, если k, в остальных случаях число входов . Величина порога , число элементов 14 равно п. Значение порога определяется априорно с учетом известного.

Триггер 15 предназначен для управления работой счетчика 16. По заднему фронту импульса запуска ИНК 1 триггер 15 разрешает поступление сдвигающих импульсов на регистр 13р по сигналу счетчика 16 - запрещает. Счетчик 16 служит для подсчета числа сдвигающих.импульсов, поступающих на шину Сдвиг влево (Сдвиг вправо) в регистр 13.

Счетчик 16 (фиг. 5) содержит двоичный счетчик 47 и элемент И 48. По импульсу запуска ИНК 1, поступающему от элемента И 12, в счетчик 47 записывается дополнительный код числа разрядов выходного кода ПНК 1 п+1. По разрешающему управляющему сигналу от триггера 15 импульсы из блока 3 управления через элемент К 48, выполняющий функцию вентиля, поступают на регистр 13 и на счетчик ,47 импульсов. Счетчик 47 осуществляет подсчет сдвигающих импульсов и при прохождении п импульсов выдает сигнал на триггер 15. Последний возвращается в исходное состояние и запрещает поступление сдвигаюш 1х импульсов через элемент И 48. Счетчик 47 подобен счетчикам 40 и 44,

(О

логического логической

20

25

435516

Компаратор 18 предназначен для сравнения кода максимального значения флуктуационной помехи (ФП), оггределя- емого априорно, с выходньпч кодом 5 элементов 14 логического порога, 11с- ли значение выходного кода элементов 14 больше максимального значения ФП, то компаратор 18 выдает сигнал

О, в противном случае Элемент НЕ 19 служит инвертором. Первая группа 20 элементов И служит для подачи на вход сумматора 2 по разрешающему сигналу с элементов НЕ 19 и ИЛИ 24 через эле- 5 менты ИЛИ 22 выходного кода элементов 14 логического порога. Вторая группа 21 элементов И служит для подачи на вход сумматора 2 по разрешающему сигналу с компаратора 18 и третьего элемента И 23 через элементы ИЛИ 22 выходного кода. ПНК 1 , записанного в крайних правых (левых) разрядах регистра 13.

Блок 25 опред&пения уровня сигнала ..предназначен для выполнения в каждом цикле преобразования операций сравнения кода макодмального значения ФП с кодами (k+0 значений последовательных отсчетов, поступающих с ПНК 1, и выдачи соответствуюш:их управляюш 1х сигналов на элементы И 23 и ИЛИ 24. Если значение кода отсчета, поступающего с ПНК 1, меньше или равно максимальному значению

35 ФП, то компаратор 26 выдает на элемент И 29 сигнал логической 1, в противном случае - логического О Счетчик 27 служит для подсчета числа сравниваемых последовательных

40 отсчетов с ПНК 1.

Счетчик 27 (фиг. 6) содержит счетчик 49 и элемент И 50. По сигналу с блока 3 управления в старший разряд счетчика 49 записывается., а в

45 остальные - дополнительный код чис-- ла (k+2). Импульсы запуска ПНК 1 через элемент И 50, выполняющий функцию вентиля, поступают на счетный вход счетчика 49, При прохождении (k+2)

50 импульсов запуска ПНК 1 счетчик 27 обнуляется. При этом сигнал со старшего разряда счетчика запрещает поступление на него импульсов через элемент И 50, Этот же сигнал запре-

55 щаег выдачу результата сравнения с компаратора 26 на триггер 28 через элемент И 29 по заднему фронту импульса Конец преобразования (КП) ПНК 1 ,

30

7

Триггер 28 предназначен для выдачи управляющих сигналов на элемент И 23 и ИЛИ 24. Начальная установка триггера 28 выполняется по сигналу с БУ 3, при этом триггер разрешает прохождение сигналов через элемент И 23. Если хотя бы один из (k+1) сравниваемых отсчетов не больше максималного значения ФИ, то триггер 28 по сигналу КП перебрасывается и разрешает через элементы ИЛИ 24 съем информации с элементов 14 логического порога.

Сумматор-осреднитель 2 (фиг. 7) представляет собой сумматор накапливающего типа с цифровым мультиплексором на два канала на входе, позво- ляюпдам суммировать данные последовательно во времени от различных источников - регистров 13 и 6, и содержит элементы И 51, элементы ИЛИ 52, комбинационный сумматор 53, регистр 54 памяти, элементы ИЛИ 55. Блоки 51 и 52 образуют цифровой мультиплексор (п разрядов на 2 канала, где п - разрядность выходного кода ПНК 1, так как разрядность суммы из регистра 6 больше, чем п, то остальные элементы И 51 служат для подключения к сумматору 53 старших разрядов суммы), блоки 53 и 54 - накапливающий сумматор, блок 55 - цепь записи результата сложения из сумматора 53 в регистр 54 памяти. На вход комбинационного сумматора 53 поступают коды от элементов ИЛИ 22 или регистра 6 суммы в зависимости от управляющих сигналов с элемента И 12 и блока 3 управления. Запись результата сложения в регистр 54 памяти ocyD ecтвляeтcя по заднему фронту управляющих импульсов от блока 3 управления и элемента И 12. По сигналу от блока 3 управления, поступающему на третий вход сумматора 2, происходит обнуление регистра 54 памяти.

Устройство работает следующим образом.

По сигналу Пуск в реверсивный счетчик 9 записьшается код числа ос- редняемых отсчетов NJ, кратного степени два, соответствующий наиболее вероятному интервалу интегрирования, определяемому априорно по разбросу дисперсии флуктуационной помехи ij(t) В блоке 8 управления распределитель импульсов устанавливается в состояние, соответствующее последнему такту цикла его работы. После окончания

18

переходного процесса (одного цикла

,1

работы распределителя импульсов, в счетчик 9 записывается код числа К . , в счетчик 10 и счетчик 11 сдвигов записывается дополнительный код числа k+1, причем К. равно N или 2 ,, или l/2No, в счетчик 27 записывается дополнительный код числа (k+2), а

триггер 28 устанавливается в начальное состояние. Переходный процесс длительностью , где Т - время цикла работы распределителя импульсов, необходим для заполнения регистра 13 после включения устройства. При этом для того, чтобы переходный процесс укладывался в один цикл работы распределителя импульсов, необходимо условие Njj k.

Затем производится N.-кратное преобразование входного сигнала Uy+i(t) в преобразователе 1 по сигналам с блока 3 управления через элемент И 12,на второй вход которого поступает разрешающий потенциал со счетчика 10, задающего число преобразований. При этом может использоваться любой тип ПНК 1. Полученный в результате однократного преобразования код

в ПНК 1 импульсом конца преобразования записывается в сдвигающий регистр 13 (в его крайние п разрядов).

По переднему фронту импульса запуска ПНК 1, снимаемого с элемента И 12, происходит установка дополнительного кода числа п в счетчик 16 сдвигов. По заднему фронту импульса запуска ПНК 1 триггер 15 устанавливается в состояние 1 и разрещает через счетчик 16 прохождение импульсов с блока 3 управления на щину Сдвиг влево (Сдвиг вправо) в регистр 13.

Подсчет сдвигающих импульсов вы- полняется в счетчике 16, и при прохождении импульсов он возвращает триггер 15 в исходное состояние О. Триггер 15 запрещает поступление импульсов с блока 3 управления в ре- гистр 13. Период сдвигающих импульсов Т. выбирается из условия -t,,)n, где t - длительность импульса запуска ПНК 1. Информация в регистре 13 оказывается сдвинутой вле- во (вправо) на п разрядов. Так как измеряемый сигнал постоянен на двух сравниваемых интервалах цифрового интегрирования, то изменение выходного кода ПНК 1 на этих интервалах

91

возможно лишь за счет действия йшук туанионных и импульсных помех.

С помощью элементов 14 логического порога выполняется поразрядная обработка информации, записанной в 1, 1+п,...,l+2kn разрядах регистра 13. Элементами 14 устраняется действие импульсной помехи (ИП) высокого уровня и отличие кодов ПНК 1 на сравниваемых интервалах определяется действием ФП. Код с выхода элементов 14 поступает в цифровой компаратор 18, где сравнивается с кодом максимального значения ФП.

Если хотя бы один из обрабатывае- емых элементами 14 отсчетов сигнала искажен ИП высокого уровня и измеряемый сигнал превьша1ет возможный уровень ФП, то выходной код элементов 4 больше кода максимального значения ФП и компаратор 18 выдает сигнал логического О. Этот сигнал инвертируется элементом НЕ 19, проходит через элемент ИЛИ 24 и разрешает выдачу выходного кода элементов 14 в сум матор-осреднитель 2 через элементы И 20 и ШШ 22.

Если в текущий момент ИП отсутствует, то компаратор 18 выдает сигнал логической 1, который поступает на элемент И 23. Уровень измеряемого сигнала определяется с помощью блока 25, Наличие или отсутствие ИП высокого уровня в обрабатываемых отсчетах определяется с помощью компаратора 26, где выходной код ПНК 1 сравнивается с кодом максимального значения ФП, Если выходной код ППК 1 не превышает сравниваемого кода, то компаратора 26 выдает на элемент И 29 сигнал логической 1,

Счетчик 27 выполняет подсчет импульсов запуска ПНК 1 с начала каждого цикла работы устройства и разрешает прохождение сигналов через элемент И 29 только в течение первых (k+1)преобраэований. После прохождения (k+2) импульсов запуска ПНК 1 счетчик 27 обнуляется. В этом состоянии он не выполняет подсчет импульсов запуска. Если на элемент И 29 с блоков 26 и 27 поступают сигналы логической 1, то импульс КП проходит через элемент И 29, и по заднему фронту импульса триггер 28 устанавливается в состояние 1. С его единичного выхода через элемент ИЛИ 24 снимается сигнал, разрешаю

0

551

О

щий выдачу выходног о кода элементен 14 в сумматор-осреднитель 2 через элементы И 20 и ИЛИ 22, В нач;шьном состоянии триггер 28 разрепшет прохождение сигналов через элемент И 23 с компаратора 18.

Таким образом, если выходной код ППК 1 больше максимального значения

0 ФП, ИП отсутствует и выходной код элементов 14 не больше максимального значения ФП, то в cy мaтop-ocpeд- нитель 2 через элементы И 21 и ИЛИ 22 поступает выходной код ПНК 1 .

2 Коды, поступающие в сумматор-осреднитель 2 с элементов ИЛИ 22, суммируются с его содержимым по импульсам запуска ПНК 1

5

После N --кратного

преобразования счетчик 10 выдает сигнал в блок 3 управления, по которому начинает работать распределитель импульсов (РИ) блока 3 управления. На первом такте работы РИ код суммы из сумматора-осреднителя 2 считывается в регистр 6 суммы и регистр 5 . результата.

На втором такте РИ происходит установка содержимого сумматора-осреднителя 2 равным нулю, установка в счетчиках 10 и П дополнительного кода числа N.- , установка в счетчике 27 дополнительного кода числа (k+2), установка триггера 28, при этом распределитель -импульсов блока 3 управле ния временно прекращает свою работу. 5 Затем производится новое N,--кратное

ПНК

0

0

преобразование в ПНК 1, логическая обработка выходных кодов ПНК 1 в элементах 14 и суммирование кодов в сумматоре 2, После N- преобразований счетчик 10 вьщает сигнал в блок 3 управления, разрешая работу распределителя импульсов.

На третьем такте работы распределителя импульсов.из содержимого сумматора 2 вычитается код, записанный в регистр 6, разность кодов, равная

50

NI SZ L Ux+

i(tjj -. i: u,n(tj,

с учетом знака переписывается в регистр 4 ошибки на четвертом такте 55 работы распределителя импульсов. На пятом такте работы РИ из ВУ 3 на пшну Сдвиг вправо регистра 5 результата и регистра 4 ошибки через счетчик 11 сдвигов поступают импульсы. Подсчет сдвигаюи Д1х импульсов выполняется в счетчике 11, и при прохождении N импульсов счетчик 11 запрещает их поступление в регистры 5 и 4. Осредненньш результат из регистра 5 выдается на считывание, а из регистра 4 разность jZ/N. сравнивается в цифровых компараторах 8 и 7 с допустимым уровнем погрешности от помех Z. Выходы цифровых компараторов управляют прибавлением или эычитанием величины приращения числа осредняемых отсчетов из кода реверсивного счетчика 9 и выдачей с элемента И 17 сигнала, разрешающего считывание кода результата X с регистра 5.

Таким образом, изменение интервала интегрирования, определяемого кодом счетчика 9 на i-м шаге поиска, осуществляет ся на шестом такте работы распределителя импульсов блока 3 управления в соответствии с итерационной формулой.

Ni,,Ni+0N;

где N- N..+6No

e J

+ 1 |jZ/Nj-( -Л,0

- (jZ/NjI

О Z/NjUd, Если

d ldZ/NjUd,

то на шестом такте работы распределителя импульсов с выхода элемента И 17 снимается сигнал, разрешающий считывание кода с регистра. 5.

На.седьмом такте работы распределителя импульсов происходит запись дополнительного кода числа осредняемых отсчетов из счетчика 9 в счетчик 10 и счетчик 11 сдвигов, обнуление сумматора-осреднителя 2, запись в счетчик 27 дополнительного кода числа (k+2) и начальная установка триггера 28. Счетчик 10 вьщает сигнал в лок 3 управления и запрещает работу распределителя импульсов. Устройство оказьшается подготовленным для следующего цикла работы.

После нескольких шагов поиска (нескольких описанных циклов) в реверсивном счетчике 9 устанавливается некоторое значение N;, соответствующее значению допустимой погрешности и: С заданной доверительной ве

роятностью /ь, причем воздействие импульсных помех на погрешность преобразования исключается во всем динамическом диапазоне преобразователя напряжение-код.

В предлагаемом устройстве по сравнению с известным погрешность преобразования уменьшена на величину

kCR-U,-4(t)I ,

где R - значение выходного кода ПНК 1 при действии импульсной помехи, если число k отсчетов сигнала, искаженных Ш1, на первом из двух сравниваемых интервалов цифрового интегрирования равно числу отсчетов сигнала, искаженных Ш1, на втором интервале интегрирования.

Формула изобретения

1, Устройство аналого-цифрового преобразования, содержащее преобразователь напряжение-код, первый вход которого является шиной входного сигнала, второй вход объединен с первыми входами сумматора-осред0

нителя, триггера и первого счетчика

0

сдвигов и соединен с выходом первого элемента И, первая группа выходов - с первыми входами сдвигающего регистра соответственно, а второй выход- с вторым входом сдвигающего регистра,

5 третий вход которого соединен с первым выходом первого счетчика сдвигов,, второй выход которого соединен с вторым входом триггера, выход которого соединен с первым входом первого счетчика сдвигов, второй вход которого соединен с первым выходом блока управления, первый вход которого сое- динен с первым выходом счетчика, а второй вход является шиной Пуск и

45 объединен с первым управляющим входом реверсивного счетчика, второй управляющий вход которого объединен с первым входом второго элемента И к подключен к второму выходу бло50 ка управления, третий выход которого соединен с вторым входом сумматора- осреднителя, выходы которого соединены соответственно с первыми входами регистра результата, регистра 55 ошибки и регистра суммы, второй вход которого объединен с вторым входом регистра результата и соединен с четвертым выходом блока управления, а выход подключен к третьему входу

13

сумматора-осреднителя, выход регистра ошибки соединен с входами первого и второго цифровых компараторов, первые выходы которых соединены соот- ветствепно с вторым и третьим входами второго элемепта И, а вторые выходы - соответственпо с шипами Сложение и Вычитание реверсивного счетчика, выход которого соединен с первым входом счетчика и первым входом второго счетчика сдвигов, второй вход которого объединен с вторым входом счетчика и четвертым входом сумматора-осреднителя и соединен с пятым выходом блока управления, а выход с вторым входом регистра ошибки И третьим входом регистра результата, четвертый вход которого соединен с выходом второго элемента И, шестой выход блока управления соединен с третьим входом счетчика и первым входом первого элемента И, второй вход которого соединен с вторым выходом счетчика, седьмой выход блока управления соединен с третьим входом второго счетчика сдвигов, а восьмой выход - с третьим входом регистра ошибки, отличающееся тем, что, с целью расширения динамического диапазона измеряемого сигнала, в него введены элементы логического порога по числу разрядов выходного кода преобразователя напряжение-код, первая и вторая группы элементов И и группа элементов ИЛИ по числу элементов в группах, равному числу разрядов выходного кода преобразователя напряжение-код, третий цифровой компаратор, элемент НЕ, эле - мент ИЛИ, третий элемент И и блок, определения уровня сигнала, .первая группа входов которого соединена с первой группой выходов преобразователя напряжение-код, второй вход - с вторым выходом преобразователя напряжение-код, третий вход - с выходом первого элемента И, а четвертый вход- с пятым выходом блока управления.

.3551Ь .

выходы элемелтов .ко1-о юрога соединены с перными Р ходами соответствующих элементов И первой г руппы и входами третьег О цифрового компарато5 ра, выход KOTopoi o соединен с входом элемента НЕ и первым входом третьего элемента И, второй вход которого соединен с первым выходом блока определения уровня сигнала, а выход - с

JO первыми входами элементов И второй группы, вторые входы которых соединены с соответствующими выходами сдвигающего регистра; все выходы которого соединены с соответствующими вхо15 дами элементов логического порога, выход элемента НЕ соединен с первым входом элемента ИЛИ, второй вход которого соединен с вторым выходом блока определения уровня сигнала, а

20 выход - с вторыми входами элементов И первой группы, выходы которых соединены соответственно с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выходами

25 соответствующих элементов И второй группы, а выходы с пятой группой входов сумматора-осреднителя.

2. Устройство по п, 1, о т л и чающееся тем, что блок определения уровня сигнала выполнен на цифровом компараторе, счетчике, триггере и элементе И , первый вход которого является вторым входом бло

ка определения уровня сигнала, второй вход соединен с выходом цифрового компаратора, вход которого является первой группой входов блока, третьим входом которого является

первый вход счетчика, четвертым входом являются первый вход триггера и второй вход счетчика, выход которого соединен с третьим входом элемента И, выход которого соединен с вторым входом триггера; первый и второй выходы которого являются соответственно первым и вторым выходами блока определения уровня сигнала.

НоЗк ---

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1989 |

|

SU1647894A1 |

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

| Устройство аналого-цифрового преобразования | 1981 |

|

SU1012435A1 |

| Устройство аналого-цифрового преобразования | 1977 |

|

SU641646A1 |

| Устройство для измерения угла фазового сдвига гармонических сигналов | 1990 |

|

SU1765781A1 |

| Цифровой измеритель пикового значения импульсных воздействий | 1984 |

|

SU1167734A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| ПРЕОБРАЗОВАТЕЛЬ АКТИВНОЙ МОЩНОСТИ В ЦИФРОВОЙ КОД | 1967 |

|

SU223459A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

Изобретение относится к цифровой электроизмерительной технике и может использоваться в информационно-измерительных системах и системах автоматического управления, работаю- ПД1Х в условиях аддитивных случайных помех. Цель изобретения - растирение динамического диапазона измеряемого сигнала - достигается введением в известное устройство элементов логического порога по числу разрядов выходного кода преобразователя напря- , жение-код, двух групп элементов И и группы элементов ИЛИ по числу элементов в группах, равному числу разрядов выходного кода преобразователя напряжение-код, третьего цифрового компаратора, элемента НЕ, элемента ШШ, третьего элемента И и блока определения уровня сигнала, включающего в себя цифровой компаратор, счетчик, триггер и элемент И. При этом за счет введения логического порога при поразрядном логическом сравнении выходных кодов преобразователя напряжение-код исключается действие импульсных помех высокого уровня и сбоев преобразователя напряжение-код во всем динамическом диапазоне устройства. 1 з.п. ф-лы, 7 ил. i (Л СдЬ 00 ел сд

;ff2

А 5,5

25 К2 Kit

К// X,f7

г.2

Dm22 От6 ОтЪ От 12

Составитель В.Махнанов Редактор Н.Тупица ТехредМ.Дидык

Заказ 4836/56 Тираж 901Подписное

ВНИИПИ Государствеино о комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

к«,5,5

Фиг. 7

ОтЪ

Корректор И.Муска

| Устройство аналого-цифрового преобразования | 1977 |

|

SU641646A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Проектирование импульсных и цифровых устройств радиотехнических сие тем./Под ред | |||

| Ю.М.Казаринова | |||

| М.: Высшая школа, 1985, с | |||

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

Авторы

Даты

1987-10-07—Публикация

1986-04-14—Подача